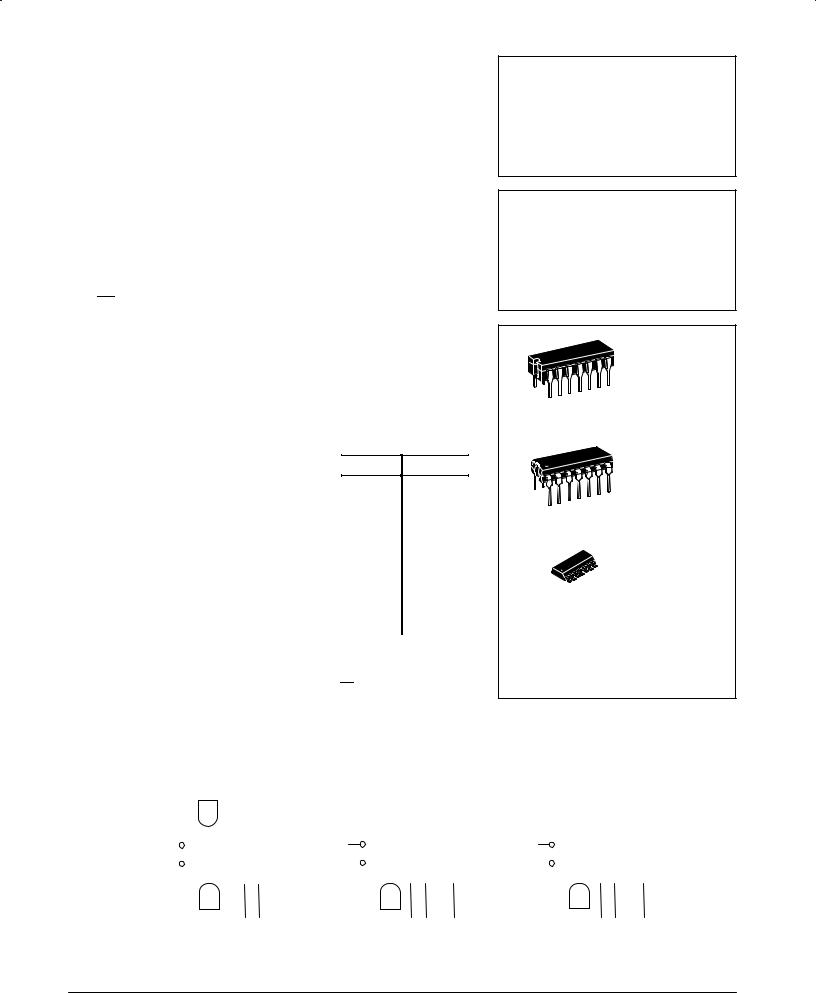

MOTOROLA SN54LS90, SN74LS90, SN54LS92, SN74LS92, SN54LS93 Technical data

...

74LS90

DECADE COUNTER; DIVIDE-BY-TWELVE COUNTER; 4-BIT BINARY COUNTER

The SN54/74LS90, SN54/74LS92 and SN54/74LS93 are high-speed 4-bit ripple type counters partitioned into two sections. Each counter has a di- vide-by-two section and either a divide-by-five (LS90), divide-by-six (LS92) or divide-by-eight (LS93) section which are triggered by a HIGH-to-LOW transition on the clock inputs. Each section can be used separately or tied together (Q to CP) to form BCD, bi-quinary, modulo-12, or modulo-16 counters. All of the counters have a 2-input gated Master Reset (Clear), and the LS90 also has a 2-input gated Master Set (Preset 9).

•Low Power Consumption . . . Typically 45 mW

•High Count Rates . . . Typically 42 MHz

•Choice of Counting Modes . . . BCD, Bi-Quinary, Divide-by-Twelve, Binary

•Input Clamp Diodes Limit High Speed Termination Effects

LOADING (Note a)

HIGH LOW

|

|

|

|

|

|

|

CP0 |

Clock (Active LOW going edge) Input to |

0.5 |

U.L. |

1.5 |

U.L. |

|

|

|

2 Section |

|

|

|

|

|

1 |

Clock (Active LOW going edge) Input to |

0.5 |

U.L. |

2.0 |

U.L. |

CP |

||||||

|

|

5 Section (LS90), 6 Section (LS92) |

|

|

|

|

|

1 |

Clock (Active LOW going edge) Input to |

0.5 |

U.L. |

1.0 |

U.L. |

CP |

||||||

|

|

8 Section (LS93) |

|

|

|

|

MR1, MR2 |

Master Reset (Clear) Inputs |

0.5 |

U.L. |

0.25 |

U.L. |

|

MS1, MS2 |

Master Set (Preset-9, LS90) Inputs |

0.5 |

U.L. |

0.25 |

U.L. |

|

Q0 |

Output from 2 Section (Notes b & c) |

10 |

U.L. |

5 (2.5) |

U.L. |

|

Q1, Q2, Q3 |

Outputs from 5 (LS90), 6 (LS92), |

10 |

U.L. |

5 (2.5) |

U.L. |

|

|

|

8 (LS93) Sections (Note b) |

|

|

|

|

NOTES:

a.1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b.The Output LOW drive factor is 2.5 U.L. for Military, (54) and 5 U.L. for commercial (74)

b.Temperature Ranges.

c.The Q0 Outputs are guaranteed to drive the full fan-out plus the CP1 input of the device.

d.To insure proper operation the rise (tr) and fall time (tf) of the clock must be less than 100 ns.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC SYMBOL |

|

|||||||||

|

|

|

|

|

|

|

|

LS90 |

|

|

|

|

|

|

|

|

|

|

LS92 |

|

|

|

|||

|

|

|

|

6 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MS |

|

|

|

|

|

|

14 |

|

|

CP0 |

|

|

|

|

|

|

|

|||

14 |

|

|

|

CP0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

1 |

|

|

|

CP |

|

|

|

|

|

|

|

|

1 |

|

|

CP1 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

MR Q0 Q1 Q2 Q3 |

|||||||||

|

|

|

|

|

MR Q0 Q1 Q2 Q3 |

|

|

|

|||||||||||||||||

|

|

|

|

1 |

2 |

|

|

|

|

|

|

|

1 |

2 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3 |

12 |

9 |

8 |

11 |

|

6 |

7 |

12 |

11 |

9 |

8 |

|||||||||

|

|

|

|

VCC = PIN 5 |

|

|

|

|

|

|

VCC = PIN 5 |

|

|

|

|||||||||||

|

|

|

|

GND = PIN 10 |

|

|

|

|

|

GND = PIN 10 |

|

|

|

||||||||||||

|

|

|

|

NC = PINS 4, 13 |

|

|

|

|

|

NC = PINS 2, 3, 4, 13 |

|||||||||||||||

SN54/74LS90

SN54/74LS92

SN54/74LS93

DECADE COUNTER;

DIVIDE-BY-TWELVE COUNTER; 4-BIT BINARY COUNTER

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 632-08 |

14 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

14 |

|

|

CASE 646-06 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

14 |

|

SOIC |

|

|

CASE 751A-02 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN54LSXXJ Ceramic

SN74LSXXN Plastic

SN74LSXXD SOIC

LS93

14 |

|

|

CP0 |

|

|

|

|

|

|

|

|

1 |

|

|

CP1 |

|

|

Q0 Q1 Q2 Q3 |

|||||

|

|

|

|

||||||||

|

|

|

MR |

||||||||

|

|

|

1 |

2 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3 |

12 |

9 |

8 |

11 |

|||

|

|

|

VCC = PIN 5 |

|

|

|

|||||

|

|

|

GND = PIN 10 |

|

|

|

|||||

|

|

|

NC = PIN 4, 6, 7, 13 |

||||||||

FAST AND LS TTL DATA

5-90

SN54/74LS90 •SN54/74LS92 •SN54/74LS93

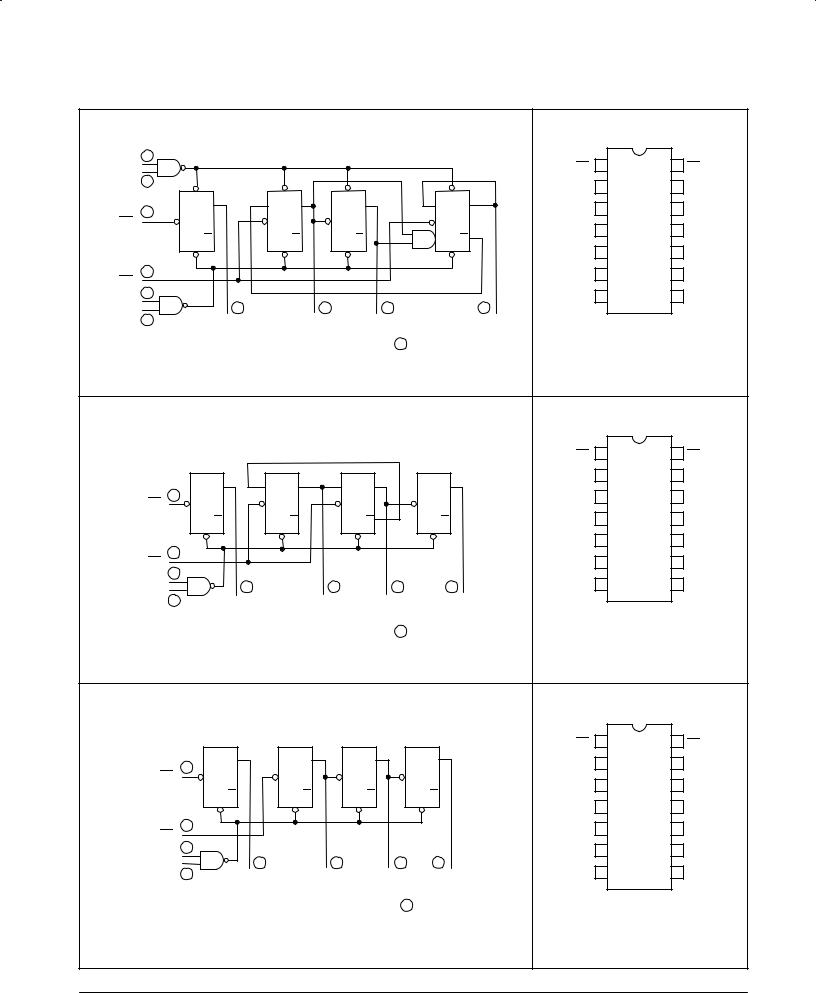

LOGIC DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONNECTION DIAGRAM |

||||||

|

|

|

|

|

|

|

|

|

LS90 |

|

|

|

|

|

|

|

|

|

DIP (TOP VIEW) |

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MS1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

14 CP |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CP |

|||||

MS2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

0 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

2 |

13 NC |

|||

|

|

J SD Q |

|

J SD Q |

J SD Q |

|

|

|

R SD Q |

|

1 |

|

|

|

|

|||||||

|

14 |

|

|

|

|

|

MR |

3 |

12 Q |

0 |

||||||||||||

CP0 |

|

CP |

|

|

|

CP |

|

CP |

|

|

|

|

|

CP |

|

2 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

NC |

4 |

11 Q3 |

|||||||||

|

|

K C |

|

Q |

|

K C |

Q |

K C |

|

Q |

|

|

|

S C Q |

|

|||||||

|

|

|

D |

|

|

|

D |

D |

|

|

|

|

D |

|

V |

5 |

10 GND |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

CP1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MS |

6 |

9 |

Q |

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

||

MR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MS |

7 |

8 |

Q |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

||

1 |

|

|

|

|

|

12 |

|

|

9 |

|

|

|

8 |

|

|

11 |

|

|

|

|

|

|

MR2 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Q0 |

|

|

Q1 |

|

|

|

Q2 |

|

|

|

Q3 |

NC = NO INTERNAL CONNECTION |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= PIN NUMBERS |

|

NOTE: |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = PIN 5 |

|

The Flatpak version has the same |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

GND = PIN 10 |

|

pinouts (Connection Diagram) as |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

|

|

||

LOGIC DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONNECTION DIAGRAM |

||||||

|

|

|

|

|

|

|

|

|

LS92 |

|

|

|

|

|

|

|

|

|

DIP (TOP VIEW) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CP |

1 |

14 CP |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

0 |

|

|

|

J |

|

Q |

|

J |

|

Q |

J |

|

|

Q |

J |

|

Q |

|

NC |

2 |

13 NC |

||

|

|

14 |

|

|

|

|

|

|

|

NC 3 |

12 Q0 |

|||||||||||

|

CP0 |

CP |

|

CP |

|

CP |

|

CP |

|

|||||||||||||

|

|

|

|

|

|

|||||||||||||||||

|

|

|

K |

|

Q |

|

K |

Q |

K |

CD |

Q |

K |

|

Q |

|

NC 4 |

11 Q |

1 |

||||

|

|

|

|

CD |

|

|

CD |

|

|

|

|

CD |

|

|

5 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

10 GND |

|||

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

|

CP1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

Q |

2 |

|||

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

MR1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

11 |

|

|

9 |

|

|

8 |

|

MR2 7 |

8 |

Q3 |

||||

|

MR2 |

7 |

|

|

|

Q0 |

|

|

Q1 |

|

|

|

Q2 |

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC = NO INTERNAL CONNECTION |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= PIN NUMBERS |

|

NOTE: |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = PIN 5 |

|

The Flatpak version has the same |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

GND = PIN 10 |

|

pinouts (Connection Diagram) as |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

|

|

||

LOGIC DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONNECTION DIAGRAM |

||||||

|

|

|

|

|

|

|

|

|

LS93 |

|

|

|

|

|

|

|

|

|

DIP (TOP VIEW) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CP |

1 |

14 CP |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

0 |

|

|

14 |

|

|

J Q |

|

J |

Q |

J Q |

J |

|

Q |

|

MR |

2 |

13 NC |

||||||

|

CP0 |

|

|

CP |

|

|

CP |

CP |

|

CP |

|

|

|

1 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

MR |

3 |

12 Q |

0 |

||||||||||

|

|

|

|

|

K C |

Q |

|

K C Q |

K C |

Q |

K C |

|

Q |

|

2 |

|

|

|

||||

|

|

|

|

|

D |

|

|

D |

|

|

D |

D |

|

|

NC |

4 |

11 Q3 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

5 |

10 GND |

||

|

CP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

||

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC 6 |

9 |

Q1 |

||

|

MR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

1 |

|

|

|

12 |

|

|

|

9 |

|

|

8 |

|

|

11 |

|

|

|

|

|

|

|

MR2 3 |

|

|

|

|

|

|

|

|

|

|

|

NC 7 |

8 Q2 |

||||||||

|

|

|

|

Q0 |

|

|

Q1 |

|

|

|

Q2 |

|

|

Q3 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= PIN NUMBERS |

|

NC = NO INTERNAL CONNECTION |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = PIN 5 |

|

NOTE: |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

GND = PIN 10 |

|

The Flatpak version has the same |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

pinouts (Connection Diagram) as |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

|

|

||

FAST AND LS TTL DATA

5-91

Loading...

Loading...