MOTOROLA SN74LS259D, SN74LS259DR2, SN74LS259M, SN74LS259MEL, SN74LS259ML1 Datasheet

...

SN74LS259

8-Bit Addressable Latch

The SN74LS259 is a high-speed 8-Bit Addressable Latch designed for general purpose storage applications in digital systems. It is a multifunctional device capable of storing single line data in eight addressable latches, and also a 1-of-8 decoder and demultiplexer with active HIGH outputs. The device also incorporates an active LOW common Clear for resetting all latches, as well as, an active LOW Enable.

•Serial-to-Parallel Conversion

•Eight Bits of Storage With Output of Each Bit Available

•Random (Addressable) Data Entry

•Active High Demultiplexing or Decoding Capability

•Easily Expandable

•Common Clear

GUARANTEED OPERATING RANGES

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

VCC |

Supply Voltage |

4.75 |

5.0 |

5.25 |

V |

TA |

Operating Ambient |

0 |

25 |

70 |

°C |

|

Temperature Range |

|

|

|

|

|

|

|

|

|

|

IOH |

Output Current ± High |

|

|

± 0.4 |

mA |

IOL |

Output Current ± Low |

|

|

8.0 |

mA |

http://onsemi.com

LOW

POWER

SCHOTTKY

16

1

PLASTIC

N SUFFIX

CASE 648

16

1

SOIC

D SUFFIX

CASE 751B

ORDERING INFORMATION

Device |

Package |

Shipping |

|

|

|

SN74LS259N |

16 Pin DIP |

2000 Units/Box |

|

|

|

SN74LS259D |

16 Pin |

2500/Tape & Reel |

|

|

|

Semiconductor Components Industries, LLC, 1999 |

1 |

Publication Order Number: |

December, 1999 ± Rev. 6 |

|

SN74LS259/D |

SN74LS259

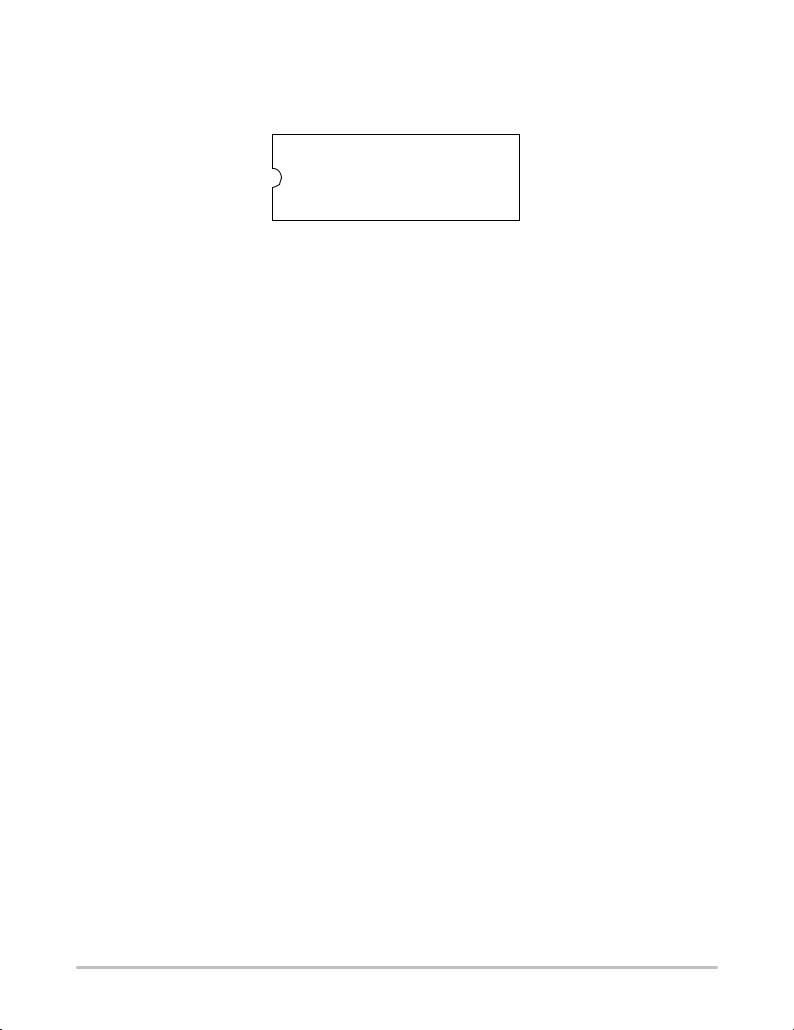

CONNECTION DIAGRAM DIP (TOP VIEW)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

C |

|

E |

|

D |

|

Q7 |

|

Q6 |

|

Q5 |

|

Q4 |

|||

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

||||

|

1 |

|

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

|

7 |

|

8 |

|

|

|

||

|

|

|

Ao |

|

|

A1 |

A2 |

|

Q0 |

Q1 |

Q2 |

|

Q3 |

GND |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOADING (Note a) |

|||||

PIN NAMES |

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH |

|

LOW |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

A0, A1, A2 |

Address Inputs |

|

|

|

|

|

|

|

|

0.5 U.L. |

|

0.25 U.L. |

||||||||||

D |

Data Input |

|

|

|

|

|

|

|

|

|

0.5 U.L. |

|

0.25 U.L. |

|||||||||

|

|

|

|

Enable (Active LOW) Input |

|

|

|

|

|

1.0 U.L. |

|

0.5 U.L. |

||||||||||

E |

|

|

|

|

||||||||||||||||||

C |

|

|

Clear (Active LOW) Input |

|

|

|

|

|

0.5 U.L. |

|

0.25 U.L. |

|||||||||||

Q0 ± Q7 |

Parallel Latch Outputs |

|

|

|

|

|

10 U.L. |

|

5 U.L. |

|||||||||||||

|

|

|

|

|

||||||||||||||||||

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

http://onsemi.com

2

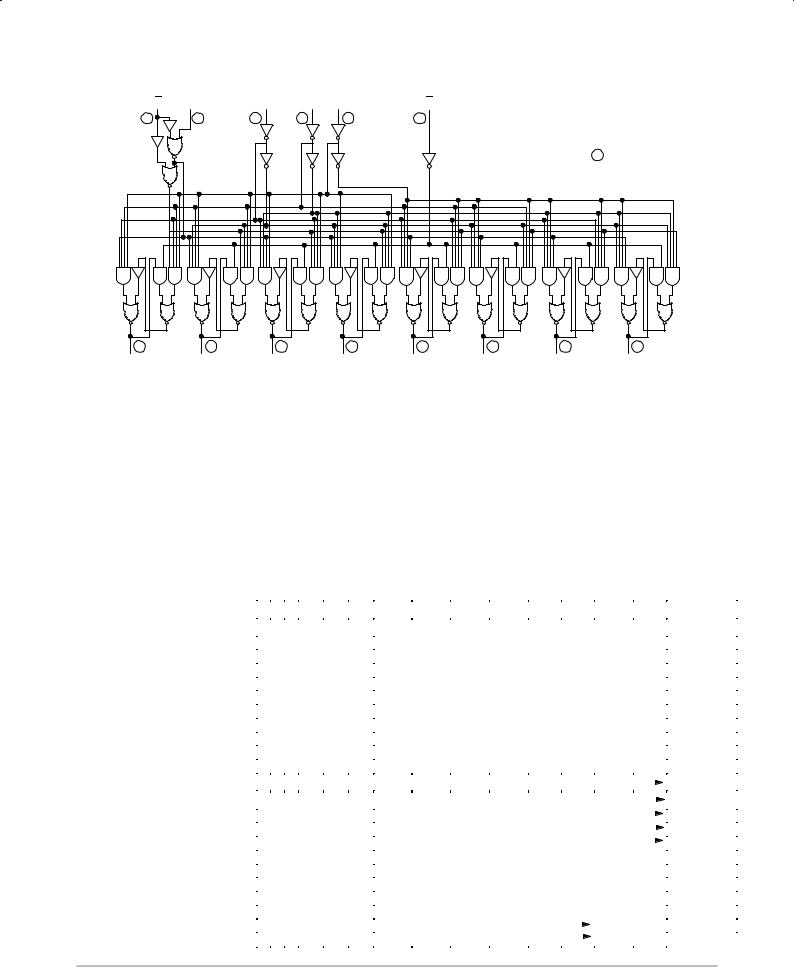

SN74LS259

LOGIC DIAGRAM

E |

D |

A0 |

A1 |

A2 |

C |

14 |

13 |

1 |

2 |

3 |

15 |

|

|

|

|

|

VCC = PIN 16 |

|

|

|

|

|

GND = PIN 8 |

|

|

|

|

|

= PIN NUMBERS |

4 |

Q0

5 |

6 |

7 |

Q1 |

Q2 |

Q3 |

9 |

Q4 |

10 |

Q5 |

11 |

12 |

Q6 |

Q7 |

FUNCTIONAL DESCRIPTION

The SN74LS259 has four modes of operation as shown in the mode selection table. In the addressable latch mode, data on the Data line (D) is written into the addressed latch.The addressed latch will follow the data input with all non-addressed latches remaining in their previous states. In the memory mode, all latches remain in their previous state and are unaffected by the Data or Address inputs.

In the one-of-eight decoding or demultiplexing mode, the addressed output will follow the state of the D input with all

MODE SELECTION

other inputs in the LOW state. In the clear mode all outputs are LOW and unaffected by the address and data inputs.

When operating the SN74LS259 as an addressable latch, changing more then one bit of the address could impose a transient wrong address. Therefore, this should only be done while in the memory mode.

The truth table below summarizes the operations.

TRUTH TABLE

PRESENT OUTPUT STATES

|

|

|

|

|

|

|

E |

|

C |

MODE |

|||

|

|

|

|

|

|

|

|

L |

H |

Addressable Latch |

|||

H |

H |

Memory |

||||

|

L |

|

L |

Active HIGH Eight-Channel |

||

|

|

|

|

|

|

Demultiplexer |

H |

|

L |

Clear |

|||

|

|

|

|

|

|

|

X = Don't Care Condition

L = LOW Voltage Level

H = HIGH Voltage Level

QN±1 = Previous Output State

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C E D A0 |

A1 |

A2 |

Q0 |

|

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

|

|

MODE |

||||||

|

L |

H |

X |

X |

X |

X |

L |

|

L |

L |

L |

L |

L |

L |

L |

|

|

Clear |

|||

|

L |

|

L |

L |

L |

L |

L |

L |

|

L |

L |

L |

L |

L |

L |

L |

|

|

Demultiplex |

||

|

L |

|

L H L |

L |

L |

H |

|

L |

L |

L |

L |

L |

L |

L |

|

|

|

||||

|

L |

|

L L H |

L |

L |

L |

|

L |

L |

L |

L |

L |

L |

L |

|

|

|

||||

|

L |

|

L H H L |

L |

L |

|

H |

L |

L |

L |

L |

L |

L |

|

|

|

|||||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

L |

|

L H H H H |

L |

|

L |

L |

L |

L |

L |

L |

H |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

H H X |

X |

X |

X |

QN±1 |

|

|

|

|

|

|

|

|

|

|

Memory |

|||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

H |

|

I |

I |

L |

L |

L |

L |

QN±1 |

QN±1 |

QN±1 |

|

|

|

|

|

|

Addressable |

|||

|

|

|

|

|

|

||||||||||||||||

|

H |

|

L |

H |

L |

L |

L |

H |

QN±1 |

QN±1 |

|

|

|

|

|

|

|

Latch |

|||

|

|

|

|

|

|

|

|||||||||||||||

|

H |

|

L |

L |

H |

L |

L |

QN±1 |

|

L |

QN±1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

H |

|

L H |

H |

L |

L |

QN±1 |

|

H |

QN±1 |

|

|

|

|

|

|

|

|

|||

|

|

• |

|

|

|

|

|

|

|

||||||||||||

|

• • |

• |

|

• |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

• • |

• |

|

• |

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|||

|

H |

|

L |

L |

H |

H |

H |

QN±1 |

|

|

|

|

|

|

|

QN±1 |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

H |

|

L H |

H |

H |

H |

QN±1 |

|

|

|

|

|

|

QN±1 |

H |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||||||||||

http://onsemi.com

3

Loading...

Loading...