MOTOROLA SN74LS42DR2, SN74LS42M, SN74LS42MEL, SN74LS42ML1, SN74LS42ML2 Datasheet

...

SN74LS42

One-of-Ten Decoder

The LSTTL / MSI SN74LS42 is a Multipurpose Decoder designed to accept four BCD inputs and provide ten mutually exclusive outputs. The LS42 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all ON Semiconductor

TTL families. |

http://onsemi.com |

|

• Multifunction Capability |

||

|

||

• Mutually Exclusive Outputs |

|

|

• Demultiplexing Capability |

LOW |

|

• Input Clamp Diodes Limit High Speed Termination Effects |

POWER |

|

|

SCHOTTKY |

|

|

|

GUARANTEED OPERATING RANGES

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

VCC |

Supply Voltage |

4.75 |

5.0 |

5.25 |

V |

TA |

Operating Ambient |

0 |

25 |

70 |

°C |

|

Temperature Range |

|

|

|

|

|

|

|

|

|

|

IOH |

Output Current ± High |

|

|

± 0.4 |

mA |

IOL |

Output Current ± Low |

|

|

8.0 |

mA |

16

1

PLASTIC

N SUFFIX

CASE 648

16

1

SOIC

D SUFFIX

CASE 751B

ORDERING INFORMATION

Device |

Package |

Shipping |

|

|

|

SN74LS42N |

16 Pin DIP |

2000 Units/Box |

|

|

|

SN74LS42D |

16 Pin |

2500/Tape & Reel |

|

|

|

Semiconductor Components Industries, LLC, 1999 |

1 |

Publication Order Number: |

December, 1999 ± Rev. 6 |

|

SN74LS42/D |

SN74LS42

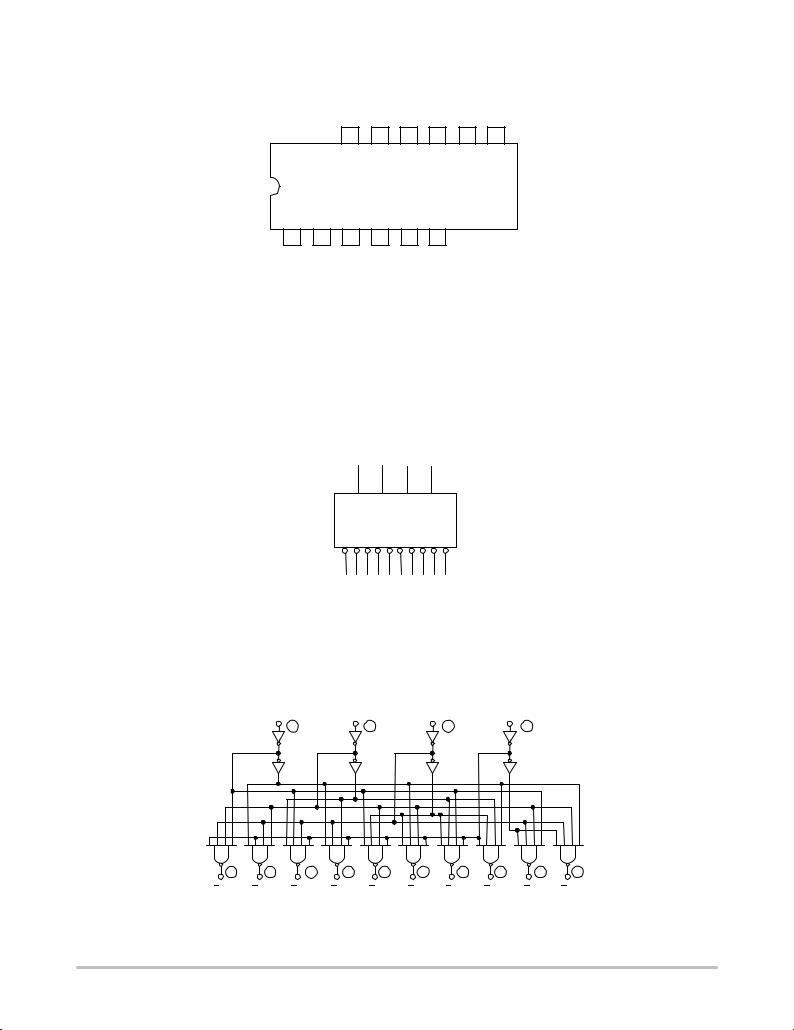

CONNECTION DIAGRAM DIP (TOP VIEW)

VCC |

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

A1 |

A2 |

A3 |

|

9 |

|

|

8 |

|

|

7 |

|

||||||||||||||

16 |

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The Flatpak version |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

has the same pinouts |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Connection Diagram) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

as the Dual In-Line |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Package. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

3 |

|

4 |

|

5 |

|

6 |

7 |

|

8 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

||||

0 |

1 |

2 |

3 |

4 |

5 |

|

6 |

|

||||||||||||||||||

|

|

|

|

|

LOADING (Note a) |

|

PIN NAMES |

|

HIGH |

LOW |

|||

A0 ± A3 |

Address Inputs |

0.5 U.L. |

0.25 U.L. |

|||

|

to |

|

|

Outputs, Active LOW |

10 U.L. |

5 U.L. |

0 |

9 |

|||||

|

|

|

|

|

|

|

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

LOGIC SYMBOL

15 14 13 12

A0 A1 A2 A3

0 1 2 3 4 5 6 7 8 9

1 2 3 4 5 6 7 9 10 11

VCC = PIN 16

GND = PIN 8

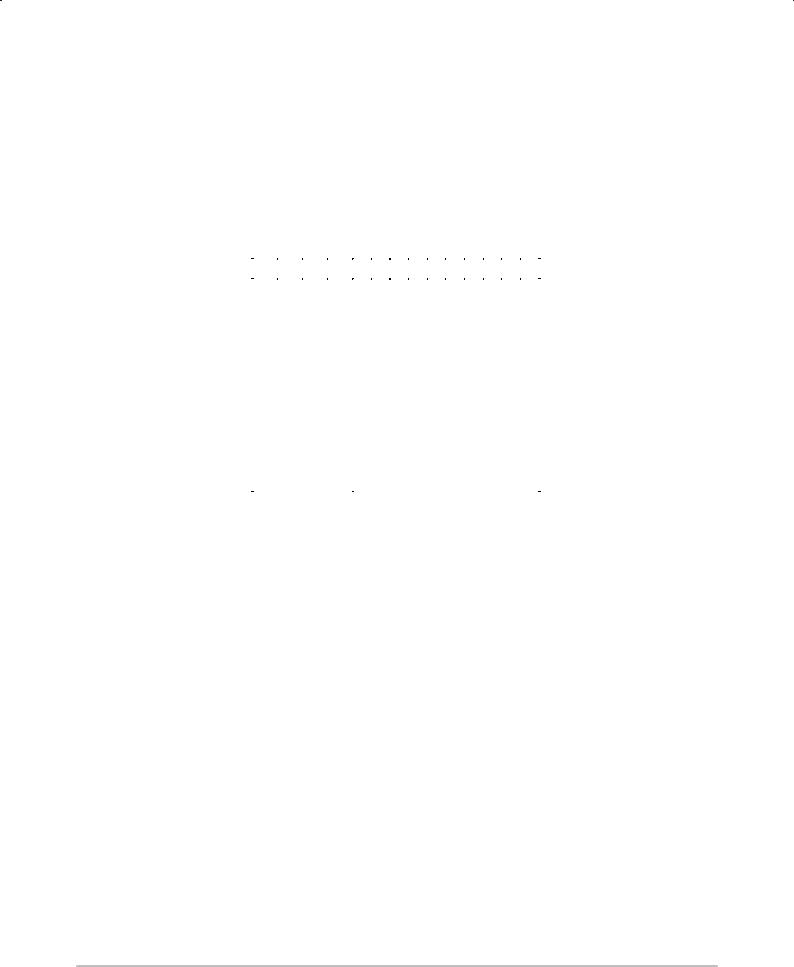

LOGIC DIAGRAM

A0 |

A1 |

A2 |

|

A3 |

15 |

|

14 |

13 |

12 |

|

1 |

2 |

3 |

4 |

5 |

|

6 |

7 |

9 |

10 |

11 |

0 |

1 |

2 |

3 |

|

4 |

5 |

6 |

|

7 |

8 |

9 |

VCC = PIN 16

GND = PIN 8

= PIN NUMBERS

= PIN NUMBERS

http://onsemi.com

2

SN74LS42

FUNCTIONAL DESCRIPTION

The LS42 decoder accepts four active HIGH BCD inputs and provides ten mutually exclusive active LOW outputs, as shown by logic symbol or diagram. The active LOW outputs facilitate addressing other MSI units with LOW input enables.

The logic design of the LS42 ensures that all outputs are HIGH when binary codes greater than nine are applied to the inputs.

The most significant input A3 produces a useful inhibit function when the LS42 is used as a one-of-eight decoder. The A3 input can also be used as the Data input in an 8-output demultiplexer application.

TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

A1 A2 A3 |

0 1 2 3 4 5 6 7 8 9 |

||||||||||||||||||||

L |

L L L |

L H |

H H H H H H H H |

|||||||||||||||||||

H L L L |

H L H |

H H H H H H H |

||||||||||||||||||||

L |

H L L |

H H L H |

H H H H H H |

|||||||||||||||||||

H H L L |

H H H L H |

H H H H H |

||||||||||||||||||||

L |

L H L |

H H H H L H |

H H H H |

|||||||||||||||||||

H L H L |

H H H H H L H |

H H H |

||||||||||||||||||||

L |

H H L |

H H H H H H L H |

H H |

|||||||||||||||||||

H H H L |

H H H H H H H L H |

H |

||||||||||||||||||||

L |

L L H |

H H H H H H H H L H |

||||||||||||||||||||

H L L H |

H H H H H H H H H L |

|||||||||||||||||||||

L |

H L H |

H H H H H H H H H H |

||||||||||||||||||||

H H L H |

H H H H H H H H H H |

|||||||||||||||||||||

L |

L H H |

H H H H H H H H H H |

||||||||||||||||||||

H L H H |

H H H H H H H H H H |

|||||||||||||||||||||

L |

H H H |

H H H H H H H H H H |

||||||||||||||||||||

H H H H |

H H H H H H H H H H |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H = HIGH Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L = LOW Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

http://onsemi.com

3

Loading...

Loading...