Motorola SN54LS395J, SN74LS395D, SN74LS395N Datasheet

4-BIT SHIFT REGISTER WITH 3-STATE OUTPUTS

The SN74LS395 is a 4-Bit Register with 3-state outputs and can operate in either a synchronous parallel load or a serial shift-right mode, as determined by the Select input. An asynchronous active LOW Master Reset (MR) input overrides the synchronous operations and clears the register. An active HIGH Output Enable (OE) input controls the 3-state output buffers, but does not interfere with the other operations. The fourth stage also has a conventional output for linking purposes in multi-stage serial operations.

•Shift Left or Parallel 4-Bit Register

•3-State Outputs

•Input Clamp Diodes Limit High-Speed Termination Effects

CONNECTION DIAGRAM DIP (TOP VIEW)

|

VCC |

O0 |

O1 |

|

O2 |

|

O3 |

|

Q3 |

|

CP |

|

OE |

|||

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

|

DS |

|

P0 |

|

P1 |

|

P2 |

P3 |

|

S |

|

GND |

||

|

PIN NAMES |

|

LOADING (Note a) |

||||

|

|

|

|

HIGH |

LOW |

||

|

|

Parallel Inputs |

|

|

|

|

|

|

P0 ± P3 |

0.5 |

U.L. |

0.25 |

U.L. |

||

|

DS |

Serial Data Input |

0.5 |

U.L. |

0.25 |

U.L. |

|

|

S |

|

Mode Select Input |

0.5 |

U.L. |

0.25 |

U.L. |

|

CP |

Clock (Active LOW) Input |

0.5 |

U.L. |

0.25 |

U.L. |

|

|

MR |

Master Reset (Active LOW) Input |

0.5 |

U.L. |

0.25 |

U.L. |

|

|

OE |

Output Enable (Active HIGH) Input |

0.5 |

U.L. |

0.25 |

U.L. |

|

|

3-State Register Outputs |

65 |

U.L. |

15 |

U.L. |

||

|

O0 ± O3 |

||||||

|

Register Output |

10 |

U.L. |

5 |

U.L. |

||

|

Q3 |

||||||

|

|

|

|

|

|

||

NOTES: |

|

|

|

|

|

||

a) 1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW. |

|

|

|

|

|||

SN74LS395

4-BIT SHIFT REGISTER WITH 3-STATE OUTPUTS

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 620-09 |

16 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

16 |

|

|

CASE 648-08 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

16 |

|

SOIC |

|

|

CASE 751B-03 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN74LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

LOGIC SYMBOL

7 3 4 5 6

S P0 P1 P2 P3

2DS

10 |

|

CP |

Q3 |

|

11 |

|

|

9  OE

OE

MR O0 O1 O2 O3

1 15 14 13 12

VCC = PIN 16

GND = PIN 8

FAST AND LS TTL DATA

5-551

SN74LS395

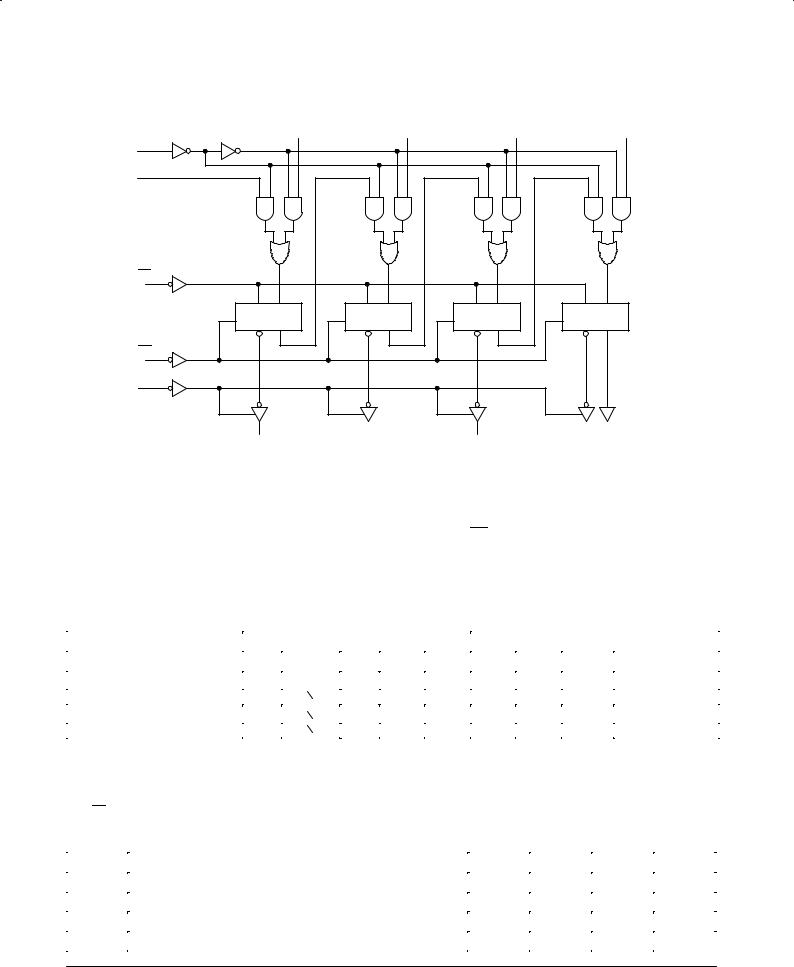

LOGIC DIAGRAM

S |

P0 |

|

P1 |

|

P2 |

|

P3 |

Ds |

|

|

|

|

|

|

|

CP |

|

|

|

|

|

|

|

CP |

D |

CP |

D |

CP |

D |

CP |

D |

CD |

Q |

CD |

Q |

CD |

Q |

CD |

Q |

|

|

|

|

||||

MR |

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

O0 |

|

O1 |

|

FUNCTION DESCRIPTION

The SN74LS395 contains four D-type edge-triggered flip-flops and auxiliary gating to select a D input either from a Parallel (Pn) input or from the preceding stage. When the Select input is HIGH, the Pn inputs are enabled. A LOW signal on the S input enables the serial inputs for shift-right operations, as indicated in the Truth Table.

State changes are initiated by HIGH-to-LOW transitions on the Clock Pulse (CP) input. Signals on the Pn, Ds and S inputs can change when the Clock is in either state, provided that the recommended set-up and hold times are observed. When the

O2 |

|

O3 |

|

Q3 |

|

|

S input is LOW, a CP HIGH-LOW transition transfers data in Q0 to Q1, Q1 to Q2, and Q2 to Q3. A left-shift is accomplished by connecting the outputs back to the Pn inputs, but offset one place to the left, i.e., O3 to P2, O2 to P1 and O1 to P0, with P3 acting as the linking input from another package.

When the OE input is HIGH, the output buffers are disabled and the Q0 ±Q3 outputs are in a high impedance condition. The shifting, parallel loading or resetting operations can still be accomplished, however.

MODE SELECT Ð TRUTH TABLE

|

|

|

|

|

|

|

Inputs @ tn |

|

|

|

|

Outputs @ tn+1 |

|

||||

Operating Mode |

MR |

|

CP |

|

S |

|

Ds |

Pn |

O0 |

O1 |

|

O2 |

|

O3 |

|||

Asynchronous Reset |

|

L |

|

X |

|

X |

|

X |

X |

L |

L |

|

L |

|

L |

||

Shift, SET First Stage |

|

H |

|

|

|

|

|

L |

|

H |

X |

H |

O0n |

|

O1n |

|

O2n |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

Shift, RESET First Stage |

|

H |

|

|

|

|

|

L |

|

L |

X |

L |

O0n |

|

O1n |

|

O2n |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

Parallel Load |

|

H |

|

|

|

|

|

H |

|

X |

Pn |

P0 |

P1 |

|

P2 |

|

P3 |

|

|

|

|

|

|

|

|

|

|||||||||

H = HIGH Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L = LOW Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X = Immaterial |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tn, n + 1 = time before and after CP HIGH-to-LOW transition

NOTE:

When OE is HIGH, outputs O0 ± O3 are in the high impedance state; however, this does not affect other operations or the Q3 output.

GUARANTEED OPERATING RANGES

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

VCC |

Supply Voltage |

4.75 |

5.0 |

5.25 |

V |

TA |

Operating Ambient Temperature Range |

0 |

25 |

70 |

°C |

IOH |

Output Current Ð High |

|

|

± 0.4 |

mA |

IOL |

Output Current Ð Low |

|

|

8.0 |

mA |

FAST AND LS TTL DATA

5-552

Loading...

Loading...