MOTOROLA SN74LS164M, SN74LS164MEL, SN74LS164ML1, SN74LS164ML2, SN74LS164MR1 Datasheet

...

SN74LS164

Serial-In Parallel-Out

Shift Register

The SN74LS164 is a high speed 8-Bit Serial-In Parallel-Out Shift Register. Serial data is entered through a 2-Input AND gate synchronous with the LOW to HIGH transition of the clock. The device features an asynchronous Master Reset which clears the register setting all outputs LOW independent of the clock. It utilizes the Schottky diode clamped process to achieve high speeds and is fully compatible with all ON Semiconductor TTL products.

•Typical Shift Frequency of 35 MHz

•Asynchronous Master Reset

•Gated Serial Data Input

•Fully Synchronous Data Transfers

•Input Clamp Diodes Limit High Speed Termination Effects

•ESD > 3500 Volts

GUARANTEED OPERATING RANGES

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

VCC |

Supply Voltage |

4.75 |

5.0 |

5.25 |

V |

TA |

Operating Ambient |

0 |

25 |

70 |

°C |

|

Temperature Range |

|

|

|

|

|

|

|

|

|

|

IOH |

Output Current ± High |

|

|

± 0.4 |

mA |

IOL |

Output Current ± Low |

|

|

8.0 |

mA |

http://onsemi.com

LOW

POWER

SCHOTTKY

14

1

PLASTIC

N SUFFIX

CASE 646

14

1

SOIC

D SUFFIX

CASE 751A

ORDERING INFORMATION

Device |

Package |

Shipping |

|

|

|

SN74LS164N |

14 Pin DIP |

2000 Units/Box |

|

|

|

SN74LS164D |

14 Pin |

2500/Tape & Reel |

|

|

|

Semiconductor Components Industries, LLC, 1999 |

1 |

Publication Order Number: |

December, 1999 ± Rev. 6 |

|

SN74LS164/D |

SN74LS164

CONNECTION DIAGRAM DIP (TOP VIEW)

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Q7 |

|

Q6 |

|

Q5 |

|

Q4 |

|

MR CP |

|

|

|

|||||||

|

|

14 |

|

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The Flatpak version has the same |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

pinouts (Connection Diagram) as |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

|

|

|

|

|

|

A |

B |

|

Q0 |

|

Q1 |

|

Q2 |

|

Q3 |

|

GND |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOADING (Note a) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN NAMES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH |

|

LOW |

|

||

A, B |

Data Inputs |

|

|

|

|

|

|

|

|

|

|

0.5 U.L. |

|

0.25 U.L. |

||||||

CP |

Clock (Active HIGH Going Edge) Input |

|

|

|

0.5 U.L. |

|

0.25 U.L. |

|||||||||||||

|

|

Master Reset (Active LOW) Input |

|

|

|

0.5 U.L. |

|

0.25 U.L. |

||||||||||||

MR |

|

|

||||||||||||||||||

Q0 ± Q7 |

Outputs |

|

|

|

|

|

|

|

|

|

|

|

10 U.L. |

|

5 U.L. |

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

|

|

LOGIC SYMBOL |

1 |

A |

LS164 |

2 |

B |

8-BIT SHIFT REGISTER |

8 |

CP |

|

MR Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

9 3 4 5 6 10 11 12 13

VCC = PIN 14

GND = PIN 7

http://onsemi.com

2

SN74LS164

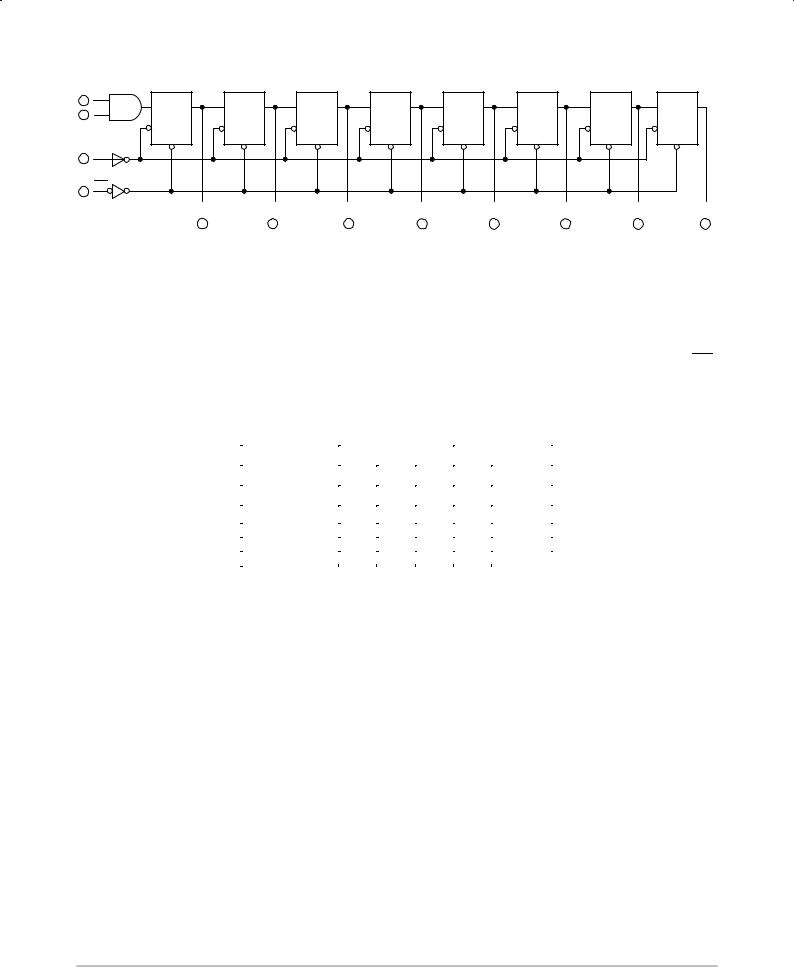

LOGIC DIAGRAM

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

Q |

D |

Q |

D |

Q |

D |

Q |

D |

Q |

D |

Q |

D |

Q |

D |

Q |

D |

|||||||||||||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CD |

|

CD |

|

CD |

|

CD |

|

CD |

|

CD |

|

CD |

|

CD |

8 CP

MR |

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

VCC = PIN 14 |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

3 |

4 |

5 |

6 |

10 |

11 |

12 |

13 |

GND = PIN 7

= PIN NUMBERS

= PIN NUMBERS

FUNCTIONAL DESCRIPTION

The LS164 is an edge-triggered 8-bit shift register with serial data entry and an output from each of the eight stages. Data is entered serially through one of two inputs (A or B); either of these inputs can be used as an active HIGH Enable for data entry through the other input. An unused input must be tied HIGH, or both inputs connected together.

Each LOW-to-HIGH transition on the Clock (CP) input

shifts data one place to the right and enters into Q0 the logical AND of the two data inputs (A•B) that existed before the

rising clock edge. A LOW level on the Master Reset (MR) input overrides all other inputs and clears the register asynchronously, forcing all Q outputs LOW.

MODE SELECT Ð TRUTH TABLE

OPERATING |

|

|

|

INPUTS |

|

OUTPUTS |

|

MODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

A |

B |

Q0 |

Q1±Q7 |

||

|

|

||||||

Reset (Clear) |

|

L |

X |

X |

L |

L ± L |

|

|

|

|

|

|

|

|

|

|

|

H |

I |

I |

L |

q0 ± q6 |

|

Shift |

|

H |

I |

h |

L |

q0 ± q6 |

|

|

|

H |

h |

I |

L |

q0 ± q6 |

|

|

|

H |

h |

h |

H |

q0 ± q6 |

|

L (l) = LOW Voltage Levels

H (h) = HIGH Voltage Levels X = Don't Care

qn = Lower case letters indicate the state of the referenced input or output one set-up time prior to the LOW to HIGH clock transition.

http://onsemi.com

3

Loading...

Loading...