Motorola SN54LS641J, SN54LS642J, SN54LS645J, SN54LS640J, SN74LS645N Datasheet

...

OCTAL BUS TRANSCEIVERS

These octal bus transceivers are designed for asynchronous two-way communication between data buses. Control function implementation minimizes external timing requirements. These circuits allow data transmission from the A bus to B or from the B bus to A bus depending upon the logic level of the direction control (DIR) input. Enable input (G) can disable the device so that the buses are effectively isolated.

DEVICE |

OUTPUT |

LOGIC |

LS640 |

3-State |

Inverting |

LS641 |

Open-Collector |

True |

LS642 |

Open-Collector |

Inverting |

LS645 |

3-State |

True |

FUNCTION TABLE

CONTROL |

|

|

OPERATION |

|||

|

INPUTS |

|

|

|

|

|

|

|

LS640 |

|

LS641 |

||

|

|

|

|

|

||

G |

|

DIR |

|

LS642 |

|

LS645 |

|

|

|

|

|

|

|

L |

|

L |

B data to A bus |

|

B data to A bus |

|

|

|

|

|

|

|

|

L |

|

H |

A data to B bus |

|

A data to B bus |

|

|

|

|

|

|

|

|

H |

|

X |

|

Isolation |

|

Isolation |

|

|

|

|

|

|

|

H = HIGH Level, L = LOW Level, X = Irrelevant

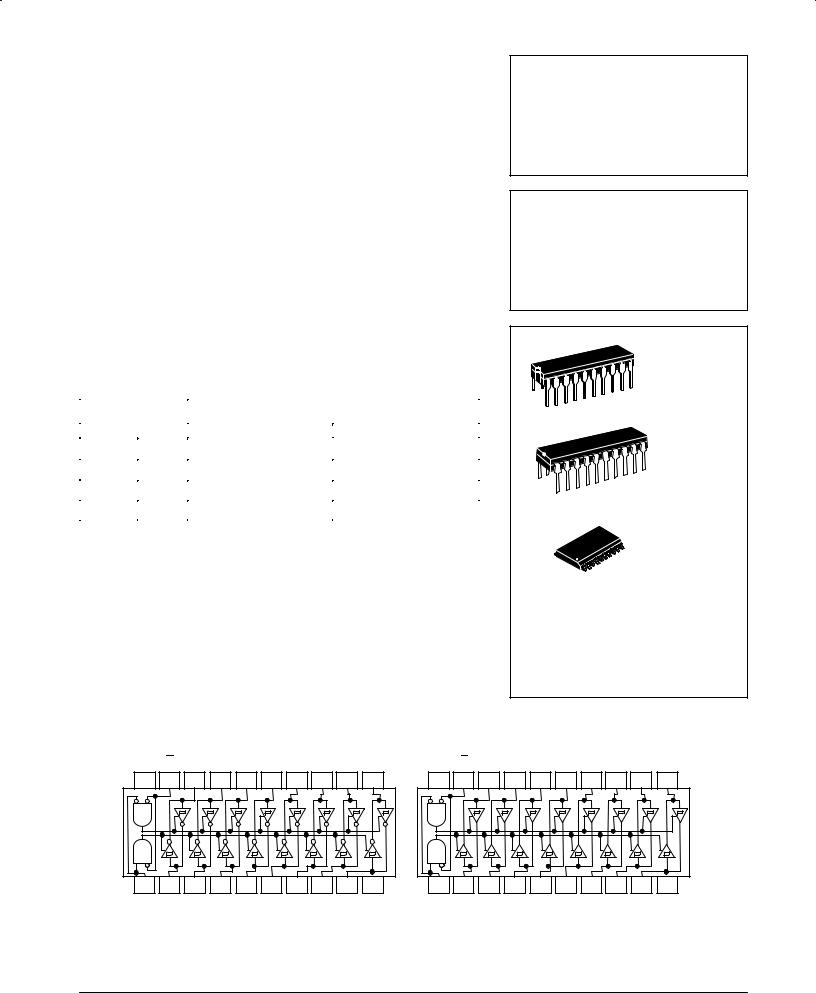

SN54/74LS640

SN54/74LS641

SN54/74LS642

SN54/74LS645

OCTAL BUS TRANSCEIVERS

LOW POWER SCHOTTKY

|

J SUFFIX |

|

|

CERAMIC |

|

20 |

CASE 732-03 |

|

|

||

1 |

|

|

|

N SUFFIX |

|

|

PLASTIC |

|

20 |

CASE 738-03 |

|

|

||

1 |

|

|

|

DW SUFFIX |

|

20 |

SOIC |

|

CASE 751D-03 |

||

|

||

|

1 |

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXDW SOIC

CONNECTION DIAGRAMS DIP (TOP VIEW)

ENABLE |

B1 |

B2 |

B3 |

B4 |

B5 |

B6 |

B7 |

B8 |

|

VCC |

G |

||||||||

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

DIR |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

A8 |

GND |

|

|

|

|

SN54 / 74LS640 |

|

|

|

||

|

|

|

|

SN54 / 74LS642 |

|

|

|

||

ENABLE |

B1 |

B2 |

B3 |

B4 |

B5 |

B6 |

B7 |

B8 |

|

VCC |

G |

||||||||

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

DIR |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

A8 |

GND |

|

|

|

|

SN54 / 74LS641 |

|

|

|

||

|

|

|

|

SN54 / 74LS645 |

|

|

|

||

FAST AND LS TTL DATA

5-1

Loading...

Loading...