MOTOROLA SN74LS169M, SN74LS169MEL, SN74LS169ML1, SN74LS169N Datasheet

BCD DECADE/MODULO

16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS

The SN54/74LS168 and SN54/74LS169 are fully synchronous 4-stage up/down counters featuring a preset capability for programmable operation, carry lookahead for easy cascading and a U/D input to control the direction of counting. The SN54/74LS168 counts in a BCD decade (8, 4, 2, 1) sequence, while the SN54/74LS169 operates in a Modulo 16 binary sequence. All state changes, whether in counting or parallel loading, are initiated by the LOW-to-HIGH transition of the clock.

•Low Power Dissipation 100 mW Typical

•High-Speed Count Frequency 30 MHz Typical

•Fully Synchronous Operation

•Full Carry Lookahead for Easy Cascading

•Single Up/Down Control Input

•Positive Edge-Trigger Operation

•Input Clamp Diodes Limit High-Speed Termination Effects

CONNECTION DIAGRAM DIP (TOP VIEW)

|

|

|

VCC |

|

TC |

Q0 |

|

Q1 |

Q2 |

Q3 |

|

CET |

PE |

|

|

|

|

||||||

|

|

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The Flatpak version |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

has the same pinouts |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Connection Diagram) as |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

|

|

|

|

|

|

|

|

U/D |

|

CP |

P0 |

|

P1 |

P2 |

P3 |

|

CEP |

GND |

|

|

|

|

||||||

PIN NAMES |

|

|

|

|

|

|

|

|

|

|

|

|

|

LOADING (Note a) |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH |

LOW |

||

|

|

|

|

|

|

|

|

||||||||||||||||

CEP |

Count Enable Parallel (Active LOW) Input |

0.5 U.L. |

0.25 |

U.L. |

|||||||||||||||||||

CET |

Count Enable Trickle (Active LOW) Input |

1.0 U.L. |

0.5 |

U.L. |

|||||||||||||||||||

CP |

Clock Pulse (Active positive going edge) Input |

0.5 U.L. |

0.25 |

U.L. |

|||||||||||||||||||

PE |

Parallel Enable (Active LOW) Input |

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

|||||||||||||||

|

|

|

Up-Down Count Control Input |

|

|

|

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

||||||||||

U/D |

|

|

|

|

|

|

|||||||||||||||||

P0±P3 |

Parallel Data Inputs |

|

|

|

|

|

|

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

|||||||||

Q0±Q3 |

Flip-Flop Outputs |

|

|

|

|

|

|

|

|

|

10 |

U.L. |

5 (2.5) |

U.L. |

|||||||||

TC |

Terminal Count (Active LOW) Output |

|

|

|

10 |

U.L. |

5 (2.5) |

U.L. |

|||||||||||||||

NOTES:

a.1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b.The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

SN54/74LS168

SN54/74LS169

BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 620-09 |

16 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

16 |

|

|

CASE 648-08 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

16 |

|

SOIC |

|

|

CASE 751B-03 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

LOGIC SYMBOL

|

|

|

9 |

3 |

4 |

5 |

6 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

1 |

|

|

PE P0 P1 P2 P3 |

|

|

|||||||

|

|

U/D |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

7 |

|

|

CEP |

|

|

|

|

|

TC |

|

15 |

|

|

|

|

|

|

|

|

|

|||||

10 |

|

|

CET |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

2 |

|

|

CP |

Q0 Q1 |

Q2 Q3 |

|

|

|||||

|

|

|

||||||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

14 13 12 11

VCC = PIN 16

GND = PIN 8

FAST AND LS TTL DATA

5-1

SN54/74LS168 •SN54/74LS169

|

|

|

|

|

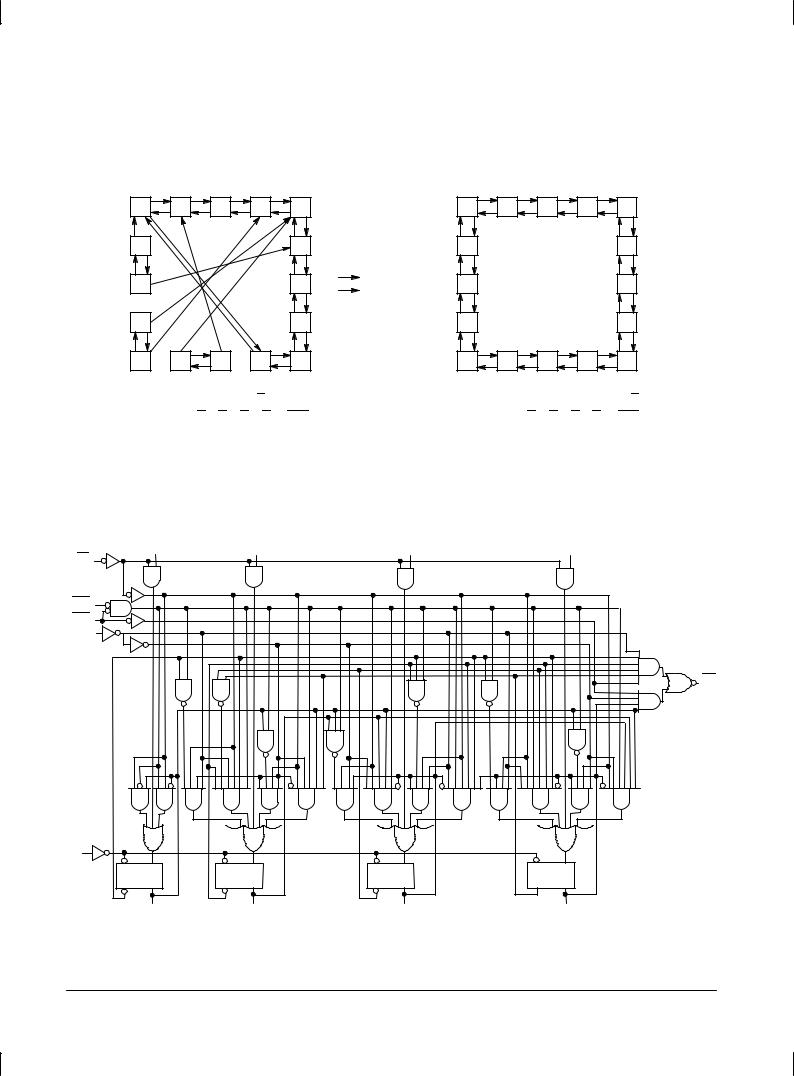

STATE DIAGRAMS |

|

|

|

|

|

|

SN54/ 74LS168 |

|

|

|

SN54 / 74LS169 |

|

||||

UP / DOWN DECADE COUNTER |

|

|

|

|

|

|

||||

0 |

1 |

2 |

3 |

4 |

|

0 |

1 |

2 |

3 |

4 |

15 |

|

|

|

5 |

|

15 |

|

|

|

5 |

14 |

|

|

|

6 |

Count Up |

14 |

|

|

|

6 |

|

|

|

Count Down |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

7 |

|

13 |

|

|

|

7 |

12 |

11 |

10 |

9 |

8 |

|

12 |

11 |

10 |

9 |

8 |

SN54 / 74LS168 |

|

|

|

|

SN54 / 74LS169 |

|

|

|

||

UP: |

TC = Q0 Q3 (U / D) |

|

|

UP: |

TC = Q0 Q1 Q2 Q3 (U / D) |

|||||

DOWN: |

TC = Q0 Q1 Q2 Q3 (U / D) |

|

DOWN: |

TC = Q0 Q1 Q2 Q3 (U / D) |

||||||

|

|

|

LOGIC DIAGRAMS |

|

|

|

|

SN54 / 74LS168 |

|

PE |

P0 |

P1 |

P2 |

P3 |

|

|

|

|

|

CEP |

|

|

|

|

CET |

|

|

|

|

U/D |

|

|

|

|

|

|

|

|

TC |

CP |

|

|

|

|

CP |

D |

|

|

|

|

Q0 |

Q1 |

Q2 |

Q3 |

FAST AND LS TTL DATA

5-2

Loading...

Loading...