Motorola SN54LS253J, SN74LS253N, SN74LS253DW Datasheet

DUAL 4-INPUT MULTIPLEXER WITH 3-STATE OUTPUTS

The LSTTL/MSI SN54/74LS253 is a Dual 4-Input Multiplexer with 3-state outputs. It can select two bits of data from four sources using common select inputs. The outputs may be individually switched to a high impedance state with a HIGH on the respective Output Enable (E0) inputs, allowing the outputs to interface directly with bus oriented systems. It is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

•Schottky Process for High Speed

•Multifunction Capability

•Non-Inverting 3-State Outputs

•Input Clamp Diodes Limit High Speed Termination Effects

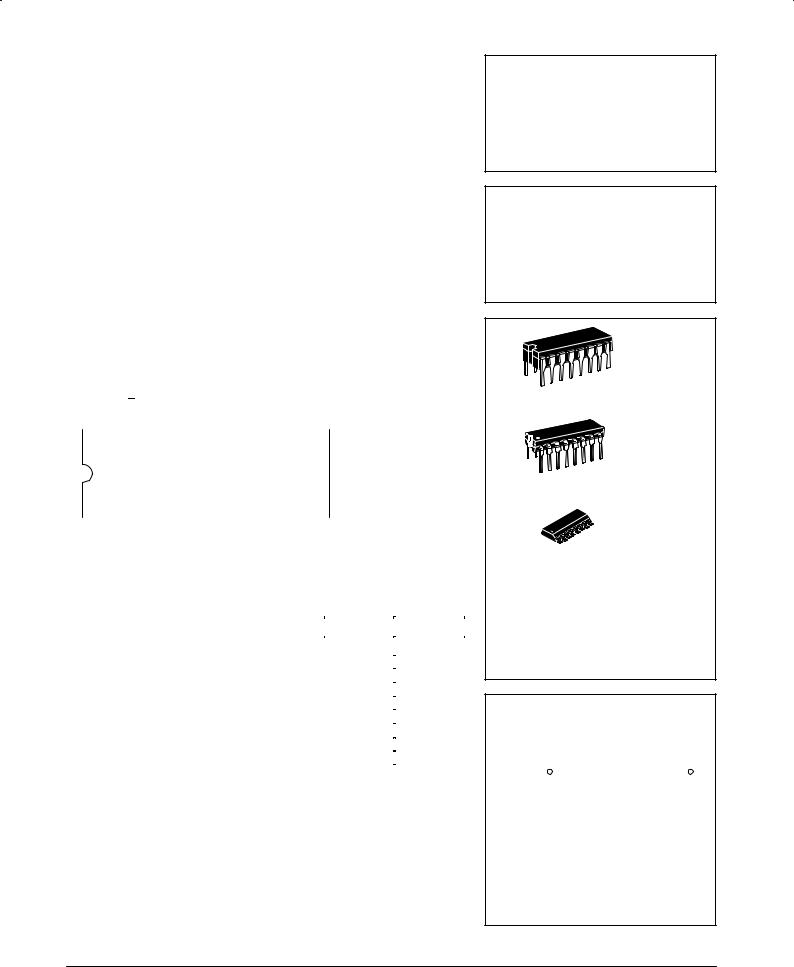

CONNECTION DIAGRAM DIP (TOP VIEW)

VCC |

|

E0b |

S0 |

|

I3b |

|

I2b |

|

I1b |

|

I0b |

|

Zb |

|||

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE:

The Flatpak version has the same pinouts

(Connection Diagram) as the Dual In-Line Package.

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E0a |

|

S1 |

|

I3a |

|

I2a |

I1a |

I0a |

Za |

|

GND |

||||

PIN NAMES |

|

LOADING (Note a) |

|

||

|

|

HIGH |

LOW |

||

|

|

|

|

|

|

S0, S1 |

Common Select Inputs |

0.5 |

U.L. |

0.25 |

U.L. |

Multiplexer A |

|

|

|

|

|

E0a |

Output Enable (Active LOW) Input |

0.5 |

U.L. |

0.25 |

U.L. |

I0a ± I3a |

Multiplexer Inputs |

0.5 |

U.L. |

0.25 |

U.L. |

Za |

Multiplexer Output (Note b) |

65 (25) |

U.L. |

15 (7.5) |

U.L. |

Multiplexer B |

|

|

|

|

|

E0b |

Output Enable (Active LOW) Input |

0.5 |

U.L. |

0.25 |

U.L. |

I0b ± I3b |

Multiplexer Inputs |

0.5 |

U.L. |

0.25 |

U.L. |

Zb |

Multiplexer Output (Note b) |

65 (25) |

U.L. |

15 (7.5) |

U.L. |

NOTES:

a)1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b)The Output LOW drive factor is 7.5 U.L. for Military (54) and 15 U.L. for Commercial (74) Temperature Ranges. The Output HIGH drive factor is 25 U.L. for Military (54) and 65 U.L. for Commercial (74) Temperature Ranges.

SN54/74LS253

DUAL 4-INPUT MULTIPLEXER WITH 3-STATE OUTPUTS

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 620-09 |

16 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

16 |

|

|

CASE 648-08 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

16 |

|

SOIC |

|

|

CASE 751B-03 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

LOGIC SYMBOL

|

|

|

1 |

6 |

5 |

4 |

3 |

10 |

11 |

|

12 13 |

15 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

S |

E0a I0a I1a I2a |

I3a |

I0b I1b |

I2b I3b |

E0b |

||||||||||||||||

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

S1 |

|

|

|

|

Za |

|

|

|

|

Zb |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

79

VCC = PIN 16

GND = PIN 8

FAST AND LS TTL DATA

5-416

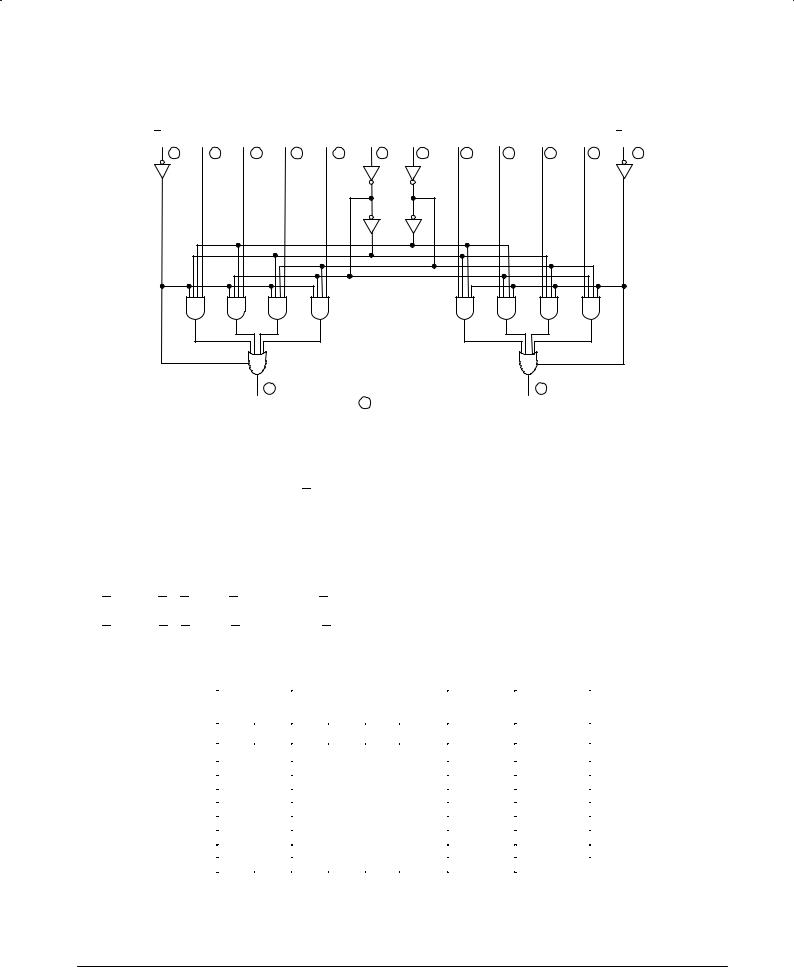

LOGIC DIAGRAM

E0b

15

|

|

|

|

SN54/74LS253 |

|

|

|

|

|||

I3b |

I2b |

I1b |

I0b |

S0 |

|

S1 |

I3a |

I2a |

I1a |

I0a |

E0a |

13 |

12 |

|

11 |

10 |

14 |

2 |

3 |

4 |

5 |

6 |

1 |

Zb |

|

VCC |

= |

PIN |

16 |

Za |

|

9 |

GND |

= |

PIN |

8 |

7 |

||

|

|

|

= |

PIN |

NUMBERS |

|

|

FUNCTIONAL DESCRIPTION

The LS253 contains two identical 4-Input Multiplexers with 3-state outputs. They select two bits from four sources selected by common select inputs (S0, S1). The 4-input multiplexers have individual Output Enable (E0a, E0b) inputs which when HIGH, forces the outputs to a high impedance (high Z) state.

The LS253 is the logic implementation of a 2-pole, 4-position switch, where the position of the switch is determined by the logic levels supplied to the two select inputs. The logic equations for the outputs are shown below:

Za = E0a (I0a S1 S0 + I1a S1 S0 I2a S1 S0 + I3a S1S0)

Zb = E0b (I0b S1 S0 + I1b S1 S0 I2b S1 S0 + I3b S1S0)

If the outputs of 3-state devices are tied together, all but one device must be in the high impedance state to avoid high currents that would exceed the maximum ratings. Designers should ensure that Output Enable signals to 3-state devices whose outputs are tied together are designed so that there is no overlap.

TRUTH TABLE

SELECT |

|

DATA INPUTS |

|

OUTPUT |

OUTPUT |

||

INPUTS |

|

|

ENABLE |

||||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

S0 |

S1 |

I0 |

I1 |

I2 |

I3 |

E0 |

Z |

X |

X |

X |

X |

X |

X |

H |

(Z) |

L |

L |

L |

X |

X |

X |

L |

L |

L |

L |

H |

X |

X |

X |

L |

H |

H |

L |

X |

L |

X |

X |

L |

L |

H |

L |

X |

H |

X |

X |

L |

H |

L |

H |

X |

X |

L |

X |

L |

L |

L |

H |

X |

X |

H |

X |

L |

H |

H |

H |

X |

X |

X |

L |

L |

L |

H |

H |

X |

X |

X |

H |

L |

H |

|

|

|

|

|

|

|

|

H = HIGH Level

L = LOW Level

X = Irrelevant

(Z) = High Impedance (off)

Address inputs S0 and S1 are common to both sections.

FAST AND LS TTL DATA

5-417

Loading...

Loading...