Motorola SN54LS138J, SN74LS138D, SN74LS138N Datasheet

1-OF-8 DECODER/ DEMULTIPLEXER

The LSTTL/MSI SN54/74LS138 is a high speed 1-of-8 Decoder/ Demultiplexer. This device is ideally suited for high speed bipolar memory chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three LS138 devices or to a 1-of-32 decoder using four LS138s and one inverter. The LS138 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

•Demultiplexing Capability

•Multiple Input Enable for Easy Expansion

•Typical Power Dissipation of 32 mW

•Active Low Mutually Exclusive Outputs

•Input Clamp Diodes Limit High Speed Termination Effects

CONNECTION DIAGRAM DIP (TOP VIEW)

|

VCC |

|

O0 |

O1 |

|

O2 |

|

O3 |

O4 |

|

O5 |

O6 |

|

|

|

|

||||||||

|

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The Flatpak version |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

has the same pinouts |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Connection Diagram) as |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the Dual In-Line Package. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

|

A1 |

A2 |

|

E1 |

|

E2 |

E3 |

|

O7 |

GND |

|

|

|

|

||||||

PIN NAMES |

|

|

|

|

|

|

|

|

|

|

|

|

|

LOADING (Note a) |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH |

LOW |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

A0 ± A2 |

|

|

|

|

Address Inputs |

|

|

|

|

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

||||||||

E1, E2 |

|

|

|

|

Enable (Active LOW) Inputs |

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

||||||||||||

E3 |

|

|

|

|

|

|

Enable (Active HIGH) Input |

|

|

|

0.5 |

U.L. |

0.25 |

U.L. |

||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||

O0 ± O7 |

|

|

|

|

Active LOW Outputs (Note b) |

10 |

U.L. |

5 (2.5) |

U.L. |

|||||||||||||||

NOTES:

a)1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b)The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

SN54/74LS138

1-OF-8 DECODER/ DEMULTIPLEXER

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 620-09 |

16 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

16 |

|

|

CASE 648-08 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

16 |

|

SOIC |

|

|

CASE 751B-03 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

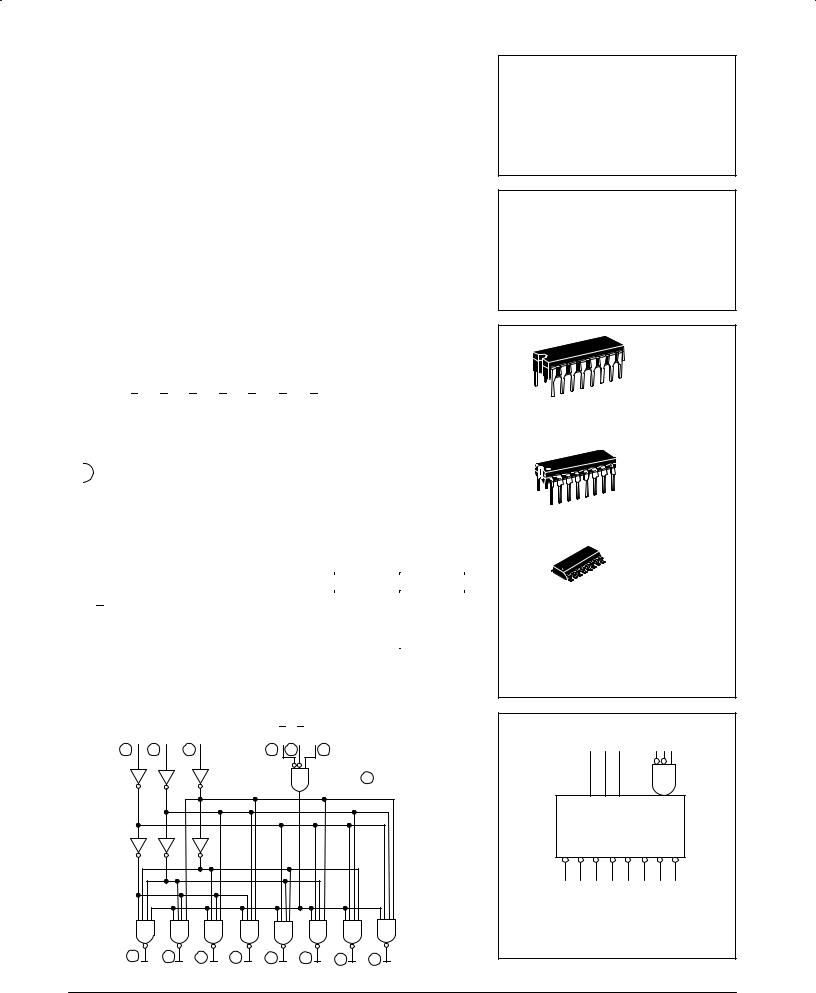

LOGIC DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

LOGIC SYMBOL |

|

||||||

A2 |

A1 |

|

A0 |

|

|

E1 E2 E3 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

3 |

2 |

|

1 |

|

4 |

5 |

6 |

|

VCC |

= |

PIN |

16 |

|

1 |

2 |

3 |

|

4 5 6 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

GND |

= |

PIN |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= |

PIN |

NUMBERS |

|

|

|

|

|

1 2 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 A1 A2 |

|

E |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

O0 O1 O2 O3 O4 O5 O6 O7 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = PIN 16 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

= |

PIN |

8 |

|

|

7 |

9 |

|

10 |

11 |

12 |

|

13 |

14 |

15 |

|

|

|

|

|

|

|

|

|

|

O7 |

O6 |

O5 |

O4 |

|

O3 |

O2 |

|

O1 |

O0 |

|

|

|

|

|

|

|

|

|

|

FAST AND LS TTL DATA

5-230

SN54/74LS138

FUNCTIONAL DESCRIPTION

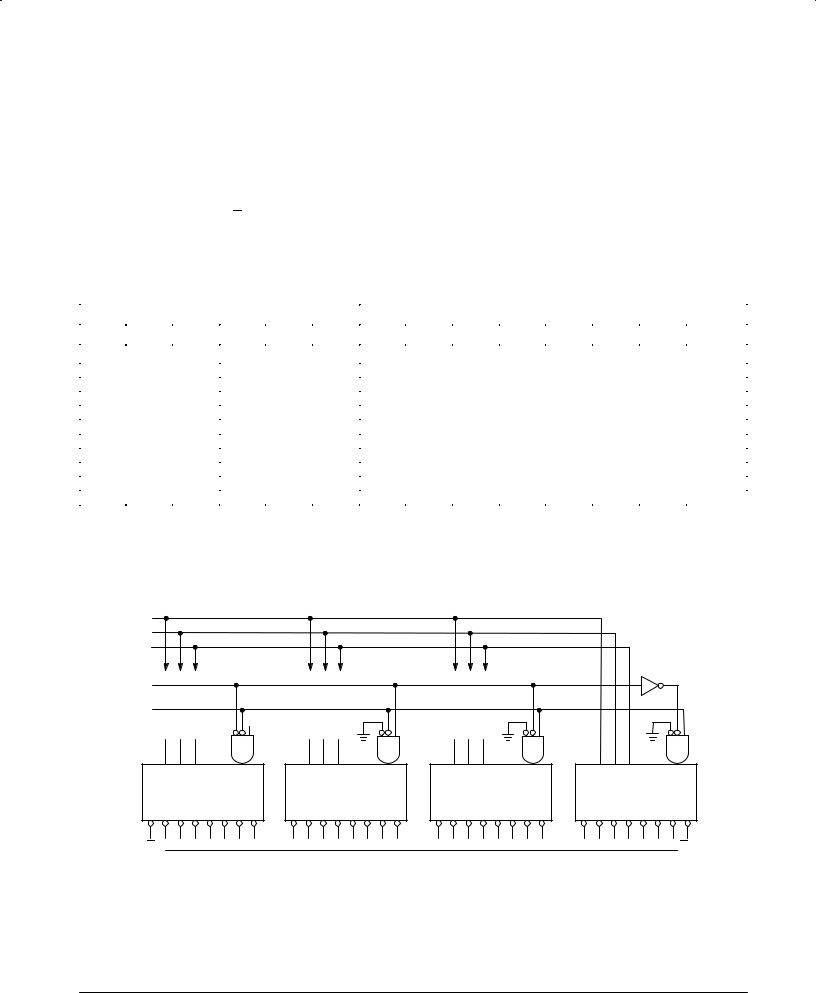

The LS138 is a high speed 1-of-8 Decoder/Demultiplexer fabricated with the low power Schottky barrier diode process. The decoder accepts three binary weighted inputs (A0, A1, A2) and when enabled provides eight mutually exclusive active LOW Outputs (O0 ±O7). The LS138 features three Enable inputs, two active LOW (E1, E2) and one active HIGH (E3). All outputs will be HIGH unless E1 and E2 are LOW and E3 is HIGH. This multiple enable function allows easy parallel ex-

pansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four LS138s and one inverter. (See Figure a.)

The LS138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active HIGH or active LOW state.

TRUTH TABLE

|

|

INPUTS |

|

|

|

|

|

OUTPUTS |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 |

E2 |

E3 |

A0 |

A1 |

A2 |

O0 |

O1 |

O2 |

O3 |

O4 |

O5 |

O6 |

O7 |

H |

X |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

X |

H |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

X |

X |

L |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

L |

L |

H |

L |

L |

L |

L |

H |

H |

H |

H |

H |

H |

H |

L |

L |

H |

H |

L |

L |

H |

L |

H |

H |

H |

H |

H |

H |

L |

L |

H |

L |

H |

L |

H |

H |

L |

H |

H |

H |

H |

H |

L |

L |

H |

H |

H |

L |

H |

H |

H |

L |

H |

H |

H |

H |

L |

L |

H |

L |

L |

H |

H |

H |

H |

H |

L |

H |

H |

H |

L |

L |

H |

H |

L |

H |

H |

H |

H |

H |

H |

L |

H |

H |

L |

L |

H |

L |

H |

H |

H |

H |

H |

H |

H |

H |

L |

H |

L |

L |

H |

H |

H |

H |

H |

H |

H |

H |

H |

H |

H |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

A0 |

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

A2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LS04 |

A3 |

|

|

|

|

|

|

|

A4 |

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

1 2 3 |

|

1 2 3 |

|

1 2 3 |

|

1 2 3 |

A0 A1 A2 |

E |

A0 A1 A2 |

E |

A0 A1 A2 |

E |

A0 A1 A2 |

E |

LS138 |

LS138 |

LS138 |

LS138 |

O0 O1 O2 O3 O4 O5 O6 O7 |

O0 O1 O2 O3 O4 O5 O6 O7 |

O0 O1 O2 O3 O4 O5 O6 O7 |

O0 O1 O2 O3 O4 O5 O6 O7 |

O0 |

|

|

O31 |

Figure a

FAST AND LS TTL DATA

5-231

Loading...

Loading...