Texas Instruments HPC3130APGE, HPC3130APBK, HPC3130APBM Datasheet

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D Compliant With PCI Hot-Plug Specification,

Revision 1.0

D Supports up to Four Independently

Controlled Hot-Plug Slots

D Provides Register Accessing Through Both

Generic Parallel Bus and Two-Wire Serial

Interface

D Provides Interrupt and Event Status/Enable

State Compliant With ACPI Specification

1.0

D Provides an Automatic Bus Connection

Sequencing Feature

D Supports 66-MHz PCI Clock Frequency

D Features Two Attention Indicators With

Variable LED Blinking Rates per Slot

D Provides an Easy Scheme to Cascade the

HPC3130A for Compact PCI Applications

D Provides Card Detection Mechanism

Independent of PCI Present Signals for

Advanced Card Protection

D Provides Path to Guarantee Idle State

During PCI Bus Connections

D Fabricated in Advanced Low-Power CMOS

Process

D Features a CBT Switch

†

Control Feature for

REQ64 Implementation

D Package Options:

– 120-pin QFP Package

– 128-pin LQFP Package

– 144-pin LQFP Package

Table of Contents

Description 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 MHz PCI Support 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Block Diagram 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Configuration and Control Registers 25. . . . . . . . . . . . . . . . . . . . . . . . .

Pin Assignments (120-Pin) 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Absolute Maximum Ratings 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pin Assignments (128-Pin) 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Recommended Operating Conditions 33. . . . . . . . . . . . . . . . . . . . . . . .

Pin Assignments (144-Pin) 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Serial Bus Interface 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Name/Pin Number Sort Table (120-Pin) 6. . . . . . . . . . . . . . . . . Electrical Characteristics 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Name/Pin Number Sort Table (128-Pin) 8. . . . . . . . . . . . . . . . . PCI Clock/Reset Timing Requirements 35. . . . . . . . . . . . . . . . . . . . . . .

Signal Name/Pin Number Sort Table (144-Pin) 10. . . . . . . . . . . . . . . . PCI Timing Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Terminal Functions 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Mechanical Data (120-Pin) 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HPC3130A Applications 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Mechanical Data (128-Pin) 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

64-Bit Implementation 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Mechanical Data (144-Pin) 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Copyright 1999, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†

Contact Texas Instrument’s Bus Interface product group for information related to CBT switches.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description

The T exas Instruments HPC3130A is a peripheral component interconnect (PCI) hot-plug controller , compliant

with

PCI Hot-Plug Specification, Revision 1.0

. This device supports hot insertion/removal of up to four hot-plug

slots on a PCI bus, provides a 64-bit data path in any of the four hot-plug slots, and supports 66-MHz systems

for two slots.

The primary function of the HPC3130A is to allow noninterfering hot-plug slot connection/disconnection with

the other PCI devices on the bus. The HPC3130A provides automatic bus connection sequencing and supports

a protocol for connection during bus idle conditions. It also supports an interrupt pin to report hot-plug slot

events. The interrupt event status and enable state are compliant with the

Advanced Configuration and Power

Interface (ACPI) Specification

.

Internal registers may be accessed through either a two-signal serial interface or a generic parallel bus. The

serial interface slave decoding circuit supports up to eight different controllers or other serial bus devices with

the same system base. Decoding through the parallel interface supports multiple controllers with external

chip-select logic. Two double-words of configuration and control registers are provided per slot. As a result, the

HPC3130A decodes an address range of 32 bytes.

An advanced complementary metal-oxide semiconductor (CMOS) process provides low system power

consumption while operating at PCI clock rates up to 66 MHz.

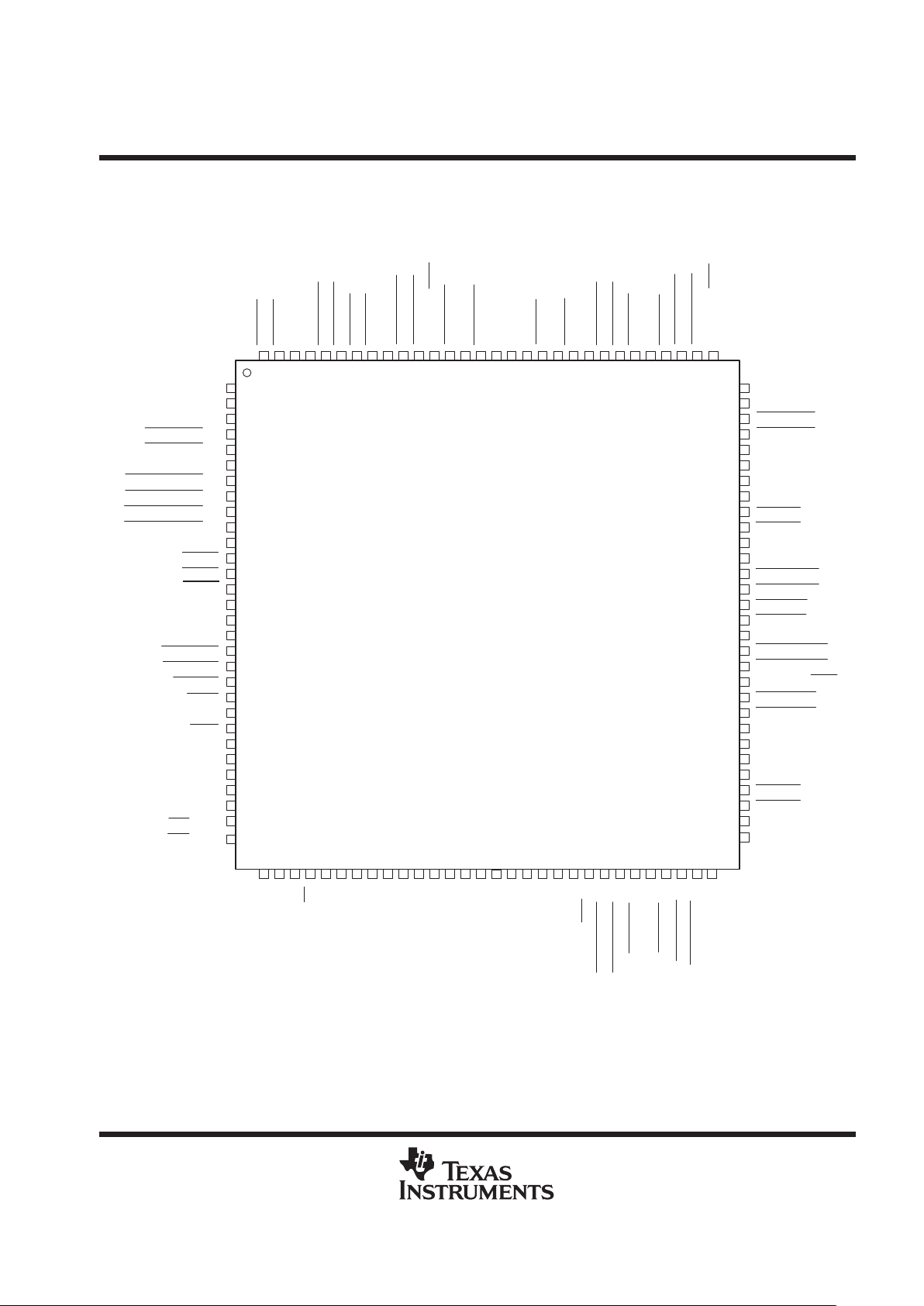

functional block diagram

A simplified block diagram of the HPC3130A is provided below. The block diagram illustrates the HPC3130A

functionality on a per slot basis. The SMODE chip input, not shown, is used for terminal multiplexing of the serial

and parallel bus slave interfaces.

CS

Parallel

Bus

Slave

Interface

Serial Bus

Slave I/F

Switch

Timing

Control

and

Status

Registers

Slot

Power I/F

Card

Detection

CBT-Switch

Control

and

Slot Reset

Attention

Indicators

RD

WR

DATA 7–0

A 4–0

SDA

SCL

ADD 6–0

IDLEREQ

IDLEGNT

FRAME

IRDY

SREQ

SGNT

PCLK

PWRON/OFF

PWRFAULT

PWRGOOD

PRSNT2

PRSNT1

REQ64ON

REQ64ON

CLKON

SLOTRST

SLOTREQ64

ATTN0

ATTN1

SYSM66EN

INTR

PRST

BUSON

M66EN

DETECT

SYSTEM INTERFACE SLOT INTERFACE

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

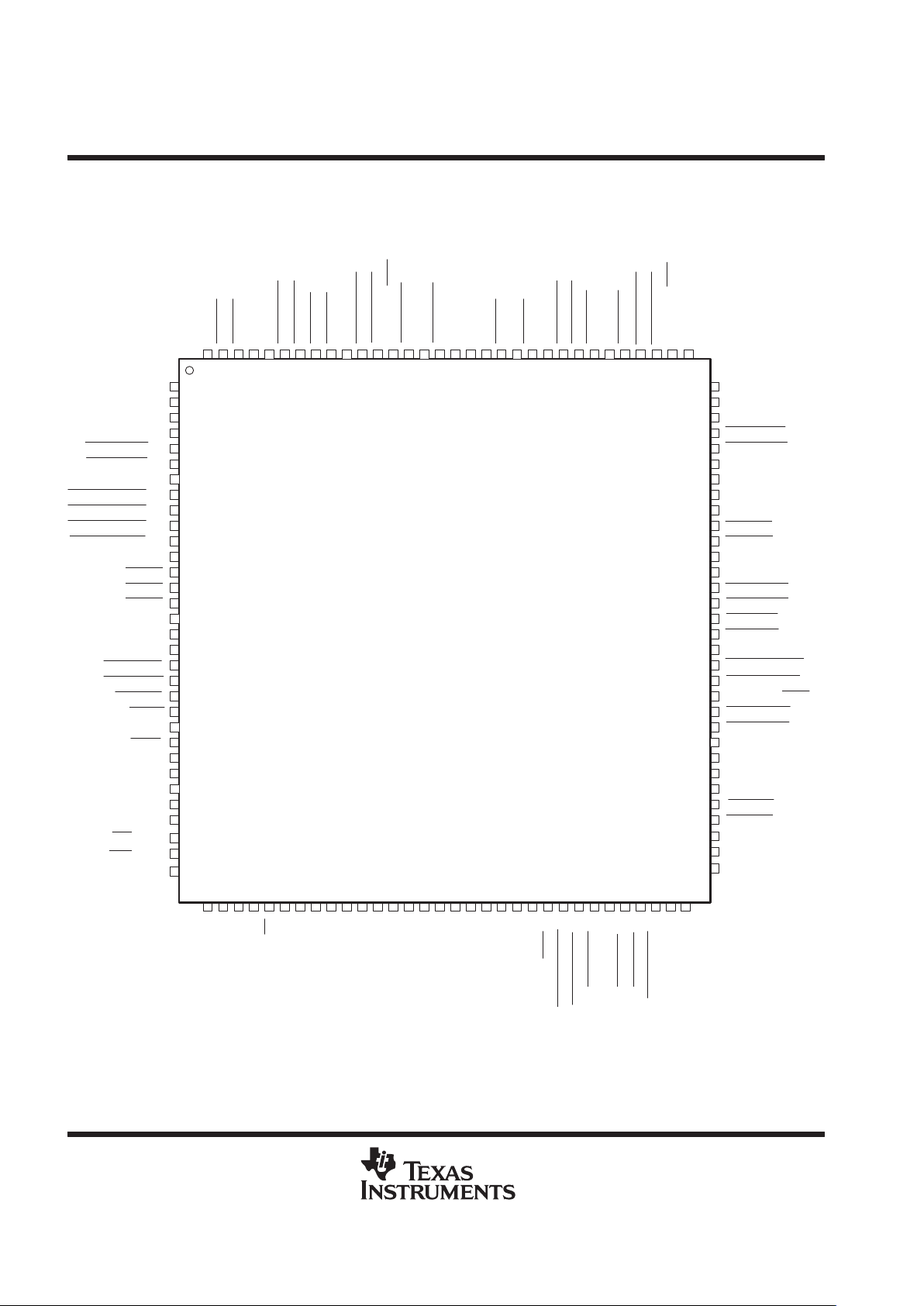

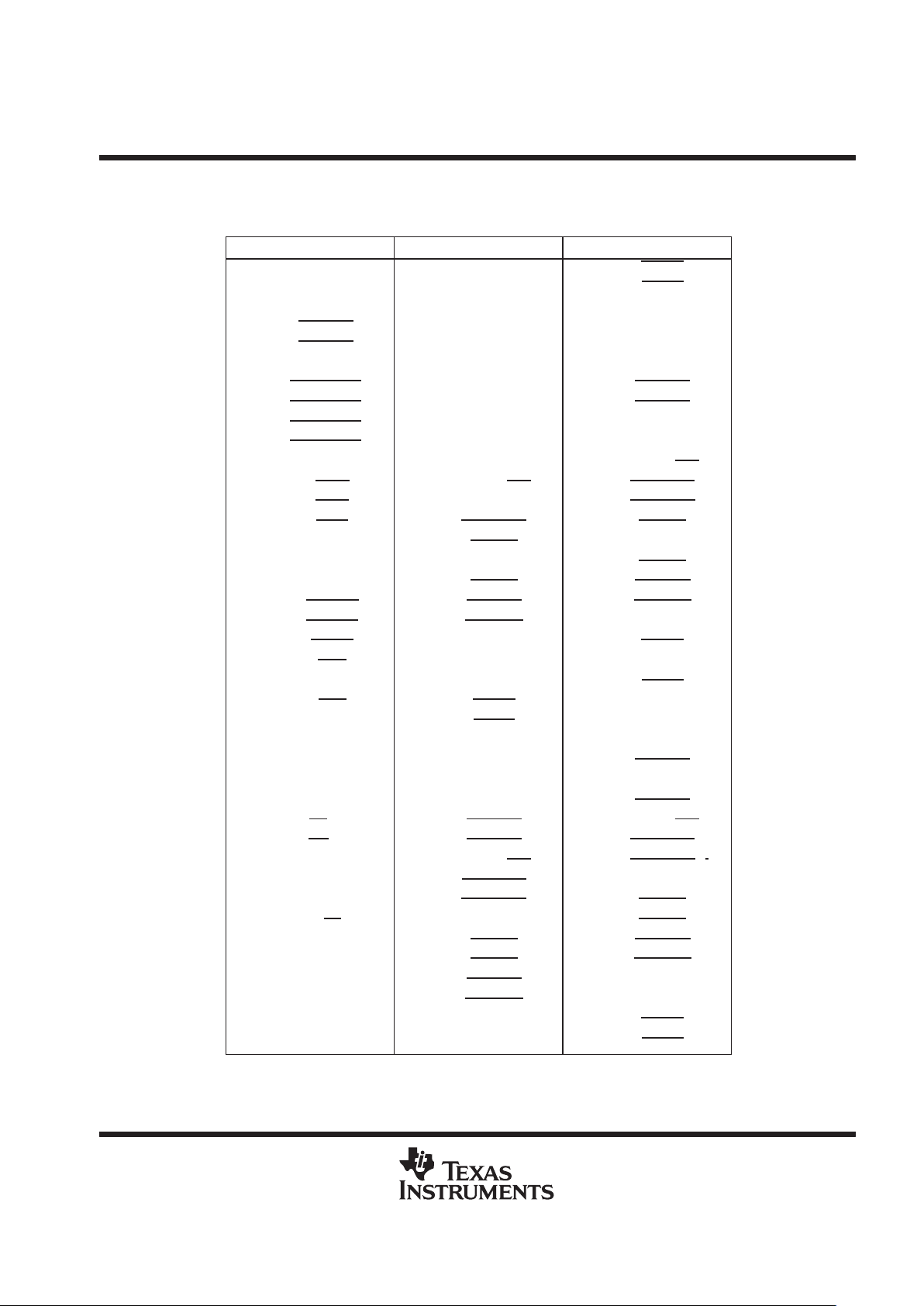

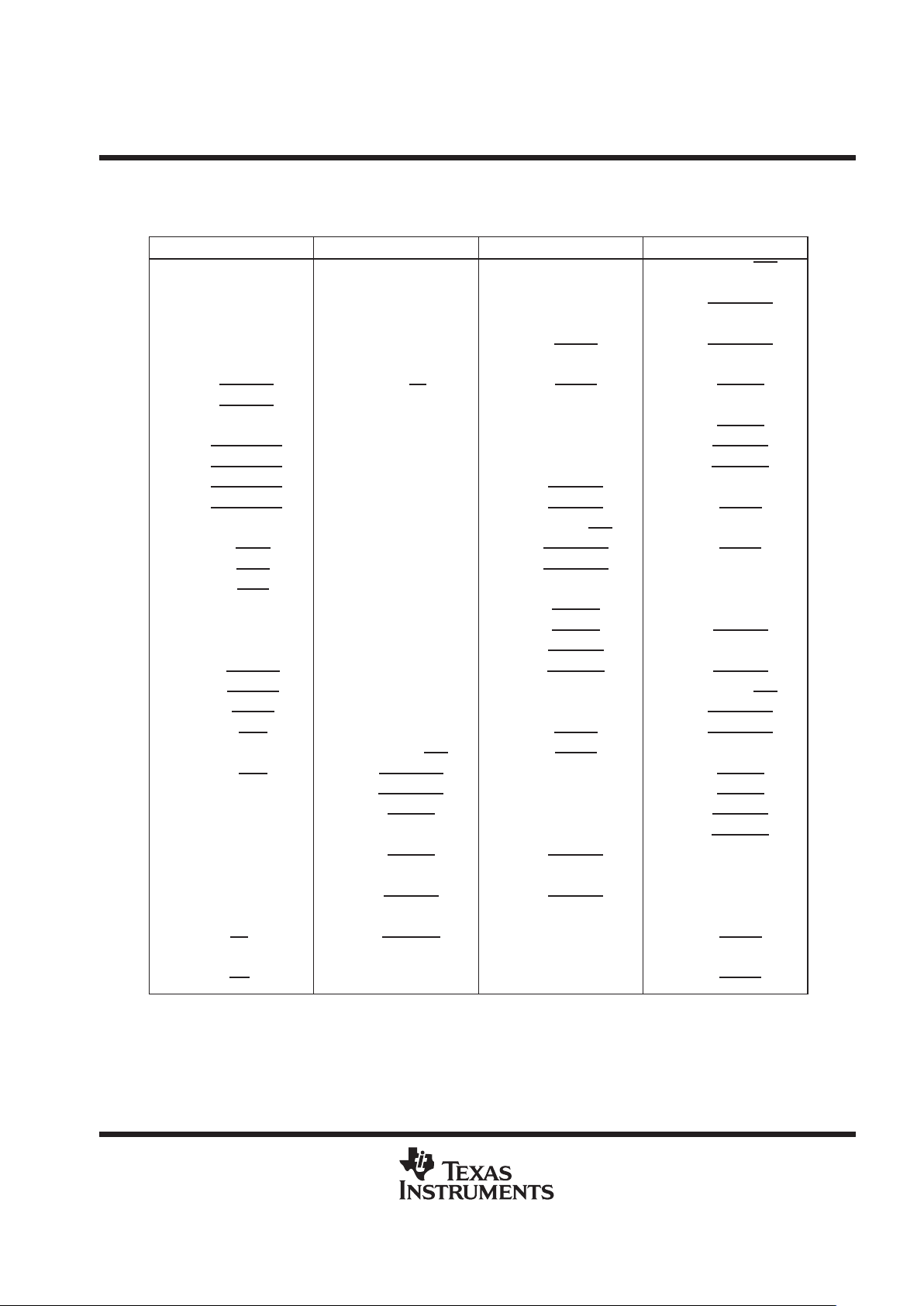

terminal assignments (120-terminal package)

PBM QUAD FLAT PACKAGE

TOP VIEW

PRST

PWRON/OFF[3]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

91

92

60

30

61

RSVD

RSVD

DETECT1[1]

DETECT0[1]

M66EN[1]

ATTN1[1]

ATTN0[1]

CLKON[1]

BUSON[1]

REQ64ON[1]

GND

REQ64ON[1]

SLOTRST[1]

PRSNT2[1]

PWRGOOD[1]

DETECT1[0]

DETECT0[0]

GND

M66EN[0]

ATTN1[0]

ATTN0[0]

CLKON[0]

BUSON[0]

RSVD

RSVD

PWRFAULT[1]

ATTN0[3]

M66EN[3]

DETECT0[3]

SLOTREQ64[3]

SLOTREQ64[2]

SLOTREQ64[1]

SLOTREQ64[0]

GND

SREQ

SGNT

SMODE

PCLK

GND

IDLEREQ

IDLEGNT

FRAME

IRDY

INTR

INTR

SYSM66EN

GND

RD/SDA

WR/SCL

CLKON[3]

BUSON[3]

REQ64ON[3]

GND

REQ64ON[3]

SLOTRST[3]

PRSNT2[3]

PRSNT1[3]

GND

PWRGOOD[3]

DETECT1[2]

DETECT0[2]

M66EN[2]

ATTN1[2]

ATTN0[2]

CLKON[2]

GND

BUSON[2]

REQ640N[2]

REQ64ON[2]

SLOTRST[2]

PRSNT2[2]

PRSNT1[2]

PWRGOOD[2]

PWRFAULT[2]

PWRON/OFF[2]

RSVD

RSVD

RSVD

CS

DATA7

DATA6

DATA4

DATA3

GND

DATA2

DATA1/ADD6

DATA0/ADD5

A4/ADD4

A2/ADD2

A1/ADD1

GND

PWRON/OFF[0]

PWRFAULT[0]

PWRGOOD[0]

PRSNT1[0]

PRSNT2[0]

SLOTRST[0]

REQ64ON[0]

V

CC

ATTN1[3]

V

CC5V

CC

V

CC

V

A3/ADD3

CC

V

V

CC

V

CCP

V

CC5V

DETECT1[3]

V

CC5V

PRSNT1[1]

PWRON/OFF[1]

5V

PWRFAULT[3]

CC

V

DATA5

CC

V

5V

REQ64ON[0]

A0/ADD0

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

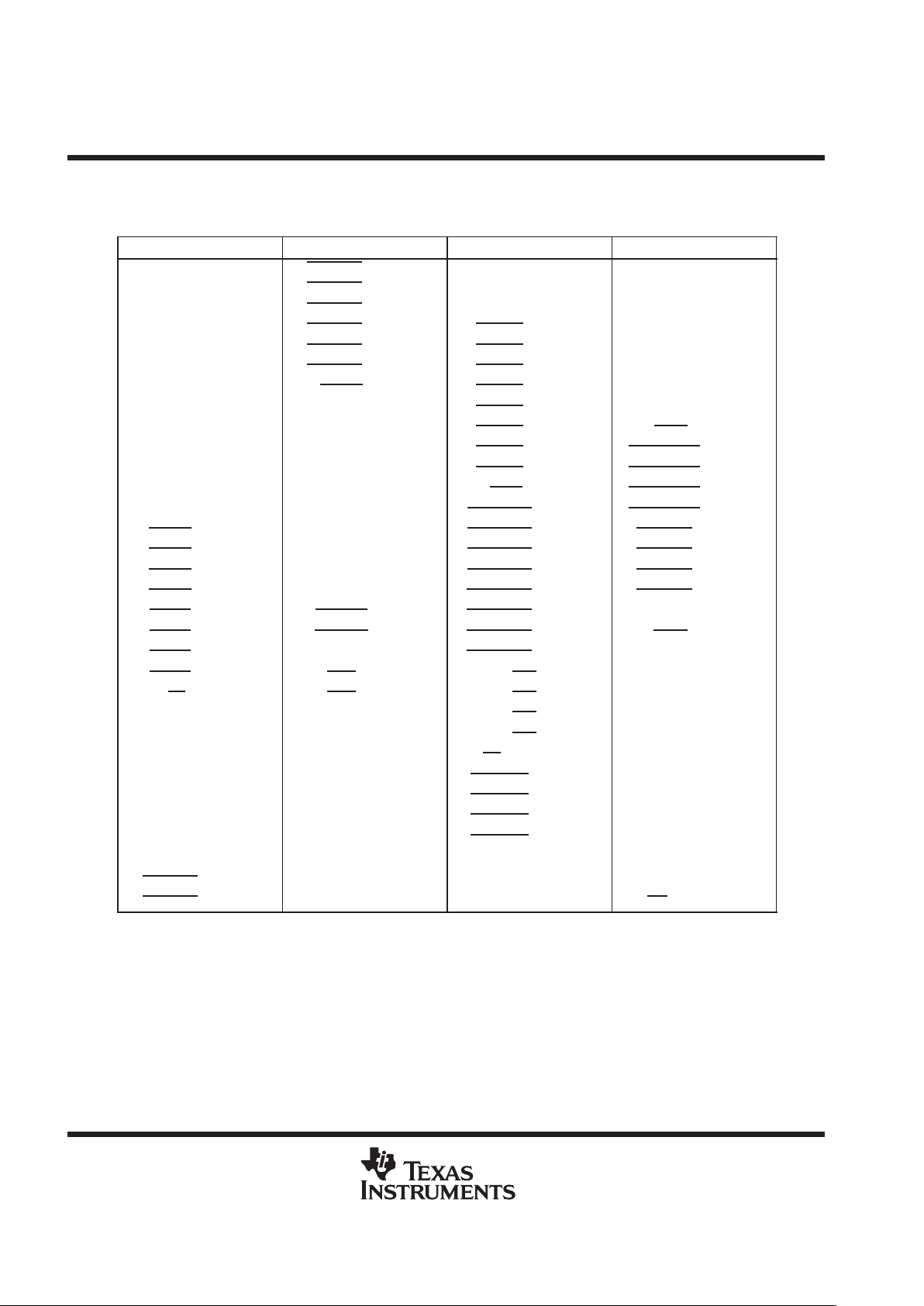

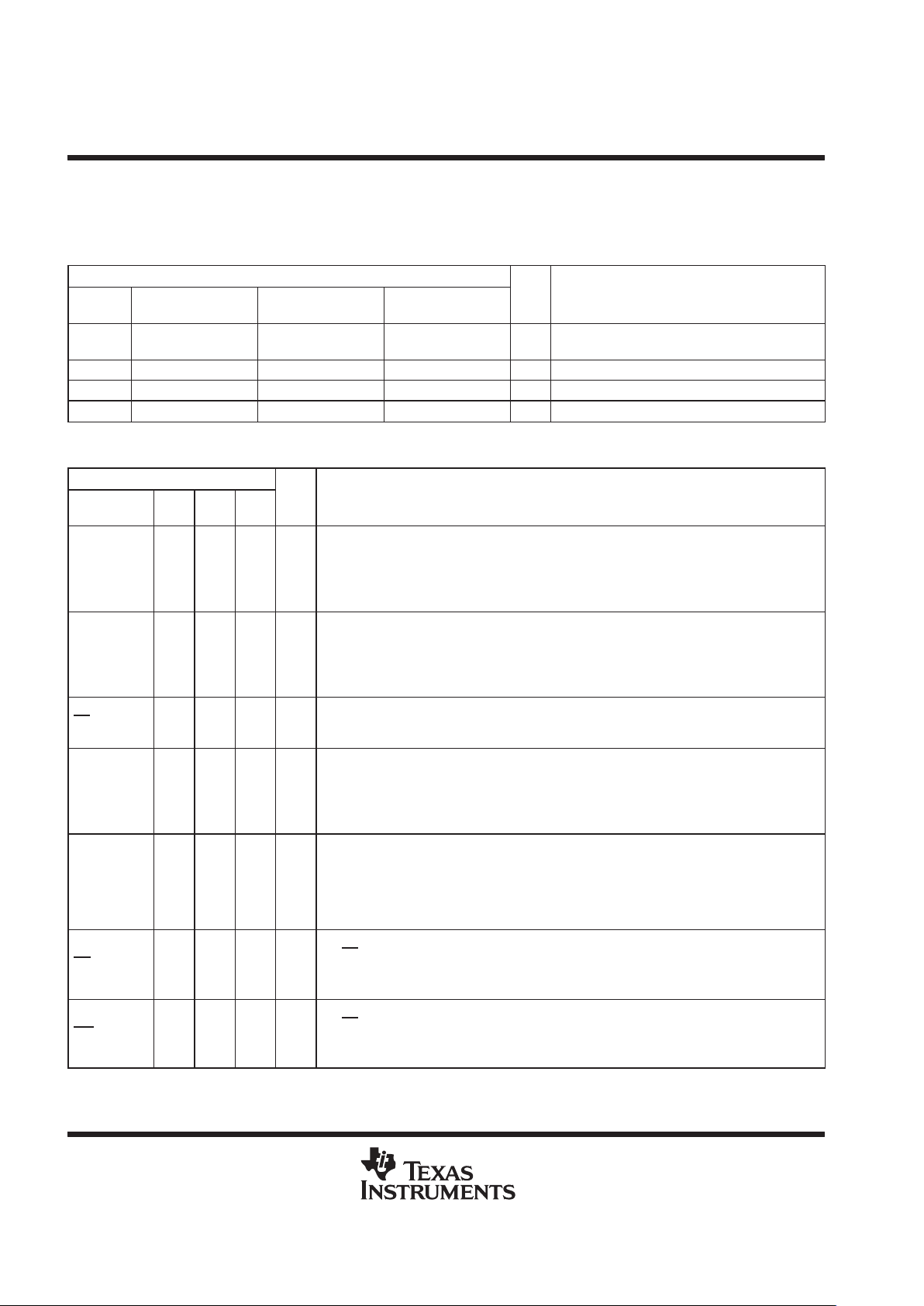

terminal assignments (128-terminal package)

PBK LOW-PROFILE QUAD FLAT PACKAGE

TOP VIEW

GND

A0/ADD0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

101

102

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

99

100

62

30

67

NC

RSVD

RSVD

DETECT1[1]

DETECT0[1]

ATTN1[1]

ATTN0[1]

CLKON[1]

BUSON[1]

REQ64ON[1]

GND

REQ64ON[1]

SLOTRST[1]

PRSNT2[1]

PRSNT1[1]

PWRFAULT[1

PWRON/OFF[1]

DETECT1[0]

DETECT0[0]

GND

M66EN[0]

ATTN1[0]

ATTN0[0]

CLKON[0]

BUSON[0]

RSVD

NC

ATTN1[3]

M66EN[3]

DETECT0[3]

DETECT1[3]

SLOTREQ64[3]

SLOTREQ64[2]

SLOTREQ64[1]

SLOTREQ64[0]

GND

SGNT

PRST

PCLK

GND

IDLEREQ

IDLEGNT

FRAME

IRDY

INTR

INTR

GND

SMODE

RD/SDA

NC

CLKON[3]

BUSON[3]

REQ64ON[3]

GND

REQ64ON[3]

SLOTRST[3]

PRSNT2[3]

PRSNT1[3]

GND

PWRGOOD[3]

PWRON/OFF[3]

DETECT1[2]

DETECT0[2]

M66EN[2]

ATTN1[2]

ATTN0[2]

CLKON[2]

GND

BUSON[2]

REQ64ON[2]

REQ64ON[2]

PRSNT2[2]

PRSNT1[2]

PWRGOOD[2]

PWRFAULT[2]

NC

RSVD

RSVD

RSVD

CS

DATA7

DATA6

DATA5

DATA4

DATA3

GND

DATA2

DATA1/ADD6

DATA0/ADD5

A4/ADD4

A3/ADD3

A2/ADD2

PWRON/OFF[0]

PWRFAULT[0]

PWRGOOD[0]

PRSNT1[0]

NC

PRSNT2[0]

SLOTRS[0]

REQ64ON[0]

V

CC

V

CC

V

CC5V

CC

V

CC

V

CC

V

32

WR/SCL

NC

31

63

64

97

98

PWRON/OFF[2]

NC

66

65

RSVD

NC

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

ATTN0[3]

M66EN[1]

SREQ

V

CC5V

PWRGOOD[1]

]

V

CCP

SYSM66EN

V

CC5V

PWRFAULT[3]

5V

SLOTRST[2]

CC

V

CC

V

5V

A1/ADD1

REQ64ON[0]

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

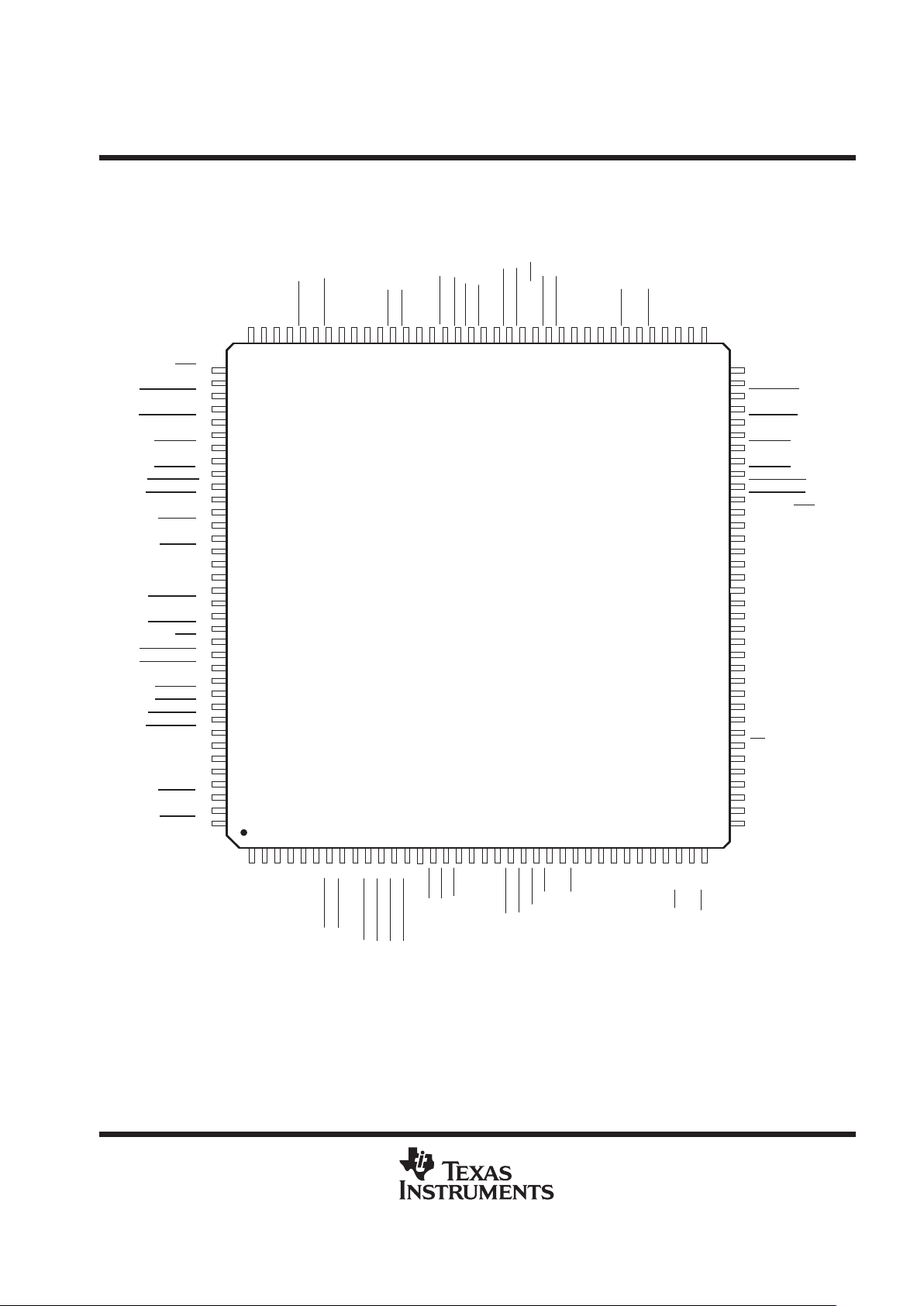

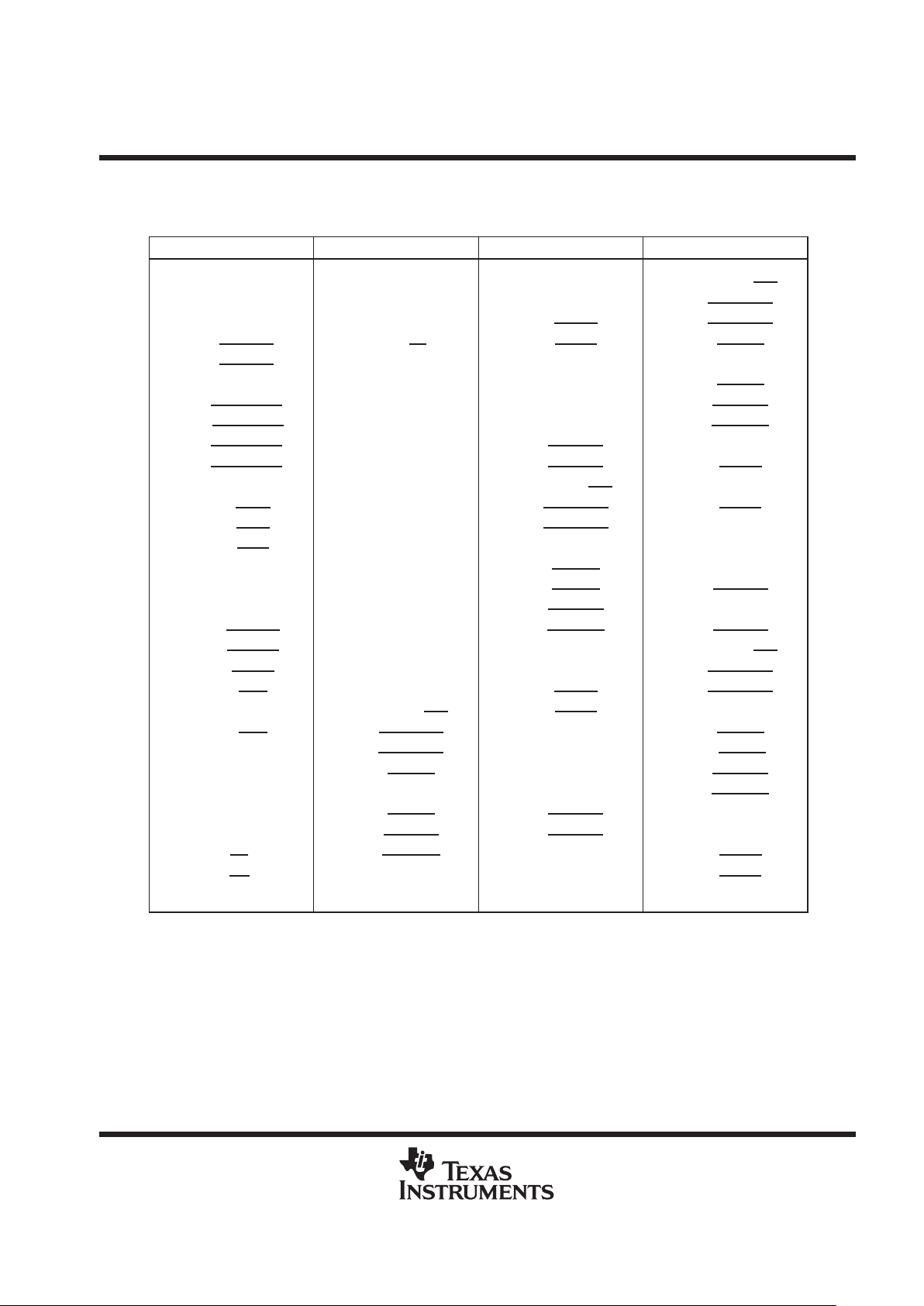

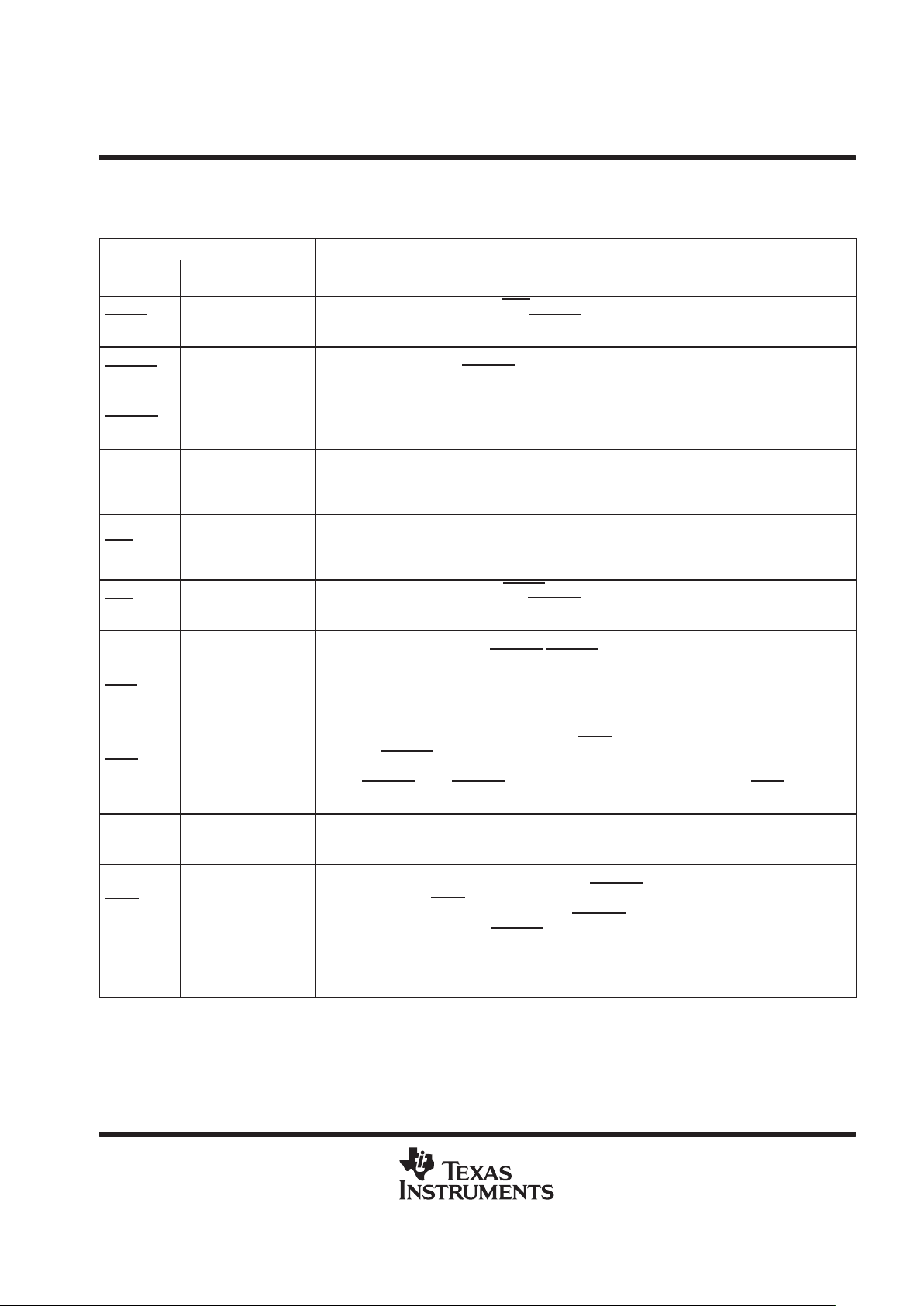

terminal assignments (144-terminal package)

PGE LOW-PROFILE QUAD FLAT PACKAGE

TOP VIEW

PRSNT1[2]

SLOTRST[1]

CC

V

1234567891011121314151617181920212223242526272829303132333435

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

ATTN0[3]

NC

NC

M66EN[3]

NC

GND

PCLK

DETECT0[3]

IDLEGNT

FRAME

IRDY

IDLEREQ

SYSM66EN

GND

SMODE

NC

NC

NC

RSVD

NC

NC

RSVD

NC

DATA7

DATA6

DATA5

DATA3

GND

DATA2

DATA0/ADD5

A4/ADD4

A1/ADD1

NC

NC

A0/ADD0

GND

NC

RSVD

NC

ATTN0[0]

ATTN1[0]

M66EN[0]

GND

BUSON[0]

PRSNT1[1]

REQ64ON[1]

GND

REQ64ON[1]

ATTN0[1]

ATTN1[1]

M66EN[1]

NC

NC

RSVD

NC

NC

NC

NC

REQ64ON[2]

ATTN0[2]

ATTN1[2]

M66EN[2]

GND

GND

NC

REQ64ON[3]

NC

NC

PWRGOOD

[3]

PWRON/OFF

[2]

SREQ

CC5V

V

V

CC

CS

PWRFAULT[3]

V

CC

CC

V

CC5V

V

PWRFAULT[2]

NC

PWRGOOD

[2]

PRSNT2[2]

REQ64ON

[2]

BUSON[2]

SLOTRST[2]

CLKON[2]

DETECT0

[2]

V

CC5V

PWRON/OFF

[3]

DETECT1

[2]

GND

PRSNT1

[3]

PRSNT2[3]

SLOTRST

[3]

REQ64ON

[3]

BUSON

[3]

CLKON[3]

RSVD

DATA4

DATA1/ADD6

V

CC5V

A3/ADD3

A2/ADD2

PWRON/OFF

[0]

V

CC

PWRFAULT[0]

PWRGOOD

[0]

PRSNT1[0]

PRSNT2[0]

SLOTRST[0]

REQ64ON[0]

NC

REQ64ON[0]

RSVD

CLKON[0]

DETECT0[0]

DETECT1[0]

PWRON/OFF[1]

PWRFAULT[1]

PWRGOOD[1]

PRSNT2[1]

BUSON[1]

CLKON[1]

DETECT0[1]

DETECT1[1]

RSVD

ATTN1[3]

GND

DETECT1[3]

SLOTREQ64[3]

SLOTREQ64[2]

SLOTREQ64[1]

SLOTREQ64[0]

SGNT

PRST

CCP

V

INTR

INTR

CC5V

V

RD/SDA

WR/SCL

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

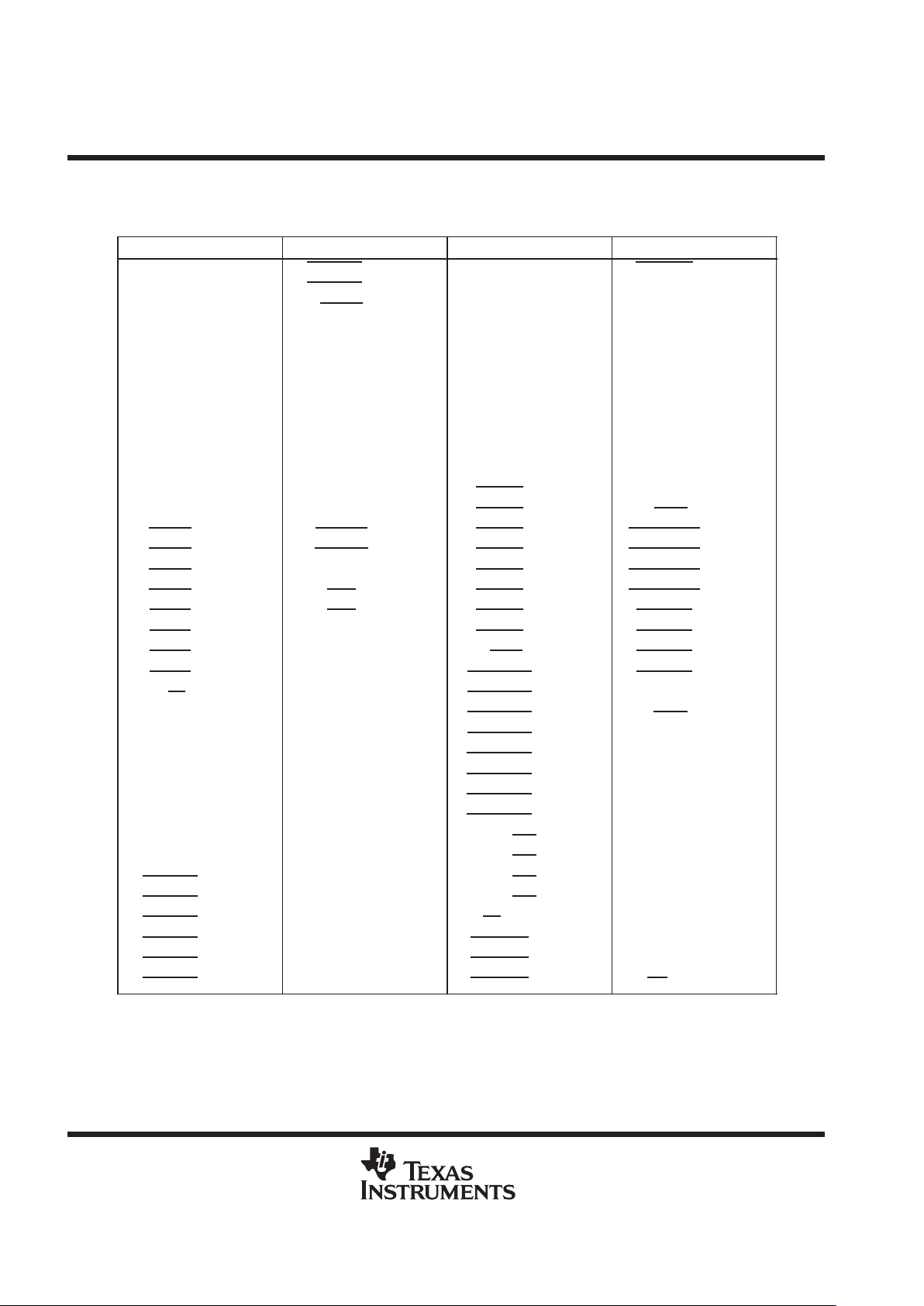

signal names by terminal name

Table 1. Signals Sorted Alphabetically by Terminal Name (120-Terminal Package)

TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO.

A0/ADD0 50 GND 17 RD/SDA 29

A1/ADD1 49 GND 26 REQ64ON[0] 59

A2/ADD2 48 GND 41 REQ64ON[1] 78

A3/ADD3 47 GND 51 REQ64ON[2] 98

A4/ADD4 45 GND 68 REQ64ON[3] 116

ATTN0[0] 65 GND 79 REQ64ON[0] 60

ATTN0[1] 83 GND 101 REQ64ON[1] 80

ATTN0[2] 103 GND 112 REQ64ON[2] 99

ATTN0[3] 1 GND 117 REQ64ON[3] 118

ATTN1[0] 66 IDLEGNT 19 RSVD 31

ATTN1[1] 84 IDLEREQ 18 RSVD 32

ATTN1[2] 104 INTR 24 RSVD 33

ATTN1[3] 2 INTR 23 RSVD 61

BUSON[0] 63 IRDY 21 RSVD 62

BUSON[1] 81 M66EN[0] 67 RSVD 89

BUSON[2] 100 M66EN[1] 86 RSVD 90

BUSON[3] 119 M66EN[2] 105 SGNT 13

CLKON[0] 64 M66EN[3] 3 SLOTREQ64[0] 10

CLKON[1] 82 PCLK 16 SLOTREQ64[1] 9

CLKON[2] 102 PRSNT1[0] 55 SLOTREQ64[2] 8

CLKON[3] 120 PRSNT1[1] 75 SLOTREQ64[3] 7

CS 34 PRSNT1[2] 94 SLOTRST[0] 58

DATA0/ADD5 44 PRSNT1[3] 113 SLOTRST[1] 77

DATA1/ADD6 43 PRSNT2[0] 57 SLOTRST[2] 97

DATA2 42 PRSNT2[1] 76 SLOTRST[3] 115

DATA3 40 PRSNT2[2] 96 SMODE 27

DATA4 39 PRSNT2[3] 114 SREQ 12

DATA5 38 PRST 14 SYSM66EN 25

DATA6 37 PWRFAULT[0] 53 V

CC

6

DATA7 35 PWRFAULT[1] 72 V

CC

36

DETECT0[0] 69 PWRFAULT[2] 92 V

CC

56

DETECT0[1] 87 PWRFAULT[3] 110 V

CC

85

DETECT0[2] 106 PWRGOOD[0] 54 V

CC

95

DETECT0[3] 4 PWRGOOD[1] 73 V

CC5V

15

DETECT1[0] 70 PWRGOOD[2] 93 V

CC5V

28

DETECT1[1] 88 PWRGOOD[3] 111 V

CC5V

46

DETECT1[2] 108 PWRON/OFF[0] 52 V

CC5V

74

DETECT1[3] 5 PWRON/OFF[1] 71 V

CC5V

107

FRAME 20 PWRON/OFF[2] 91 V

CCP

22

GND 11 PWRON/OFF[3] 109 WR/SCL 30

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

signal names by terminal number

Table 2. Signals Sorted Numerically by Terminal Number (120-Terminal Package)

NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME

1 ATTN0[3] 41 GND 81 BUSON[1]

2 ATTN1[3] 42 DATA2 82 CLKON[1]

3 M66EN[3] 43 DATA1/ADD6 83 ATTN0[1]

4 DETECT0[3] 44 DATA0/ADD5 84 ATTN1[1]

5 DETECT1[3] 45 A4/ADD4 85 V

CC

6 V

CC

46 V

CC5V

86 M66EN[1]

7 SLOTREQ64[3] 47 A3/ADD3 87 DETECT0[1]

8 SLOTREQ64[2] 48 A2/ADD2 88 DETECT1[1]

9 SLOTREQ64[1] 49 A1/ADD1 89 RSVD

10 SLOTREQ64[0] 50 A0/ADD0 90 RSVD

11 GND 51 GND 91 PWRON/OFF[2]

12 SREQ 52 PWRON/OFF[0] 92 PWRFAULT[2]

13 SGNT 53 PWRFAULT[0] 93 PWRGOOD[2]

14 PRST 54 PWRGOOD[0] 94 PRSNT1[2]

15 V

CC5V

55 PRSNT1[0] 95 V

CC

16 PCLK 56 V

CC

96 PRSNT2[2]

17 GND 57 PRSNT2[0] 97 SLOTRST[2]

18 IDLEREQ 58 SLOTRST[0] 98 REQ64ON[2]

19 IDLEGNT 59 REQ64ON[0] 99 REQ64ON[2]

20 FRAME 60 REQ64ON[0] 100 BUSON[2]

21 IRDY 61 RSVD 101 GND

22 V

CCP

62 RSVD 102 CLKON[2]

23 INTR 63 BUSON[0] 103 ATTN0[2]

24 INTR 64 CLKON[0] 104 ATTN1[2]

25 SYSM66EN 65 ATTN0[0] 105 M66EN[2]

26 GND 66 ATTN1[0] 106 DETECT0[2]

27 SMODE 67 M66EN[0] 107 V

CC5V

28 V

CC5V

68 GND 108 DETECT1[2]

29 RD/SDA 69 DETECT0[0] 109 PWRON/OFF[3]

30 WR/SCL 70 DETECT1[0] 110 PWRFAULT[3]

31 RSVD 71 PWRON/OFF[1] 111 PWRGOOD[3]

32 RSVD 72 PWRFAULT[1] 112 GND

33 RSVD 73 PWRGOOD[1] 113 PRSNT1[3]

34 CS 74 V

CC5V

114 PRSNT2[3]

35 DATA7 75 PRSNT1[1] 115 SLOTRST[3]

36 V

CC

76 PRSNT2[1] 116 REQ64ON[3]

37 DATA6 77 SLOTRST[1] 117 GND

38 DATA5 78 REQ64ON[1] 118 REQ64ON[3]

39 DATA4 79 GND 119 BUSON[3]

40 DATA3 80 REQ64ON[1] 120 CLKON[3]

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

signal names by terminal name

Table 3. Signals Sorted Alphabetically by Terminal Name (128-Terminal Package)

TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO.

A0/ADD0 53 DETECT0[2] 113 NC 97 REQ64ON[3] 125

A1/ADD1 52 DETECT0[3] 5NC128 RSVD 34

A2/ADD2 51 DETECT1[0] 75 PCLK 17 RSVD 35

A3/ADD3 50 DETECT1[1] 93 PRSNT1[0] 58 RSVD 36

A4/ADD4 48 DETECT1[2] 115 PRSNT1[1] 80 RSVD 66

ATTN0[0] 70 DETECT1[3] 6 PRSNT1[2] 101 RSVD 67

ATTN0[1] 88 FRAME 21 PRSNT1[3] 120 RSVD 94

ATTN0[2] 110 GND 12 PRSNT2[0] 60 RSVD 95

ATTN0[3] 2 GND 18 PRSNT2[1] 81 SGNT 14

ATTN1[0] 71 GND 27 PRSNT2[2] 103 SLOTREQ64[0] 11

ATTN1[1] 89 GND 44 PRSNT2[3] 121 SLOTREQ64[1] 10

ATTN1[2] 111 GND 54 PRST 15 SLOTREQ64[2] 9

ATTN1[3] 3 GND 73 PWRFAULT[0] 56 SLOTREQ64[3] 8

BUSON[0] 68 GND 84 PWRFAULT[1] 77 SLOTRST[0] 61

BUSON[1] 86 GND 108 PWRFAULT[2] 99 SLOTRST[1] 82

BUSON[2] 107 GND 119 PWRFAULT[3] 117 SLOTRST[2] 104

BUSON[3] 126 GND 124 PWRGOOD[0] 57 SLOTRST[3] 122

CLKON[0] 69 IDLEGNT 20 PWRGOOD[1] 78 SMODE 28

CLKON[1] 87 IDLEREQ 19 PWRGOOD[2] 100 SREQ 13

CLKON[2] 109 INTR 25 PWRGOOD[3] 118 SYSM66EN 26

CLKON[3] 127 INTR 24 PWRON/OFF[0] 55 V

CC

7

CS 37 IRDY 22 PWRON/OFF[1] 76 V

CC

39

DATA0/ADD5 47 M66EN[0] 72 PWRON/OFF[2] 98 V

CC

59

DATA1/ADD6 46 M66EN[1] 91 PWRON/OFF[3] 116 V

CC

90

DATA2 45 M66EN[2] 112 RD/SDA 30 V

CC

102

DATA3 43 M66EN[3] 4 REQ64ON[0] 62 V

CC5V

16

DATA4 42 NC 1 REQ64ON[1] 83 V

CC5V

29

DATA5 41 NC 32 REQ64ON[2] 105 V

CC5V

49

DATA6 40 NC 33 REQ64ON[3] 123 V

CC5V

79

DATA7 38 NC 64 REQ64ON[0] 63 V

CC5V

114

DETECT0[0] 74 NC 65 REQ64ON[1] 85 V

CCP

23

DETECT0[1] 92 NC 96 REQ64ON[2] 106 WR/SCL 31

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

signal names by terminal number

Table 4. Signals Sorted Numerically by Terminal Number (128-Terminal Package)

NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME

1 NC 33 NC 65 NC 97 NC

2 ATTN0[3] 34 RSVD 66 RSVD 98 PWRON/OFF[2]

3 ATTN1[3] 35 RSVD 67 RSVD 99 PWRFAULT[2]

4 M66EN[3] 36 RSVD 68 BUSON[0] 100 PWRGOOD[2]

5 DETECT0[3] 37 CS 69 CLKON[0] 101 PRSNT1[2]

6 DETECT1[3] 38 DATA7 70 ATTN0[0] 102 V

CC

7 V

CC

39 V

CC

71 ATTN1[0] 103 PRSNT2[2]

8 SLOTREQ64[3] 40 DATA6 72 M66EN[0] 104 SLOTRST[2]

9 SLOTREQ64[2 41 DATA5 73 GND 105 REQ64ON[2]

10 SLOTREQ64[1] 42 DATA4 74 DETECT0[0] 106 REQ64ON[2]

11 SLOTREQ64[0] 43 DATA3 75 DETECT1[0] 107 BUSON[2]

12 GND 44 GND 76 PWRON/OFF[1] 108 GND

13 SREQ 45 DATA2 77 PWRFAULT[1] 109 CLKON[2]

14 SGNT 46 DATA1/ADD6 78 PWRGOOD[1] 110 ATTN0[2]

15 PRST 47 DATA0/ADD5 79 V

CC5V

111 ATTN1[2]

16 V

CC5V

48 A4/ADD4 80 PRSNT1[1] 112 M66EN[2]

17 PCLK 49 V

CC5V

81 PRSNT2[1] 113 DETECT0[2]

18 GND 50 A3/ADD3 82 SLOTRST[1] 114 V

CC5V

19 IDLEREQ 51 A2/ADD2 83 REQ64ON[1] 115 DETECT1[2]

20 IDLEGNT 52 A1/ADD1 84 GND 116 PWRON/OFF[3]

21 FRAME 53 A0/ADD0 85 REQ64ON[1] 117 PWRFAULT[3]

22 IRDY 54 GND 86 BUSON[1] 118 PWRGOOD[3]

23 V

CCP

55 PWRON/OFF[0] 87 CLKON[1] 119 GND

24 INTR 56 PWRFAULT[0] 88 ATTN0[1] 120 PRSNT1[3]

25 INTR 57 PWRGOOD[0] 89 ATTN1[1] 121 PRSNT2[3

26 SYSM66EN 58 PRSNT1[0] 90 V

CC

122 SLOTRST[3]

27 GND 59 V

CC

91 M66EN[1] 123 REQ64ON[3]

28 SMODE 60 PRSNT2[0] 92 DETECT0[1] 124 GND

29 V

CC5V

61 SLOTRST[0] 93 DETECT1[1] 125 REQ64ON[3]

30 RD/SDA 62 REQ64ON[0] 94 RSVD 126 BUSON[3]

31 WR/SCL 63 REQ64ON[0] 95 RSVD 127 CLKON[3]

32 NC 64 NC 96 NC 128 NC

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

signal names by terminal name

Table 5. Signals Sorted Alphabetically by Terminal Name (144-Terminal Package)

TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO.

A0/ADD0 59 DETECT1[2] 129 NC 78 REQ64ON[3] 137

A1/ADD1 58 DETECT1[3] 8NC103 REQ64ON[0] 72

A2/ADD2 57 FRAME 23 NC 105 REQ64ON[1] 95

A3/ADD3 56 GND 14 NC 107 REQ64ON[2] 120

A4/ADD4 54 GND 20 NC 110 REQ64ON[3] 140

ATTN0[0] 80 GND 29 NC 112 RSVD 37

ATTN0[1] 98 GND 50 NC 114 RSVD 39

ATTN0[2] 124 GND 60 NC 139 RSVD 41

ATTN0[3] 1 GND 83 NC 141 RSVD 73

ATTN1[0] 81 GND 94 NC 143 RSVD 75

ATTN1[1] 99 GND 122 PCLK 19 RSVD 106

ATTN1[2] 125 GND 133 PRSNT1[0] 64 RSVD 108

ATTN1[3] 3 GND 138 PRSNT1[1] 90 SGNT 16

BUSON[0] 77 IDLEGNT 22 PRSNT1[2] 115 SLOTREQ64[0] 13

BUSON[1] 96 IDLEREQ 21 PRSNT1[3] 134 SLOTREQ64[1] 12

BUSON[2] 121 INTR 27 PRSNT2[0] 66 SLOTREQ64[2] 11

BUSON[3] 142 INTR 26 PRSNT2[1] 91 SLOTREQ64[3] 10

CLKON[0] 79 IRDY 24 PRSNT2[2] 117 SLOTRST[0] 68

CLKON[1] 97 M66EN[0] 82 PRSNT2[3] 135 SLOTRST[1] 92

CLKON[2] 123 M66EN[1] 101 PRST 17 SLOTRST[2] 118

CLKON[3] 144 M66EN[2] 126 PWRFAULT[0] 62 SLOTRST[3] 136

CS 43 M66EN[3] 5 PWRFAULT[1] 87 SMODE 30

DATA0/ADD5 53 NC 2 PWRFAULT[2] 111 SREQ 15

DATA1/ADD6 52 NC 4 PWRFAULT[3] 131 SYSM66EN 28

DATA2 51 NC 6 PWRGOOD[0] 63 V

CC

9

DATA3 49 NC 31 PWRGOOD[1] 88 V

CC

45

DATA4 48 NC 33 PWRGOOD[2] 113 V

CC

65

DATA5 47 NC 35 PWRGOOD[3] 132 V

CC

100

DATA6 46 NC 38 PWRON/OFF[0] 61 V

CC

116

DATA7 44 NC 40 PWRON/OFF[1] 86 V

CC5V

18

DETECT0[0] 84 NC 42 PWRON/OFF[2] 109 V

CC5V

32

DETECT0[1] 102 NC 67 PWRON/OFF[3] 130 V

CC5V

55

DETECT0[2] 127 NC 69 RD/SDA 34 V

CC5V

89

DETECT0[3] 7NC71 REQ64ON[0] 70 V

CC5V

128

DETECT1[0] 85 NC 74 REQ64ON[1] 93 V

CCP

25

DETECT1[1] 104 NC 76 REQ64ON[2] 119 WR/SCL 36

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

signal names by terminal number

Table 6. Signals Sorted Numerically by Terminal Number (144-Terminal Package)

NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME NO. TERMINAL NAME

1 ATTN0[3] 37 RSVD 73 RSVD 109 PWRON/OFF[2]

2 NC 38 NC 74 NC 110 NC

3 ATTN1[3] 39 RSVD 75 RSVD 111 PWRFAULT[2]

4 NC 40 NC 76 NC 112 NC

5 M66EN[3] 41 RSVD 77 BUSON[0] 113 PWRGOOD[2]

6 NC 42 NC 78 NC 114 NC

7 DETECT0[3] 43 CS 79 CLKON[0] 115 PRSNT1[2]

8 DETECT1[3] 44 DATA7 80 ATTN0[0] 116 V

CC

9 V

CC

45 V

CC

81 ATTN1[0] 117 PRSNT2[2]

10 SLOTREQ64[3] 46 DATA6 82 M66EN[0] 118 SLOTRST[2]

11 SLOTREQ64[2] 47 DATA5 83 GND 119 REQ64ON[2]

12 SLOTREQ64[1] 48 DATA4 84 DETECT0[0] 120 REQ64ON[2]

13 SLOTREQ64[0] 49 DATA3 85 DETECT1[0] 121 BUSON[2]

14 GND 50 GND 86 PWRON/OFF[1] 122 GND

15 SREQ 51 DATA2 87 PWRFAULT[1] 123 CLKON[2]

16 SGNT 52 DATA1/ADD6 88 PWRGOOD[1] 124 ATTN0[2]

17 PRST 53 DATA0/ADD5 89 V

CC5V

125 ATTN1[2]

18 V

CC5V

54 A4/ADD4 90 PRSNT1[1] 126 M66EN[2]

19 PCLK 55 V

CC5V

91 PRSNT2[1] 127 DETECT0[2]

20 GND 56 A3/ADD3 92 SLOTRST[1] 128 V

CC5V

21 IDLEREQ 57 A2/ADD2 93 REQ64ON[1] 129 DETECT1[2]

22 IDLEGNT 58 A1/ADD1 94 GND 130 PWRON/OFF[3]

23 FRAME 59 A0/ADD0 95 REQ64ON[1] 131 PWRFAULT[3]

24 IRDY 60 GND 96 BUSON[1] 132 PWRGOOD[3]

25 V

CCP

61 PWRON/OFF[0] 97 CLKON[1] 133 GND

26 INTR 62 PWRFAULT[0] 98 ATTN0[1] 134 PRSNT1[3]

27 INTR 63 PWRGOOD[0] 99 ATTN1[1] 135 PRSNT2[3]

28 SYSM66EN 64 PRSNT1[0] 100 V

CC

136 SLOTRST[3]

29 GND 65 V

CC

101 M66EN[1] 137 REQ64ON[3]

30 SMODE 66 PRSNT2[0] 102 DETECT0[1] 138 GND

31 NC 67 NC 103 NC 139 NC

32 V

CC5V

68 SLOTRST[0] 104 DETECT1[1] 140 REQ64ON[3]

33 NC 69 NC 105 NC 141 NC

34 RD/SDA 70 REQ64ON[0] 106 RSVD 142 BUSON[3]

35 NC 71 NC 107 NC 143 NC

36 WR/SCL 72 REQ64ON[0] 108 RSVD 144 CLKON[3]

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Terminal Functions

This section describes the HPC3130A terminal functions. The terminals are grouped in tables by function.

power supply terminal functions

TERMINAL

NAME

NO.

120

NO.

128

NO.

144

I/O FUNCTION

GND 11, 17, 26, 41, 51,

68, 79, 101, 112, 117

12, 18, 27, 44, 54,

73, 84, 108, 119, 124

14, 20, 29, 50, 60,

83, 94, 122, 133, 138

I Device ground terminals

V

CC

6, 36, 56, 85, 95 7, 39, 59, 90, 102 9, 45, 65, 100, 116 I 3.3-V power supply

V

CC5V

15, 28, 46, 74, 107 16, 29, 49, 79, 114 18, 32, 55, 89, 128 I 5-V clamp-rail voltage supply

V

CCP

22 23 25 I Clamp rail voltage for PCI signaling (5V or 3.3V)

control bus interface

TERMINAL

NAME

NO.

120

NO.

128

NO.

144

I/O FUNCTION

A2/ADD2

A1/ADD1

A0/ADD0

48

49

50

51

52

53

57

58

59

I

Parallel bus address. These terminals are address inputs in generic parallel bus cycles and are

only used when the SMODE is input low. These lower address terminals select one of the eight

registers for read/write access.

Serial bus address select. These terminals indicate the full serial bus address of the HPC3130A

when the SMODE is input high.

A4/ADD4

A3/ADD3

4547485054

56

I

Parallel bus address. These terminals are address inputs in generic parallel bus cycles, and are

only used when SMODE is input low. These upper address terminals select one of four hot-plug

slots supported by the HPC3130A.

Serial bus address select. These terminals indicate the full serial bus address of the HPC3130A

when the SMODE is input high.

CS 34 37 43 I

Chip selection. This active low input selects the HPC3130A chip as addressed in the current

generic parallel bus cycle. This chip input is only valid if the SMODE is input low. Multiple

HPC3130A chips may exist in a system with external logic driving this signal.

DATA1/ADD6

DATA0/ADD5434446475253

I/O

Parallel bus data. This bus is the data bus in generic parallel bus cycles and is selected when the

SMODE is input low. The data path is used during both read and write transactions to internal

registers when the parallel control bus interface is implemented.

Serial bus address selection. These terminals indicate the full serial bus address of the

HPC3130A when the SMODE is input high.

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

35

37

38

39

40

42

38

40

41

42

43

45

44

46

47

48

49

51

I/O

Parallel bus data. This bus is the data bus in generic parallel bus cycles and is selected when the

SMODE is input low. The data path is used during both read and write transactions to internal

registers when the parallel control bus interface is implemented.

RD/SDA 29 30 34 I/O

Read selection. This terminal indicates a register read cycle when the SMODE input is low and

the CS

terminal input is asserted. This is used to read an internal HPC3130A register.

Serial bus data. This terminal signals the serial bus data when the SMODE input is high. It is used

during internal register read and write transactions.

WR/SCL 30 31 36 I

Write selection. This terminal indicates a register write cycle when the SMODE input is low and

the CS

terminal input is asserted. This input is used to write to an internal HPC3130A register.

Serial bus clock. This terminal inputs serial bus clock in when the SMODE input is high. It is used

during internal register read and write transactions.

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Terminal Functions (Continued)

system interface

TERMINAL

NAME

NO.

120

NO.

128

NO.

144

I/O FUNCTION

FRAME 20 21 23 I

Frame. This input and the IRDY input indicate that the PCI bus is idle. When the HPC3130A

senses the PCI bus is idle after IDLEGNT

is low, a hot-plug slot can be connected to the PCI

bus. This input must be wired to a valid logic level if the bus idling procedure is not implemented.

IDLEGNT 19 20 22 I

Idle grant. This input indicates when the PCI bus is idled by the HOST-PCI bridge after a

request is made by IDLEREQ

. The protocol is identical to PCI request/grant. This input must be

wired to a valid logic level if the bus idling procedure is not implemented.

IDLEREQ 18 19 21 O

Idle request. This output is driven to request the HOST-PCI bridge to idle the PCI bus before

connecting a hot-plug slot. The protocol is identical to PCI request/grant. A pullup resistor must

be implemented on this terminal if the bus idling procedure is not implemented.

INTR 24 25 27 O

System interrupt. This output provides a system interrupt. The HPC3130A can be programmed

to assert this interrupt under various conditions, which may be serviced by the hot-plug service.

Furthermore, the event status/enable state is compliant with the

ACPI Specification

and, as a

result, supports ACPI control methods for switching the HPC3130A.

INTR 23 24 26 O

System interrupt. This open drain output provides a system interrupt. The HPC3130A can be

programmed to assert this interrupt under various conditions, which may be serviced by the

hot-plug. Furthermore, the event status/enable state is compliant with the

ACPI Specification

and, as a result, supports ACPI control methods for switching the HPC3130A.

IRDY 21 22 24 I

Initiator ready . This and the FRAME input indicate that the PCI bus is idle. When the HPC3130A

senses the PCI bus is idle after IDLEGNT

is low, a hot-plug slot may be connected to the PCI

bus. This input must be wired to a valid logic level if the bus idling procedure is not implemented.

PCLK 16 17 19 I

PCI clock input. These terminals provide the PCI clock to the HPC3130A, which uses it only for

activity indicator timing, IDLEREQ

/IDLEGNT protocol, and connection sequencing.

PRST 14 15 17 I

PCI reset. This signal provides the PCI reset to the HPC3130A. After a PCI reset, the

HPC3130A resides in a state where all slots are enabled, as in a non-hot-plug system. The

HPC3130A passes PCI resets from the host to all hot-plug slots.

SGNT 13 14 16 O

Secondary grant. This output provides a scheme to cascade a secondary HPC3130A device in

order to provide more than four slots. The SGNT

output from the primary HPC3130A is input to

the IDLEGNT

terminal for the secondary HPC3130A. After the secondary HPC3130A requests

the primary HPC3130A to idle the bus, the primary HPC3130A arbitrates for the bus using

IDLEREQ

. Once IDLEGNT is asserted, the primary HPC3130A asserts its SGNT output. This

indicates to the secondary HPC3130A device that it can connect to the bus.

SMODE 27 28 30 I

Serial bus mode. When this input is asserted high, the internal HPC3130A registers are

accessible through the serial bus interface; otherwise, they are accessed through the generic

parallel bus interface. This input selects the control bus interface.

SREQ 12 13 15 I

Secondary request. This input provides a scheme to cascade a second HPC3130A device in

order to provide more than four slots. The IDLEREQ

from the second HPC3130A device is

input to the SREQ

terminal of the primary HPC3130A. If the second HPC3130A device

arbitrates for the bus by asserting its IDLEREQ

output, this scheme causes the primary

HPC3130A to assert its IDLEREQ

. If cascading is not used, this input is pulled high.

SYSM66EN 25 26 28 I/O

PCI bus frequency indicator. This signal indicates the PCI clock frequency requirements of the

hot-plug slots, and must be tied to the system PCI bus M66EN signal. The output from this

terminal only changes state after a PCI reset and is only required in a 66-MHz system.

Loading...

Loading...