OKI MSM54V32128-60GS-K, MSM54V32126-50GS-K, MSM54V32126-60GS-K Datasheet

E2L0046-17-Y1 |

Preliminary |

|

¡ Semiconductor |

||

This version: Jan. 1998 |

||

Previous version: Dec. 1996 |

||

Semiconductor |

MSM54V32126/8 |

MSM54V32126/8

131,072-Word ´ 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO

DESCRIPTION

The MSM54V32126/8 is a new generation Graphics DRAM organized in a 131,072-word ´ 32-bit configuration. The technology used to fabricate the MSM54V32126/8 is OKI's CMOS silicon gate process technology. The device operates with a single 3.3 V power supply.

FEATURES

•131,072-word ´ 32-bit organization

•Single 3.3 V power supply, ±0.3 V tolerance

•Refresh: 512 cycles/8 ms

•Fast Page Mode with Extended Data Out (EDO)

•Write per bit (MSM54V32128 only)

•Byte write, Byte read

•RAS only refresh

•CAS before RAS refresh

•CAS before RAS self-refresh

•Hidden refresh

•Package:

64-pin 525 mil plastic SSOP (SSOP64-P-525-0.80-K) (Product : MSM54V32126-xxGS-K) (Product : MSM54V32128-xxGS-K) xx indicates speed rank.

PRODUCT FAMILY

Family |

Access Time (Max.) |

Cycle Time |

Power Dissipation |

|||||

|

|

|

|

|

|

|||

tRAC |

tAA |

tCAC |

tOEA |

(Min.) |

Operating (Max.) |

Standby (Max.) |

||

|

||||||||

MSM54V32126/8-50 |

50 ns |

25 ns |

15 ns |

15 ns |

110 ns |

504 mW |

3.1 mW |

|

|

|

|

|

|

|

|

||

MSM54V32126/8-60 |

60 ns |

30 ns |

18 ns |

18 ns |

130 ns |

486 mW |

||

|

||||||||

|

|

|

|

|

|

|

|

|

1/25

¡ Semiconductor MSM54V32126/8

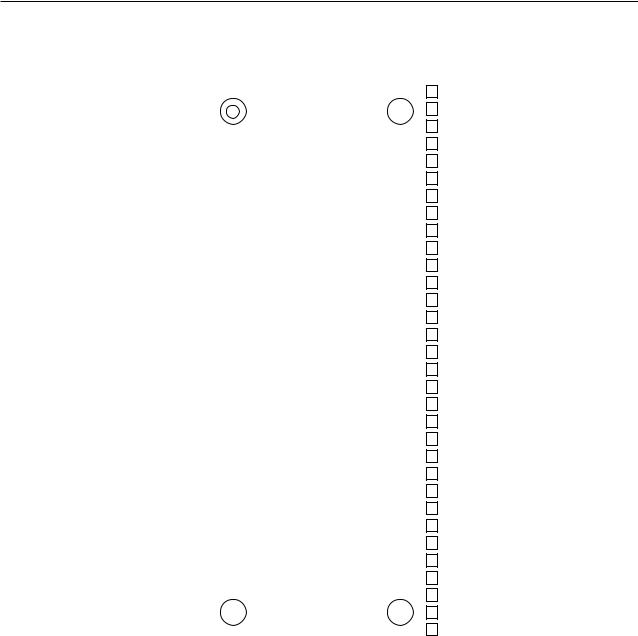

PIN CONFIGURATION (TOP VIEW)

VCC |

|

|

64 |

VSS |

1 |

|

|||

DQ0 |

|

|

63 |

DQ31 |

2 |

|

|||

DQ1 |

|

|

62 |

DQ30 |

3 |

|

|||

DQ2 |

|

|

61 |

DQ29 |

4 |

|

|||

DQ3 |

|

|

60 |

DQ28 |

5 |

|

|||

VCC |

|

|

59 |

VCC |

6 |

|

|||

DQ4 |

|

|

58 |

DQ27 |

7 |

|

|||

DQ5 |

|

|

57 |

DQ26 |

8 |

|

|||

DQ6 |

|

|

56 |

DQ25 |

9 |

|

|||

DQ7 |

|

|

55 |

DQ24 |

10 |

|

|||

VSS |

|

|

54 |

VSS |

11 |

|

|||

DQ8 |

|

|

53 |

DQ23 |

12 |

|

|||

DQ9 |

|

|

52 |

DQ22 |

13 |

|

|||

DQ10 |

|

|

51 |

DQ21 |

14 |

|

|||

DQ11 |

|

|

50 |

DQ20 |

15 |

|

|||

VCC |

|

|

49 |

VCC |

16 |

|

|||

DQ12 |

|

|

48 |

DQ19 |

17 |

|

|||

DQ13 |

|

|

47 |

DQ18 |

18 |

|

|||

DQ14 |

|

|

46 |

DQ17 |

19 |

|

|||

DQ15 |

|

|

45 |

DQ16 |

20 |

|

|||

VSS |

|

|

44 |

VSS |

21 |

|

|||

NC |

|

|

43 |

CAS1 |

22 |

|

|||

NC |

|

|

42 |

CAS2 |

23 |

|

|||

NC |

|

|

41 |

CAS3 |

24 |

|

|||

WB* / WE |

|

|

40 |

CAS4 |

25 |

|

|||

RAS |

|

|

39 |

OE |

26 |

|

|||

NC |

|

|

38 |

A8 |

27 |

|

|||

A0 |

|

|

37 |

A7 |

28 |

|

|||

A1 |

|

|

36 |

A6 |

29 |

|

|||

A2 |

|

|

35 |

A5 |

30 |

|

|||

A3 |

|

|

34 |

A4 |

31 |

|

|||

VCC |

|

|

33 |

VSS |

32 |

|

|||

|

|

|

|

|

|

|

|

64-Pin Plastic SSOP |

||

|

|

|

|

|

|

|

|

Pin Name |

|

Function |

|

|

|

|

|

|

|

|

|

A0 - A8 |

|

Address Input |

|

|

|

|

|

|

|

|

|

DQ0 - DQ31 |

|

Data Input / Data Output |

|

|

|

|

|

|

|

|

|

RAS |

|

Row Address Strobe |

|

|

|

|

|

|

|

|

|

CAS1 - CAS4 |

|

Column Address Strobe |

|

|

|

|

|

|

|

|

|

WB* / WE |

|

Write Per Bit* / Write Enable |

|

|

|

OE |

|

Output Enable |

|

|

|

|

|

|

|

|

|

VCC |

|

Power Supply (3.3 V) |

|

|

|

VSS |

|

Ground (0 V) |

|

|

|

NC |

|

No Connection |

|

|

|

|

|

|

|

Note: |

The same power supply voltage must be provided to every VCC pin, and the same GND |

||||

|

voltage level must be provided to every VSS pin. |

||||

*: |

MSM54V32128 only |

|

|

|

|

2/25

3/25

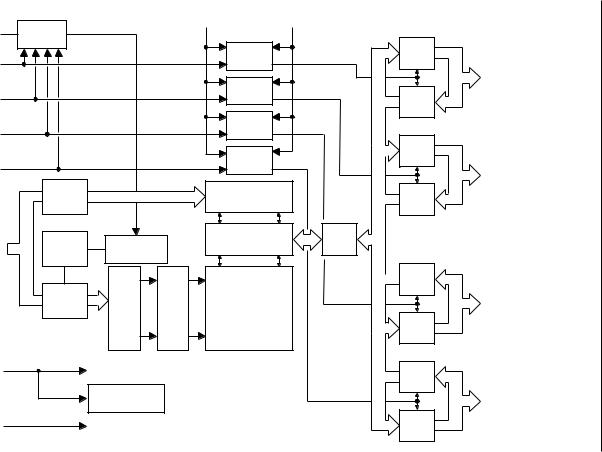

RAS

CAS1

CAS2

CAS3

CAS4

A0 - A8

VCC

VSS

Timing |

|

WB / WE |

OE |

|

|

|

||

|

|

|

|

|

|

|

||

Generator |

|

|

I/O |

|

|

|

Output |

|

|

|

|

|

|

|

8 |

||

|

|

|

|

Controller |

|

|

Buffers |

|

|

|

|

|

|

|

|

||

|

|

|

|

I/O |

|

|

|

Input |

|

|

|

|

Controller |

|

|

8 |

|

|

|

|

|

|

|

|

Buffers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O |

|

|

|

|

|

|

|

|

Controller |

|

|

|

|

|

|

|

|

I/O |

|

|

8 |

Output |

|

|

|

|

|

|

Buffers |

||

|

|

|

|

|

|

|

||

|

|

|

|

Controller |

|

|

|

|

8 |

Column |

|

8 |

Column Decoders |

|

|

|

Input |

Address |

|

|

|

8 |

||||

|

|

|

Buffers |

|||||

|

Buffers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Internal |

Refresh |

|

Sense Amps |

32 |

I/O |

32 |

|

|

|

Selector |

|

|||||

|

Address |

Control Clock |

|

|

|

|

|

|

|

Counter |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Input |

|

Row |

|

|

|

|

|

Buffers |

|

|

Row |

|

|

|

|

|

||

|

|

|

|

|

|

|

||

9 |

Address 9 |

Word |

Memory |

|

|

|

|

|

Deco- |

|

|

|

|

||||

|

Buffers |

Drivers |

Cells |

|

|

|

|

|

|

ders |

|

|

|

Output |

|||

|

|

|

|

|

|

8 |

||

|

|

|

|

|

|

|

Buffers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Input |

|

|

|

|

|

|

|

Buffers |

|

|

|

On-chip |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VBB Generator |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Output |

|

|

|

|

|

|

|

Buffers |

|

|

|

|

|

|

|

|

|

|

8

DQ0 - DQ7

8

8

DQ8 - DQ15

8

8

DQ16 - DQ23

8

8

DQ24 - DQ31

8

DIAGRAM BLOCK |

Semiconductor ¡ |

MSM54V32126/8

¡ Semiconductor MSM54V32126/8

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Parameter |

Symbol |

Rating |

Unit |

|

|

|

|

Voltage on Any Pin Relative to VSS |

VT |

–0.5 to 4.5 |

V |

Short Circuit Output Current |

IOS |

50 |

mA |

Power Dissipation |

PD |

1 |

W |

Operating Temperature |

Topr |

0 to 70 |

°C |

Storage Temperature |

Tstg |

–55 to 150 |

°C |

Recommended Operating Conditions |

|

|

|

(Ta = 0°C to 70°C) |

||

|

|

|

|

|

||

|

|

|

|

|

|

|

Parameter |

Symbol |

Min. |

Typ. |

Max. |

|

Unit |

|

|

|

|

|

|

|

Power Supply Voltage |

VCC |

3.0 |

3.3 |

3.6 |

|

V |

VSS |

0 |

0 |

0 |

|

V |

|

|

|

|||||

Input High Voltage |

VIH |

3.0 |

— |

3.6 |

|

V |

Input Low Voltage |

VIL |

–0.3 |

— |

0.3 |

|

V |

Capacitance |

|

|

(VCC = 3.3 V ±0.3 V, Ta = 25°C, f = 1 MHz) |

||

|

|

|

|||

Parameter |

Symbol |

Typ. |

|

Max. |

Unit |

|

|

|

|

|

|

Input Capacitance |

CIN |

— |

|

7 |

pF |

Input / Output Capacitance |

CIO |

— |

|

7 |

pF |

4/25

¡ Semiconductor |

|

|

|

|

|

|

|

MSM54V32126/8 |

|

||||

DC Characteristics |

|

|

|

|

(VCC = 3.3 V ±0.3 V, Ta = 0°C to 70°C) |

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

MSM54V32126/8 |

MSM54V32126/8 |

|

|

|

||||

|

Parameter |

|

Symbol |

Condition |

|

-50 |

|

-60 |

Unit |

Note |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min. |

|

Max. |

Min. |

|

Max. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output High Voltage |

|

VOH |

IOH = –0.1 mA |

2.0 |

|

VCC |

2.0 |

|

VCC |

V |

|

|

|

Output Low Voltage |

|

VOL |

IOL = 0.1 mA |

0 |

|

0.8 |

0 |

|

0.8 |

V |

|

|

|

|

|

|

0 V < VIN < VCC; |

|

|

|

|

|

|

|

|

|

|

Input Leakage Current |

|

ILI |

All other pins not |

–10 |

|

10 |

–10 |

|

10 |

mA |

|

|

|

|

|

|

under test = 0 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Leakage Current |

|

ILO |

0 V < VOUT < 3.6 V |

–10 |

|

10 |

–10 |

|

10 |

mA |

|

|

|

|

Output Disable |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Average Power |

|

|

RAS, CAS cycling, |

|

|

|

|

|

|

|

|

|

|

Supply Current |

|

ICC1 |

— |

|

130 |

— |

|

110 |

mA |

1, 2, 3 |

|

|

|

|

tRC = Min. |

|

|

|

||||||||

|

(Operating) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply |

|

ICC2 |

RAS, CAS ³ VCC – 0.2 V |

— |

|

850 |

— |

|

850 |

mA |

|

|

|

Current (Standby) |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Average Power |

|

|

RAS = cycling, |

|

|

|

|

|

|

|

|

|

|

Supply Current |

|

ICC3 |

CAS = VIH, |

— |

|

130 |

— |

|

110 |

mA |

1, 2, 3 |

|

|

(RAS Only Refresh) |

|

|

tRC = Min. |

|

|

|

|

|

|

|

|

|

|

Average Power |

|

|

RAS = VIL, |

|

|

|

|

|

|

|

|

|

|

Supply Current |

|

ICC4 |

CAS cycling, |

— |

|

140 |

— |

|

135 |

mA |

1, 2, 4 |

|

|

(Fast Page Mode) |

|

|

tHPC = Min. |

|

|

|

|

|

|

|

|

|

|

Average Power |

|

|

RAS = cycling, |

|

|

|

|

|

|

|

|

|

|

Supply Current |

|

ICC5 |

— |

|

130 |

— |

|

110 |

mA |

1, 2, 4 |

|

|

|

|

CAS before RAS |

|

|

|

||||||||

|

(CAS before RAS Refresh) |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Average Power Supply |

|

|

RAS = VIL, |

|

|

|

|

|

|

|

|

|

|

Current (CAS before RAS |

|

ICCS |

— |

|

950 |

— |

|

950 |

mA |

1, 2 |

|

|

|

|

CAS = VIL |

|

|

|

||||||||

|

Self-Refresh) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes: 1. Specified values are obtained with minimum cycle time.

2.ICC is dependent on output loading. Specified values are obtained with the output open.

3.Address can be changed once or less while RAS = VIL.

4.Address can be changed once or less while CAS = VIH.

5/25

¡ Semiconductor |

|

|

|

|

|

MSM54V32126/8 |

|||||

AC Characteristics (1/2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(VCC = 3.3 V ±0.3 V, Ta = 0°C to 70°C) Note 1, 2, 3 |

||||||||

|

|

|

|

MSM54V32126/8 |

MSM54V32126/8 |

|

|

||||

|

Parameter |

Symbol |

|

|

-50 |

-60 |

|

Unit |

Note |

||

|

|

|

|

Min. |

|

Max. |

Min. |

|

Max. |

|

|

|

Random Read or Write Cycle Time |

tRC |

|

110 |

|

— |

130 |

|

— |

ns |

|

|

Read Modify Write Cycle |

tRWC |

|

145 |

|

— |

170 |

|

— |

ns |

|

|

Fast Page Mode Cycle Time |

tHPC |

|

22 |

|

— |

24 |

|

— |

ns |

|

|

Fast Page Mode Read-Modify-Write Cycle Time |

tPRWC |

|

70 |

|

— |

80 |

|

— |

ns |

|

|

Access Time from RAS |

tRAC |

|

— |

|

50 |

— |

|

60 |

ns |

4, 9, 10 |

|

Access Time from Column Address |

tAA |

|

— |

|

25 |

— |

|

30 |

ns |

4, 10 |

|

Access Time from CAS |

tCAC |

|

— |

|

15 |

— |

|

18 |

ns |

4, 9 |

|

Access Time from CAS Precharge |

tCPA |

|

— |

|

30 |

— |

|

35 |

ns |

4, 13 |

|

Output Buffer Turn-off Delay Time from RAS |

tREZ |

|

3 |

|

20 |

3 |

|

20 |

ns |

5 |

|

Output Buffer Turn-off Delay Time from CAS |

tCEZ |

|

3 |

|

20 |

3 |

|

20 |

ns |

5 |

|

Transition Time (Rise and Fall) |

tT |

|

3 |

|

35 |

3 |

|

35 |

ns |

3 |

|

RAS Precharge Time |

tRP |

|

54 |

|

— |

64 |

|

— |

ns |

|

|

RAS Pulse Width |

tRAS |

|

50 |

|

10k |

60 |

|

10k |

ns |

|

|

RAS Pulse Width (Hyper Page Mode Only) |

tRASP |

|

50 |

|

100k |

60 |

|

100k |

ns |

|

|

RAS Hold Time |

tRSH |

|

14 |

|

— |

14 |

|

— |

ns |

|

|

CAS Hold Time |

tCSH |

|

50 |

|

— |

60 |

|

— |

ns |

|

|

CAS Pulse Width |

tCAS |

|

8 |

|

10k |

9 |

|

10k |

ns |

|

|

RAS to CAS Delay Time |

tRCD |

|

20 |

|

35 |

20 |

|

42 |

ns |

9 |

|

RAS to Column Address Delay Time |

tRAD |

|

15 |

|

25 |

15 |

|

30 |

ns |

10 |

|

Column Address to RAS Lead Time |

tRAL |

|

24 |

|

— |

28 |

|

— |

ns |

|

|

CAS to RAS Precharge Time |

tCRP |

|

6 |

|

— |

8 |

|

— |

ns |

13 |

|

CAS Precharge Time (Hyper Page Mode) |

tCP |

|

8 |

|

— |

9 |

|

— |

ns |

15 |

|

Row Address Set-up Time |

tASR |

|

0 |

|

— |

0 |

|

— |

ns |

|

|

Row Address Hold Time |

tRAH |

|

7 |

|

— |

9 |

|

— |

ns |

|

|

Column Address Set-up Time |

tASC |

|

0 |

|

— |

0 |

|

— |

ns |

12 |

|

Column Address Hold Time |

tCAH |

|

8 |

|

— |

10 |

|

— |

ns |

12 |

|

Column Address Hold Time referenced to RAS |

tAR |

|

35 |

|

— |

40 |

|

— |

ns |

|

|

Read Command Set-up Time |

tRCS |

|

0 |

|

— |

0 |

|

— |

ns |

12 |

|

Read Command Hold Time |

tRCH |

|

0 |

|

— |

0 |

|

— |

ns |

6, 12 |

|

Read Command Hold Time referenced to RAS |

tRRH |

|

0 |

|

— |

0 |

|

— |

ns |

6 |

|

CAS "H" to RAS "H" Lead Time |

tCRL |

|

0 |

|

— |

0 |

|

— |

ns |

|

|

RAS "H" to CAS "H" Lead Time |

tRCL |

|

0 |

|

— |

0 |

|

— |

ns |

|

|

Data Output Hold after CAS Low |

tDOH |

|

3 |

|

— |

3 |

|

— |

ns |

11 |

|

Write Command Set-up Time |

tWCS |

|

0 |

|

— |

0 |

|

— |

ns |

8, 12 |

|

Write Command Hold Time |

tWCH |

|

8 |

|

— |

10 |

|

— |

ns |

12 |

6/25

¡ Semiconductor |

|

|

|

|

|

MSM54V32126/8 |

||||

AC Characteristics (2/2) |

|

|

|

|

|

|

|

|

|

|

|

|

(VCC = 3.3 V ±0.3 V, Ta = 0°C to 70°C) Note 1, 2, 3 |

||||||||

|

|

|

MSM54V32126/8 |

MSM54V32126/8 |

|

|

||||

Parameter |

Symbol |

|

|

-50 |

-60 |

|

Unit |

Note |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min. |

|

Max. |

Min. |

|

Max. |

|

|

Write Command Hold Time referenced to RAS |

tWCR |

|

35 |

|

— |

40 |

|

— |

ns |

|

Write Command Pulse Width |

tWP |

|

9 |

|

— |

10 |

|

— |

ns |

|

Write Command to RAS Lead Time |

tRWL |

|

9 |

|

— |

10 |

|

— |

ns |

|

Write Command to CAS Lead Time |

tCWL |

|

9 |

|

— |

10 |

|

— |

ns |

14 |

Output Buffer Turn-off Delay Time from WE |

tWEZ |

|

3 |

|

20 |

3 |

|

20 |

ns |

5 |

Data Set-up Time |

tDS |

|

0 |

|

— |

0 |

|

— |

ns |

7, 12 |

Data Hold Time |

tDH |

|

8 |

|

— |

10 |

|

— |

ns |

7, 12 |

Data Hold Time referenced to RAS |

tDHR |

|

35 |

|

— |

40 |

|

— |

ns |

|

OE to Data-in Delay Time |

tOED |

|

12 |

|

— |

12 |

|

— |

ns |

|

RAS to WE Delay Time |

tRWD |

|

70 |

|

— |

80 |

|

— |

ns |

8 |

Column Address to WE Delay Time |

tAWD |

|

45 |

|

— |

50 |

|

— |

ns |

8 |

CAS to WE Delay Time |

tCWD |

|

35 |

|

— |

40 |

|

— |

ns |

8 |

Data to CAS Delay Time |

tDZC |

|

0 |

|

— |

0 |

|

— |

ns |

|

Data to OE Delay Time |

tDZO |

|

0 |

|

— |

0 |

|

— |

ns |

|

Access Time from OE |

tOEA |

|

— |

|

15 |

— |

|

18 |

ns |

|

Output Buffer Turn-off Delay Time from OE |

tOEZ |

|

3 |

|

20 |

3 |

|

20 |

ns |

5 |

OE Command Hold Time |

tOEH |

|

9 |

|

— |

10 |

|

— |

ns |

|

RAS Hold Time referenced to OE |

tROH |

|

10 |

|

— |

12 |

|

— |

ns |

|

OE "L" to CAS "H" Lead Time |

tOCH |

|

10 |

|

— |

10 |

|

— |

ns |

|

CAS "H" to OE "L" Lead Time |

tCHO |

|

10 |

|

— |

10 |

|

— |

ns |

|

High-Z Command Pulse Width |

tOEP |

|

10 |

|

— |

12 |

|

— |

ns |

|

WB/WE Pulse Width (Output Disable) |

tWPE |

|

10 |

|

— |

12 |

|

— |

ns |

|

CAS Set-up Time for CAS before RAS Cycle |

tCSR |

|

8 |

|

— |

10 |

|

— |

ns |

12 |

CAS Hold Time for CAS before RAS Cycle |

tCHR |

|

8 |

|

— |

10 |

|

— |

ns |

13 |

RAS Precharge to CAS Active Time |

tRPC |

|

10 |

|

— |

10 |

|

— |

ns |

12 |

CAS Precharge Time (Refresh Counter Test) |

tCPT |

|

25 |

|

— |

30 |

|

— |

ns |

15 |

Refresh Period |

tREF |

|

— |

|

8 |

— |

|

8 |

ms |

|

WB Set-up Time |

tWSR |

|

0 |

|

— |

0 |

|

— |

ns |

16 |

WB Hold Time |

tRWH |

|

7 |

|

— |

8 |

|

— |

ns |

16 |

Write-Per-Bit Mask Data Set-up Time |

tMS |

|

0 |

|

— |

0 |

|

— |

ns |

16 |

Write-Per-Bit Mask Data Hold Time |

tMH |

|

8 |

|

— |

10 |

|

— |

ns |

16 |

RAS Pulse Width (CAS before RAS Self-Refresh) |

tRASS |

|

100 |

|

— |

100 |

|

— |

ms |

|

RAS Precharge Time (CAS before RAS Self-Refresh) |

tRPS |

|

110 |

|

— |

130 |

|

— |

ns |

|

CAS Hold Time (CAS before RAS Self-Refresh) |

tCHS |

|

0 |

|

— |

0 |

|

— |

ns |

|

7/25

¡ Semiconductor MSM54V32126/8

Notes: 1. An initial pause of 200 ms is required after power-up followed by any 8 RAS cycles (Example : RAS only refresh) before proper device operation is achieved. In case of usinginternalrefreshcounter,aminimumof8CASbeforeRAScyclesinsteadof8RAS cycles are required.

2.The AC characteristics assume at tT = 3 ns.

3.VIH (Min.) and VIL (Max.) are reference levels for measuring timing of input signals. Also,transitiontimesaremeasuredbetweenVIH andVIL.InputlevelsattheACtesting are 3.0 V/0 V.

4.Data outputs are measured with a load of 30 pF. DOUT reference levels : VOH/VOL = 2.0 V/0.8 V.

5.tREZ (Max.), tCEZ (Max.), tWEZ (Max.) and tOEZ (Max.) define the time at which the outputs achieve the open circuit condition and are not referenced to output voltage levels. This parameter is sampled and not 100% tested.

6.Either tRCH or tRRH must be satisfied for a read cycle.

7.These parameters are referenced to CAS leading edge of early write cycles and toWE leading edge in OE controlled write cycles and read modify write cycles.

8.tWCS, tRWD, tCWD and tAWD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If tWCS ≥ tWCS (Min.), the cycle is an early write cycle and the data out pin will remain open circuit throughout the entire cycle; If tRWD ≥ tRWD (Min.), tCWD ≥ tCWD (Min.) and tAWD ≥ tAWD (Min.), the cycle is a read modify write cycle and the data out will contain data read from the selected cell: If neither of the above sets of conditions is satisfied, the condition of the data out is indeterminate.

9.Operation within the tRCD (Max.) limit ensures that tRAC (Max.) can be met. tRCD (Max.) is specified as a reference point only: If tRCD is greater than the specified tRCD (Max.) limit, then access time is controlled by tCAC.

10.Operation within the tRAD (Max.) limit ensures that tRAC (Max.) can be met. tRAD (Max.) is specified as a reference point only: If tRAD is greater than the specified tRAD (Max.) limit, then access time is controlled by tAA.

11.This is guaranteed by design. (tDOH = tCAC - output transition time) This parameter is not 100% tested.

12.These parameters are determined by the earliest falling edge of CAS1, CAS2, CAS3, or

CAS4.

13.These parameters are determined by the latest rising edge of CAS1, CAS2, CAS3, or

CAS4.

14.tCWL should be satisfied by all CASes.

15.tCP and tCPT are determined by the time that all CASes are high.

16.Only MSM54V32128.

8/25

Loading...

Loading...