OKI MSM64P155-003GS-BK, MSM64P155-xxxGS-BK, MSM64P155L-002GS-BK, MSM64P155-001GS-BK, MSM64P155L-xxxGS-BK Datasheet

...

E2E0050-18-95 |

Preliminary |

¡ Semiconductor |

|

Semiconductor |

This version: Sep. 1998 |

MSM64P155/64P155L |

MSM64P155/64P155L

4-Bit Microcontroller with Built-in LCD Driver and Melody Circuit

GENERAL DESCRIPTION

The MSM64P155 (1.5 V)/64P155L (3.0 V) is a one-time-programmable ROM version product, which has one-time PROM (OTP) as internal program memory. On the other hand, the MSM64155 is a mask ROM-version product, which has mask ROM as internal program memory. Unlike the mask ROM-version MSM64155 which has a P-well CMOS structure, the MSM64P155/ 64P155L has been fabricated with the N-well CMOS-structured EPROM process technology.

Therefore, the MSM64P155/64P155L differs from the MSM64155 in the polarity of the power supply for LCD bias generation and in the external circuit structure.

Unlike the mask ROM-version product, the MSM64P155/64P155L cannot be supplied in the form of a chip. The MSM64P155/64P155L is an OTP-version product used to evaluate an application program.

The MSM64P155/64P155L has two operation modes, microcontroller operation mode and PROM mode. The microcontroller operation mode is used to operate the MSM64P155/64P155L like a mask ROM-version product and the PROM mode is used to program or read the PROM.

FEATURES

• Operating range |

|

Operating voltage (mask option) |

: 1.5 V/3.0 V |

Operating frequency |

: 32.768 kHz crystal oscillation |

|

Approx. 32 kHz RC oscillation |

• Minimum instruction execution time |

: 91 ms |

• General memory space |

: 4064 bytes (PROM) |

• Local memory space |

: 256 nibbles |

• LCD driver |

: 64 |

|

Common driver ´ 4 |

|

Segment driver ´ 60 |

|

1/4 duty, 1/3 bias; 240 segments (60 ´ 4) |

|

1/3 duty, 1/3 bias; 180 segments (60 ´ 3) |

• I/O port |

: 2 ports ´ 4 bits (open-drain output/CMOS output |

Input-output port |

|

|

selectable; pull-down resistor input/high-impedance |

|

input selectable) |

Input port |

: 1 port ´ 2 bits (pull-down resistor input/high-impedance |

|

input selectable) |

|

1 port ´ 4 bits (pull-down resistor input/high-impedance |

|

input selectable) |

Output port |

: 1 port ´ 4 bits (CMOS output) |

• Event counter |

: 1 channel |

• Melody output |

: 2 |

• Capture circuits |

: 2 channels |

|

256 Hz, 128 Hz, 64 Hz, 32 Hz |

1/29

¡ Semiconductor |

MSM64P155/64P155L |

• Interrupt sources |

: 10 sources |

|

External 4, time base 4, melody 2 |

|

(When TST3 = "1", six time base sources) |

•Clock generation circuit (mask option) : Crystal/RC oscillation

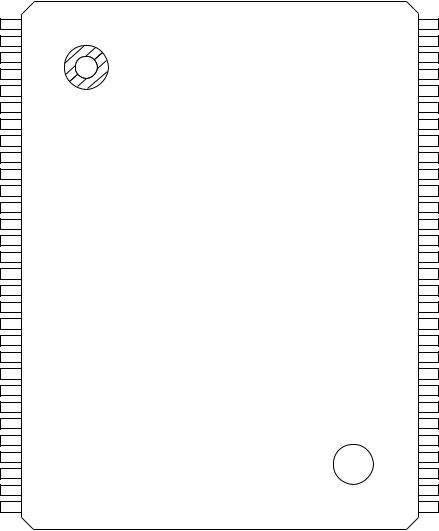

•Package:

100-pin plastic QFP (QFP100-P-1420-0.65-BK) Product name :

MSM64P155-001GS-BK (crystal oscillation, 1.5 V, blanked PROM) MSM64P155L-002GS-BK (crystal oscillation, 3.0 V, blanked PROM) MSM64P155-003GS-BK (RC oscillation, 1.5 V, blanked PROM) MSM64P155L-004GS-BK (RC oscillation, 3.0 V, blanked PROM) MSM64P155-xxxGS-BK (crystal/RC oscillation, 1.5 V, written PROM) MSM64P155L-xxxGS-BK (crystal/RC oscillation, 3.0 V, written PROM) xxx indicates a code number.

2/29

¡ Semiconductor |

MSM64P155/64P155L |

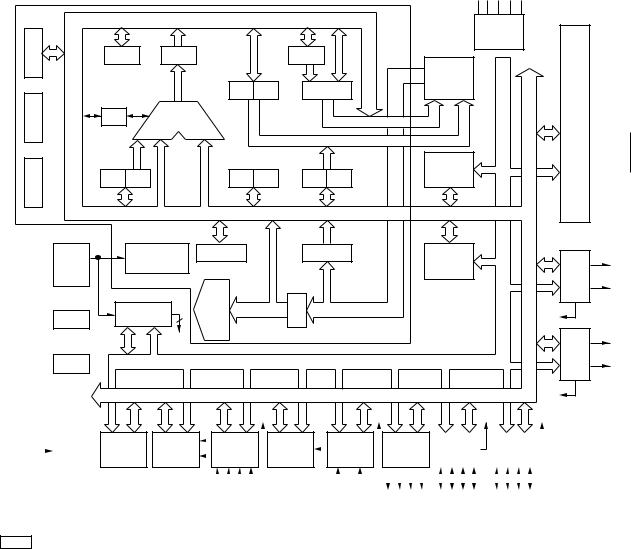

BLOCK DIAGRAM

MIEF HALT BSR

TR2 |

TR0 |

|

|

TR1 |

|

|

|

(4) |

|

|

|

ROM |

|

|

PCM |

PCL |

PCH |

4064B |

||

|

|

|

||||

C |

ALU |

|

|

|

A8 to A11 |

|

|

|

|

|

|

||

|

|

|

|

A7 to A0 |

|

|

|

(4) |

(4) |

|

|

RAM |

|

B A |

L |

X Y |

256N |

|||

|

H |

VVV C2C1DD3DD2DD1

BIAS

ADDRESSPORT

COM1

COM1

COM2

COM2

COM3

COM3

COM4

COM4

LCD  SEG0

SEG0

SEG59

SEG59

OSC0

CLK

OSC1

RESET  RST

RST

TST1  TST2

TST2  TST TST3

TST TST3

TIMING

CONTROLLER

TBC 4

INT

|

DB7 to DB0 |

(8) |

|

|

SP |

ROMR |

|

INTC |

MD0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

MD0 |

IR DECODER |

IR |

|

|

MD0 |

(8) |

|

INT |

||

|

|

|

||

|

|

|

|

|

|

|

|

|

MD1 |

|

PORT ADDRESS |

|

|

MD1 |

|

|

|

MD1 |

|

|

|

|

|

|

|

DB7 to DB0 |

|

|

INT |

|

INT |

INT |

INT |

INT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

BUP |

CAPR |

|

|

PORT2 |

|

EVENT |

|

PORT3 |

|

|

PORT4 |

|

PORT6 |

|

|

PORT7 |

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P2.0 |

P2.1 |

P2.2 |

P2.3 |

|

|

|

P3.0 |

P3.1 |

|

P4.0 |

P4.1 |

P4.2 |

P4.3 |

P6.0 |

P6.1 |

P6.2 |

P6.3 |

|

P7.0 |

P7.1 |

P7.2 |

P7.3 |

|

||||||||||||||||||

is the CPU core (nx-4/20).

3/29

¡ Semiconductor |

MSM64P155/64P155L |

PIN CONFIGURATION (TOP VIEW)

RESET 1 OSC0 2

OSC1 3

VPP 4

P2.3 5

P2.2 6

P2.1 7

P2.0 8

P3.1 9

P3.0 10

P4.3 11

P4.2 12

P4.1 13

P4.0 14

P6.3 15

P6.2 16

P6.1 17

P6.0 18

P7.3 19

P7.2 20

P7.1 21

P7.0 22

VSS 23

MD0 24

MD0 25

MD1 26

MD1 27

TST3 28

TST2 29

TST1 30

V |

V |

V |

C1 |

C2 |

COM1 |

COM2 |

COM3 |

COM4 |

SEG0 |

SEG1 |

SEG2 |

SEG3 |

|

SEG4 |

|

SEG5 |

SEG6 |

SEG7 |

|

SEG8 |

|

SEG9 |

|

SEG10 |

||||||||||||||

DD1 |

DD2 |

DD3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

100 |

|

99 |

|

98 |

|

97 |

|

96 |

|

95 |

|

94 |

|

93 |

|

92 |

|

91 |

|

90 |

|

89 |

|

88 |

|

87 |

|

86 |

|

85 |

|

84 |

|

83 |

|

82 |

|

81 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

32 |

|

33 |

|

34 |

|

35 |

|

36 |

|

37 |

|

38 |

|

39 |

|

40 |

|

41 |

|

42 |

|

43 |

|

44 |

|

45 |

|

46 |

|

47 |

|

48 |

|

49 |

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEG59 |

SEG58 |

SEG57 |

SEG56 |

SEG55 |

SEG54 |

SEG53 |

SEG52 |

SEG51 |

(NC) |

SEG50 |

SEG49 |

SEG48 |

|

SEG47 |

|

SEG46 |

SEG45 |

SEG44 |

|

SEG43 |

|

SEG42 |

|

SEG41 |

||||||||||||||

100-Pin Plastic QFP

Note: Pins marked as (NC) are no-connection pins which are left open.

80 SEG11

79 SEG12

78 SEG13

77 SEG14

76 SEG15

75 SEG16

74 SEG17

73 SEG18

72 SEG19

71 SEG20

70 SEG21

69 SEG22

68 SEG23

67 SEG24

66 SEG25

65 SEG26

64 SEG27

63 SEG28

62 SEG29

61 SEG30

60 SEG31

59 SEG32

58 SEG33

57 SEG34

56 SEG35

55 SEG36

54 SEG37

53 SEG38

52 SEG39

51 SEG40

4/29

¡ Semiconductor MSM64P155/64P155L

PIN DESCRIPTIONS

Basic Functions

Function |

Pin |

Symbol |

Type |

Description |

|

|

|

|

|

Power |

23 |

VSS |

— |

Digital supply voltage (0 V) |

Supply |

100 |

VDD1 |

— |

Digital positive power supply (1.5 V spec.) |

|

||||

|

|

|

|

Bias output for LCD driver (3.0 V spec.) |

|

|

|

|

|

|

99 |

VDD2 |

— |

Digital positive power supply (3.0 V spec.) |

|

|

|

|

Bias output for LCD driver (1.5 V spec.) |

|

|

|

|

|

|

98 |

VDD3 |

— |

Bias output for LCD driver (+4.5 V) |

|

97 |

C1 |

— |

Pins for connecting a capacitor for generating LCD driving bias |

|

96 |

C2 |

— |

|

|

4 |

VPP |

— |

Positive power supply for writing programming data to PROM |

|

|

|

|

(+12.5 V) |

|

|

|

|

|

Oscillation |

2 |

OSC0 |

I |

Clock oscillation pins: |

|

|

|

|

Either a crystal (32.768 kHz) and a capacitor (10 to 30 pF) are |

|

|

|

|

connected to these pins or a resistor (1 MW) is. |

|

3 |

OSC1 |

O |

|

|

|

|

|

|

Test |

30 |

TST1 |

I |

Input pins for test: |

|

29 |

TST2 |

I |

These pins are internally pulled down to VSS. |

|

28 |

TST3 |

I |

When this pin is set to "H" level, the 256 Hz and 4 Hz interrupts are |

|

|

|

|

enabled, and then the MSM64P155 can be used as an OTP version |

|

|

|

|

of the MSM64152A, MSM64153A, and MSM64158A. |

|

|

|

|

|

RESET |

1 |

RESET |

I |

System reset input pin : |

|

|

|

|

Setting this pin to "H" level puts this device into a reset state. |

|

|

|

|

Then, setting this pin to "L" level starts executing an instruction from |

|

|

|

|

address 000H. |

|

|

|

|

This pin is internally connected to VSS through a pull-down resistor. |

5/29

¡ Semiconductor |

|

MSM64P155/64P155L |

||||

Basic Functions (continued) |

|

|

|

|||

|

|

|

|

|

|

|

Function |

Pin |

Symbol |

|

Type |

Description |

|

|

|

|

|

|

|

|

Ports |

8 |

P2.0 |

|

I |

4-bit input port (port 2) : |

|

|

|

|

|

|

Select between pull-down resistor input and high impedance input |

|

|

7 |

P2.1 |

|

|

||

|

|

|

for each bit with the port 2 control register (P2CON). |

|||

|

6 |

P2.2 |

|

|

||

|

|

|

When configured for secondary functions, an external interrupt and |

|||

|

5 |

P2.3 |

|

|

||

|

|

|

capture circuit trigger input are allocated. |

|||

|

|

|

|

|

If P2.0 to P2.3 are set to "H" level, the device enters system reset |

|

|

|

|

|

|

mode. |

|

|

10 |

P3.0 |

|

I |

2-bit input port (port 3) : |

|

|

|

|

|

|

Select between pull-down resistor input and high impedance input |

|

|

9 |

P3.1 |

|

|

||

|

|

|

with the port 3 control register (P3CON). |

|||

|

|

|

|

|

||

|

|

|

|

|

When configured for a secondary function, an external interrupt is |

|

|

|

|

|

|

allocated to P3.0 and an event counter is allocated to P3.1. |

|

|

14 |

P4.0 |

|

O |

4-bit output port (port 4) : |

|

|

13 |

P4.1 |

|

|

4-bit CMOS output port. |

|

|

|

|

|

|

||

|

12 |

P4.2 |

|

|

|

|

|

11 |

P4.3 |

|

|

|

|

|

18 |

P6.0 |

|

I/O |

4-bit input-output port (port 6) : |

|

|

|

|

|

|

Select between input and output, between pull-down resistor input |

|

|

17 |

P6.1 |

|

|

||

|

|

|

and high impedance input, and between open-drain output and CMOS |

|||

|

16 |

P6.2 |

|

|

||

|

|

|

output with the port 6 control register (P6CON). When configured |

|||

|

15 |

P6.3 |

|

|

for a secondary function, an external interrupt is allocated. |

|

|

22 |

P7.0 |

|

I/O |

4-bit input-output port (port 7) : |

|

|

|

|

|

|

Select between input and output, between pull-down resistor input |

|

|

21 |

P7.1 |

|

|

||

|

|

|

and high impedance input, and between open-drain output and CMOS |

|||

|

20 |

P7.2 |

|

|

||

|

|

|

output with the port 7 control register (P7CON). When configured for |

|||

|

19 |

P7.3 |

|

|

a secondary function, an external interrupt is allocated. |

|

Melody |

25 |

MD0 |

|

O |

Output pin of melody driver 0. |

|

Drivers |

24 |

MD0 |

|

O |

Inverted output pin of MD0 output. |

|

|

|

|

|

|

|

|

|

26 |

MD1 |

|

O |

Output pin of melody driver 1. |

|

|

27 |

MD1 |

|

O |

Inverted output pin of MD1 output. |

|

LCD |

95 |

COM1 |

|

O |

LCD common signal output pins. |

|

Drivers |

94 |

COM2 |

|

O |

|

|

|

93 |

COM3 |

|

O |

|

|

|

92 |

COM4 |

|

O |

|

|

6/29

¡ Semiconductor |

|

MSM64P155/64P155L |

|||

Basic Functions (continued) |

|

|

|||

|

|

|

|

|

|

Function |

Pin |

Symbol |

|

Type |

Description |

|

|

|

|

|

|

LCD |

91 |

SEG0 |

|

O |

LCD segment signal output pins. |

Drivers |

|

|

|

|

|

90 |

SEG1 |

|

O |

|

|

|

|

|

|||

|

89 |

SEG2 |

|

O |

|

|

|

|

|

|

|

|

88 |

SEG3 |

|

O |

|

|

87 |

SEG4 |

|

O |

|

|

|

|

|

|

|

|

86 |

SEG5 |

|

O |

|

|

85 |

SEG6 |

|

O |

|

|

|

|

|

|

|

|

84 |

SEG7 |

|

O |

|

|

83 |

SEG8 |

|

O |

|

|

|

|

|

|

|

|

82 |

SEG9 |

|

O |

|

|

|

|

|

|

|

|

81 |

SEG10 |

|

O |

|

|

|

|

|

|

|

|

80 |

SEG11 |

|

O |

|

|

|

|

|

|

|

|

79 |

SEG12 |

|

O |

|

|

|

|

|

|

|

|

78 |

SEG13 |

|

O |

|

|

77 |

SEG14 |

|

O |

|

|

|

|

|

|

|

|

76 |

SEG15 |

|

O |

|

|

|

|

|

|

|

|

75 |

SEG16 |

|

O |

|

|

|

|

|

|

|

|

74 |

SEG17 |

|

O |

|

|

|

|

|

|

|

|

73 |

SEG18 |

|

O |

|

|

72 |

SEG19 |

|

O |

|

|

|

|

|

|

|

|

71 |

SEG20 |

|

O |

|

|

|

|

|

|

|

|

70 |

SEG21 |

|

O |

|

|

|

|

|

|

|

|

69 |

SEG22 |

|

O |

|

|

|

|

|

|

|

|

68 |

SEG23 |

|

O |

|

|

|

|

|

|

|

|

67 |

SEG24 |

|

O |

|

|

|

|

|

|

|

|

66 |

SEG25 |

|

O |

|

|

|

|

|

|

|

|

65 |

SEG26 |

|

O |

|

|

|

|

|

|

|

|

64 |

SEG27 |

|

O |

|

|

|

|

|

|

|

|

63 |

SEG28 |

|

O |

|

|

|

|

|

|

|

|

62 |

SEG29 |

|

O |

|

|

|

|

|

|

|

|

61 |

SEG30 |

|

O |

|

|

60 |

SEG31 |

|

O |

|

|

|

|

|

|

|

|

59 |

SEG32 |

|

O |

|

|

|

|

|

|

|

|

58 |

SEG33 |

|

O |

|

|

|

|

|

|

|

|

57 |

SEG34 |

|

O |

|

|

|

|

|

|

|

|

56 |

SEG35 |

|

O |

|

|

|

|

|

|

|

|

55 |

SEG36 |

|

O |

|

|

54 |

SEG37 |

|

O |

|

|

|

|

|

|

|

|

53 |

SEG38 |

|

O |

|

|

|

|

|

|

|

|

52 |

SEG39 |

|

O |

|

7/29

¡ Semiconductor |

|

MSM64P155/64P155L |

|

||||

Basic Functions (continued) |

|

|

|

||||

|

|

|

|

|

|

|

|

|

Function |

Pin |

Symbol |

|

Type |

Description |

|

|

|

|

|

|

|

|

|

|

LCD |

51 |

SEG40 |

|

O |

LCD segment signal output pins. |

|

|

Drivers |

50 |

SEG41 |

|

O |

|

|

|

|

|

|

|

|||

|

|

49 |

SEG42 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

48 |

SEG43 |

|

O |

|

|

|

|

47 |

SEG44 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

46 |

SEG45 |

|

O |

|

|

|

|

45 |

SEG46 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

44 |

SEG47 |

|

O |

|

|

|

|

43 |

SEG48 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

42 |

SEG49 |

|

O |

|

|

|

|

41 |

SEG50 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

39 |

SEG51 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

38 |

SEG52 |

|

O |

|

|

|

|

37 |

SEG53 |

|

O |

|

|

|

|

36 |

SEG54 |

|

O |

|

|

|

|

35 |

SEG55 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

34 |

SEG56 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

33 |

SEG57 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

32 |

SEG58 |

|

O |

|

|

|

|

|

|

|

|

|

|

|

|

31 |

SEG59 |

|

O |

|

|

8/29

|

¡ Semiconductor |

|

MSM64P155/64P155L |

|||

|

Secondary Functions |

|

|

|

||

|

|

|

|

|

|

|

|

Function |

Pin |

Symbol |

Type |

Description |

|

|

|

|

|

|

|

|

|

External |

8 |

P2.0 |

I |

P2.0 to P2.3 secondary functions : |

|

|

Interrupts |

|

|

|

These are level-triggered external interrupt input pins. |

|

|

7 |

P2.1 |

|

|||

|

|

|

Select interrupt enable/disable for each bit with the P2 interrupt |

|||

|

|

6 |

P2.2 |

|

||

|

|

|

enable register (P2IE). |

|||

|

|

|

|

|

||

|

|

5 |

P2.3 |

|

||

|

|

|

If P2.0 to P2.3 pins are set to "H" level for a minimum of 2 seconds, |

|||

|

|

|

|

|

the device enters system reset mode. |

|

|

|

|

|

|

P2.0, P2.1 secondary functions : |

|

|

|

|

|

|

trigger input pins for capture circuit. |

|

|

|

|

|

|

|

|

|

|

10 |

P3.0 |

I |

P3.0 secondary function : |

|

|

|

|

|

|

This is an input pin for external interrupt. This pin can receive an |

|

|

|

|

|

|

interrupt at a rising edge, a falling edge, or at both rising and falling |

|

|

|

|

|

|

edges. |

|

|

|

|

|

|

|

|

|

|

18 |

P6.0 |

I |

P6.0 to P6.3 secondary functions : |

|

|

|

|

|

|

These are level-triggered external interrupt input pins. |

|

|

|

17 |

P6.1 |

|

||

|

|

|

|

|

||

|

|

16 |

P6.2 |

|

|

|

|

|

|

|

|

|

|

|

|

15 |

P6.3 |

|

|

|

|

|

|

|

|

|

|

|

|

22 |

P7.0 |

I |

P7.0 to P7.3 secondary functions : |

|

|

|

|

|

|

These are level-triggered external interrupt input pins. |

|

|

|

21 |

P7.1 |

|

||

|

|

|

|

|

||

|

|

20 |

P7.2 |

|

|

|

|

|

|

|

|

|

|

|

|

19 |

P7.3 |

|

|

|

|

|

|

|

|

|

|

|

Event |

9 |

P3.1 |

I |

P3.1 secondary function : |

|

|

Counter |

|

|

|

Input port for event counter |

|

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

9/29

Loading...

Loading...