OKI MSM518221-30GS-K, MSM518221-25JS, MSM518221-40ZS, MSM518221-30ZS, MSM518221-40GS-K Datasheet

...

E2L0032-17-Y1

This version: Jan. 1998

¡SemiconductorSemiconductor MSM518221

Previous version: Dec. 1996

MSM518221

262,214-Word ¥ 8-Bit Field Memory

DESCRIPTION

The OKI MSM518221 is a high performance 2-Mbit, 256K ¥ 8-bit, Field Memory. It is designed for high-speedserialaccessapplicationssuchasHDTVs,conventionalNTSCTVs,VTRs,digitalmovies and Multi-media systems. The 2-Mbit capacity fits one field of a conventional NTSC TV screen.

Each of the 8-bit planes has separate serial write and read ports. These employ independent control clocks to support asynchronous read and write operations. Different clock rates are also supported, which allow alternate data rates between write and read data streams.

TheMSM518221provideshighspeedFIFO,First-InFirst-Out,operationwithoutexternalrefreshing: it refreshes its DRAM storage cells automatically, so that it appears fully static to the users. Moreover, fully static type memory cells and decoders for serial access enable the refresh free serial access operation, so that serial read and/or write control clock can be halted high or low for any duration as long as the power is on. Internal conflicts of memory access and refreshing operations are prevented by special arbitration logic.

The MSM518221's function is simple, and similar to a digital delay device whose delay-bit-length is easily set by reset timing. The delay length, and the number of read delay clocks between write and read, is determined by externally controlled write and read reset timings.

Additional SRAM serial registers, or line buffers for the initial access of 256 ¥8-bit enable high speed first-bit-access with no clock delay just after the write or read reset timings.

TheMSM518221issimilarinoperationandfunctionalitytoOKI1-MbitFieldMemoryMSM514221B. It has a write mask function or input enable function (IE), and read-data skipping function or output enablefunction(OE). Thedifferencesbetweenwriteenable(WE)andinputenable(IE),andbetween read enable (RE) and output enable (OE) are that WE and RE can stop serial write/read address increments, but IE and OE cannot stop the increment, when write/read clocking is continuously appliedtoMSM518221.Theinputenable(IE)functionallowstheusertowriteintoselectedlocations of the memory only, leaving the rest of the memory contents unchanged. This facilitates data processing to display a "picture in picture" on a TV screen.

1/16

¡ Semiconductor |

MSM518221 |

FEATURES

•Single power supply : 5 V ±10%

•512 Rows ¥ 512 Columns ¥ 8 bits

•Fast FIFO (First-In First-Out) operation

•High speed asynchronous serial access

Read/write cycle time |

25 ns/30 ns/40 ns |

Access time |

25 ns/25 ns/30 ns |

•Functional compatibility with OKI MSM514221B

•Write mask function (Input enable control)

•Data skipping function (Output enable control)

•Self refresh (No refresh control is required)

•Package options :

28-pin 400 mil plastic ZIP |

(ZIP28-P-400-1.27) |

(Product : MSM518221-xxZS) |

28-pin 400 mil plastic SOJ |

(SOJ28-P-400-1.27) |

(Product : MSM518221-xxJS) |

28-pin 430 mil plastic SOP |

(SOP28-P-430-1.27-K) |

(Product : MSM518221-xxGS-K) |

|

|

xx indicates speed rank. |

PRODUCT FAMILY

Family |

Access Time (Max.) |

Cycle Time (Min.) |

Package |

|

|

|

|

|

|

MSM518221-25ZS |

25 ns |

25 ns |

|

|

|

|

|

|

|

MSM518221-30ZS |

25 ns |

30 ns |

400 mil 28-pin ZIP |

|

|

|

|

|

|

MSM518221-40ZS |

30 ns |

40 ns |

|

|

MSM518221-25JS |

25 ns |

25 ns |

|

|

MSM518221-30JS |

25 ns |

30 ns |

400 mil 28-pin SOJ |

|

MSM518221-40JS |

30 ns |

40 ns |

|

|

MSM518221-30GS-K |

25 ns |

30 ns |

430 mil 28-pin SOP |

|

MSM518221-40GS-K |

30 ns |

40 ns |

||

|

2/16

¡ Semiconductor |

MSM518221 |

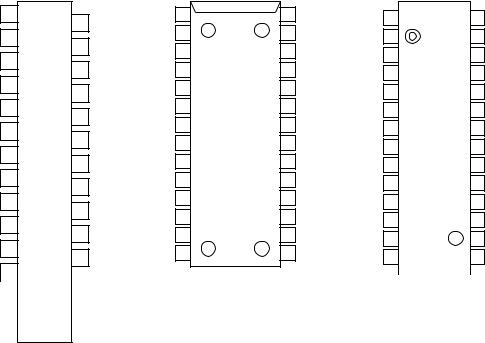

PIN CONFIGURATION (TOP VIEW)

WE |

1 |

IE |

DIN4 |

1 |

28 |

VCC |

DIN4 |

1 |

28 |

VCC |

|

|

2 |

DIN5 |

2 |

27 |

DIN3 |

|

|

|

|

||

DIN0 |

3 |

DIN1 |

DIN5 |

2 |

27 |

DIN3 |

|||||

DIN2 |

4 |

DIN6 |

3 |

26 |

DIN2 |

DIN6 |

3 |

26 |

DIN2 |

||

5 |

DIN3 |

||||||||||

|

|

|

|

|

|

|

|

||||

VCC |

6 |

DIN7 |

4 |

25 |

DIN1 |

DIN7 |

4 |

25 |

DIN1 |

||

7 |

DIN4 |

RSTW |

5 |

24 |

DIN0 |

RSTW |

5 |

24 |

DIN0 |

||

|

8 |

||||||||||

DIN5 |

9 |

DIN6 |

SWCK |

6 |

23 |

IE |

SWCK |

6 |

23 |

IE |

|

|

10 |

NC |

7 |

22 |

WE |

NC |

7 |

22 |

WE |

||

DIN7 |

11 |

|

|||||||||

RSTW |

RE |

8 |

21 |

NC |

|||||||

SWCK |

12 |

RE |

8 |

21 |

NC |

||||||

13 |

|

|

|

|

|

||||||

NC |

OE |

9 |

20 |

SRCK |

OE |

9 |

20 |

SRCK |

|||

NC |

14 |

||||||||||

15 |

RE |

DOUT7 10 |

19 |

RSTR |

DOUT7 10 |

19 |

RSTR |

||||

|

16 |

||||||||||

OE |

17 |

DOUT7 |

DOUT6 11 |

18 |

DOUT0 |

DOUT6 11 |

18 |

DOUT0 |

|||

DOUT6 |

18 |

DOUT5 12 |

17 |

DOUT1 |

DOUT5 12 |

17 |

DOUT1 |

||||

19 |

DOUT5 |

||||||||||

DOUT4 |

20 |

DOUT4 13 |

16 |

DOUT2 |

DOUT4 13 |

16 |

DOUT2 |

||||

21 |

VSS |

VSS 14 |

15 |

DOUT3 |

VSS 14 |

15 |

DOUT3 |

||||

|

22 |

||||||||||

DOUT3 |

23 |

|

|

DOUT2 |

|

|

|

24 |

|

|

|

||||

DOUT1 |

|

|

|

|

|||

25 |

|

|

28-Pin Plastic SOJ |

28-Pin Plastic SOP |

|||

RSTR |

|

26 |

DOUT0 |

|

|

|

|

|

|

|

|

||||

27 |

|

|

SRCK |

|

|

|

|

28 |

|

|

|

||||

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

28-Pin Plastic ZIP

Pin Name |

Function |

SWCK |

Serial Write Clock |

|

|

SRCK |

Serial Read Clock |

|

|

WE |

Write Enable |

RE |

Read Enable |

|

|

IE |

Input Enable |

|

|

OE |

Output Enable |

RSTW |

Write Reset Clock |

|

|

RSTR |

Read Reset Clock |

|

|

DIN0 - 7 |

Data Input |

DOUT0 - 7 |

Data Output |

VCC |

Power Supply (5 V) |

VSS |

Ground (0 V) |

NC |

No Connection |

|

|

3/16

4/16

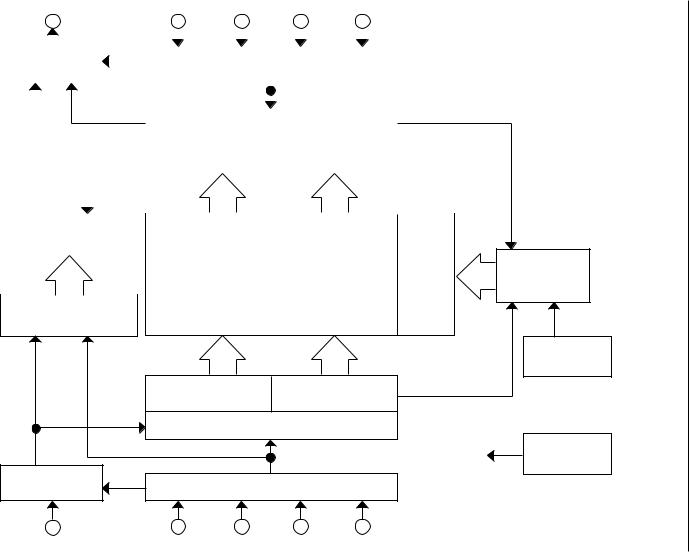

DOUT (¥ 8) |

OE |

RE |

|

RSTR |

SRCK |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data-out |

|

|

Serial |

Read |

|

|

|

Controller |

|

|||||||

|

|

|

|

|

|

|||||||||||

Buffer (¥ 8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

512 Word Serial Read Register (¥ 8) |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Read Line Buffer |

|

|

Read Line Buffer |

|

||||||

|

|

|

|

|

|

Low-Half (¥ 8) |

|

|

High-Half (¥ 8) |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

256 (¥ 8) |

|

|

256 (¥ 8) |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

71 Word |

|

|

|

|

|

|

|

|

|

|

|

|

|||

Sub-Register (¥ 8) |

|

|

|

|

|

|

|

|

|

|

|

X |

||||

|

|

|

|

|

|

|

|

|

256K (¥ 8) |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

Memory |

|

|

|

|

Decoder |

||

|

|

|

|

|

|

|

|

|

|

Array |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

71 Word |

|

|

|

|

Sub-Register (¥ 8) |

|

|

|

|

|

|

256 (¥ 8) |

256 (¥ 8) |

|

|

Write Line Buffer |

Write Line Buffer |

||

|

Low-Half (¥ 8) |

High-Half (¥ 8) |

||

|

512 Word Serial Write Register (¥ 8) |

|||

Data-in |

|

|

|

|

Buffer (¥ 8) |

Serial |

Write |

Controller |

|

DIN (¥ 8) |

IE |

WE |

RSTW |

SWCK |

DIAGRAM BLOCK |

Semiconductor ¡ |

Read/Write

and Refresh

Controller

Clock

Oscillator

VBB

Generator

MSM518221

¡ Semiconductor |

MSM518221 |

OPERATION

Write Operation

The write operation is controlled by three clocks, SWCK, RSTW, and WE. Write operation is accomplished by cycling SWCK, and holding WE high after the write address pointer reset operation or RSTW.

Each write operation, which begins after RSTW, must contain at least 80 active write cycles, i.e. SWCK cycles while WE is high. To transfer the last data to the DRAM array, which at that time is stored in the serial data registers attached to the DRAM array, an RSTW operation is required after the last SWCK cycle.

Write Reset : RSTW

The first positive transition of SWCK after RSTW becomes high resets the write address counters to zero. RSTW setup and hold times are referenced to the rising edge of SWCK. Because the write reset function is solely controlled by the SWCK rising edge after the high level of RSTW, the states of WE and IE are ignored in the write reset cycle.

Before RSTW may be brought high again for a further reset operation, it must be low for at least two SWCK cycles.

Data Inputs : DIN0 - 7

Write Clock : SWCK

The SWCK latches the input data on chip when WE is high, and also increments the internal write addresspointer. Data-insetuptimetDS,andholdtimetDH arereferencedtotherisingedgeofSWCK.

Write Enable : WE

WE isused fordatawriteenable/disable control. WEhighlevelenables theinput, andWE lowlevel disablestheinputandholdstheinternalwriteaddresspointer. TherearenoWEdisabletime(low) and WE enable time (high) restrictions, because the MSM518221 is in fully static operation as long as the power is on. Note that WE setup and hold times are referenced to the rising edge of SWCK.

Input Enable : IE

IE is used to enable/disable writing into memory. IE high level enables writing. The internal write addresspointerisalwaysincrementedbycyclingSWCKregardlessoftheIElevel. NotethatIEsetup and hold times are referenced to the rising edge of SWCK.

5/16

Loading...

Loading...