Motorola MC33349N-4, MC33349N-3, MC33349N-1, MC33349N-10, MC33349N-2 Datasheet

...

Order this document by MC33349PP/D

Product Preview

Lithium Battery Protection Circuit for One Cell Battery Packs

The MC33349 is a monolithic lithium battery protection circuit that is designed to enhance the useful operating life of a one cell rechargeable battery pack. Cell protection features consist of internally trimmed charge and discharge voltage limits, charge and discharge current limit detection, and a virtually zero current sleepmode state when the cell is discharged. This protection circuit requires a minimum number of external components and is targeted for inclusion within the battery pack. This MC33349 is available in the SOT±23 6 lead surface mount package.

•Internally Trimmed Charge and Discharge Voltage Limits

•Charge and Discharge Current Limit Detection

•Virtually Zero Current Sleepmode State when Cells are Discharged

•Dedicated for One Cell Applications

•Minimum Components for Inclusion within the Battery Pack

•Available in a Low Profile Surface Mount Package

Ordering Information shown on following page.

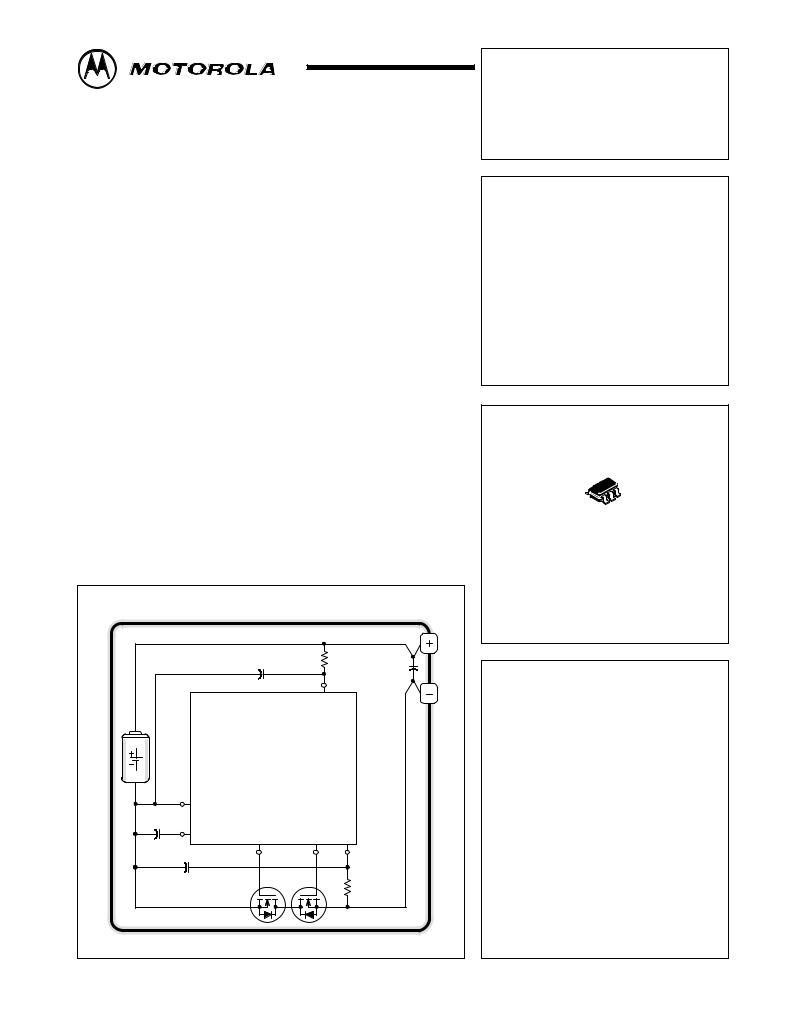

Typical One Cell Smart Battery Pack

|

0.1 μF |

|

100 Ω |

|

|

|

|

|

|

5 |

|

|

MC33349 |

|

|

|

6 |

|

|

0.01 μF |

4 |

3 |

2 |

|

1 |

||

|

0.1 μF |

|

1.0 kΩ |

|

|

|

This device contains 264 active transistors.

MC33349

LITHIUM BATTERY

PROTECTION CIRCUIT

FOR

ONE CELL

SMART BATTERY PACKS

SEMICONDUCTOR

TECHNICAL DATA

6

1

N SUFFIX

PLASTIC PACKAGE

CASE 1262 (SOT±23)

PIN CONNECTIONS

|

|

|

|

|

|

|

DO |

1 |

|

|

|

6 |

Gnd |

|

|

|

|

|

|

|

P± |

2 |

|

|

|

5 |

Vcell |

CO |

|

|

|

|

|

Ct |

3 |

|

|

|

4 |

||

|

|

|

|

|

|

|

|

|

(Top View) |

|

|||

This document contains information on a product under development. Motorola reserves the |

Motorola, Inc. 1998 |

Rev 0 |

right to change or discontinue this product without notice. |

|

|

MC33349

ORDERING INFORMATION

|

Charge |

Charge |

Discharge |

|

|

|

|

|

Overvoltage |

Overvoltage |

Undervoltage |

Current Limit |

Operating |

|

|

Device |

Threshold (V) |

Hysteresis (mV) |

Threshold (V) |

Threshold (mV) |

Temperature Range |

Package |

|

|

|

|

|

|

|

|

|

MC33349N±1 |

4.2 |

|

|

150 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±2 |

4.2 |

|

|

75 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±3 |

4.25 |

|

|

150 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±4 |

4.25 |

|

|

75 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±5 |

4.3 |

200 |

2.3 |

150 |

TA = ±40 to 85°C |

SOT±23 |

|

|

|

|

|||||

MC33349N±6 |

4.3 |

75 |

|||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

MC33349N±7 |

4.35 |

|

|

150 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±8 |

4.35 |

|

|

75 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±9 |

4.65 |

|

|

150 |

|

|

|

|

|

|

|

|

|

|

|

MC33349N±10 |

4.65 |

|

|

75 |

|

|

|

|

|

|

|

|

|

|

MAXIMUM RATINGS

Ratings |

Symbol |

Value |

Unit |

|

|

|

|

Input Voltage |

VIR |

|

V |

Discharge Gate Drive Output (Pin 1) to Gnd (Pin 6) |

|

5.0 to ±1.0 |

|

Charge Gate Drive Common/Current Limit (Pin 2) to Vcell |

|

1.0 to ±18 |

|

(Pin 5) |

|

|

|

Charge Gate Drive Output (Pin 3) to Vcell (Pin 5) |

|

1.0 to ±18 |

|

Overvoltage Delay Capacitor (Pin 4) to Gnd (Pin 6) |

|

5.0 to ±1.0 |

|

Cell Voltage (Pin 5) to Gnd (Pin 6) |

|

5.0 to ±1.0 |

|

|

|

|

|

Thermal Resistance, Junction±to±Air |

RθJA |

|

°C/W |

N Suffix, SOT±23 Plastic Package, Case 1262 |

|

TBD |

|

|

|

|

|

Operating Junction Temperature (Note 1) |

TJ |

±40 to 85 |

°C |

Storage Temperature |

Tstg |

±55 to 125 |

°C |

2 |

MOTOROLA ANALOG IC DEVICE DATA |

MC33349

ELECTRICAL CHARACTERISTICS (Ct = 0.01 μF, TA = 25°C, for min/max values TA is the operating junction temperature range that applies, unless otherwise noted.)

Characteristic |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

VOLTAGE SENSING |

|

|

|

|

|

|

|

|

|

|

|

|

|

Cell Charging Cutoff (Pin 5 to Pin 6) |

|

|

|

|

|

|

Overvoltage Threshold, VCell Increasing |

|

|

|

|

|

|

Vth(OV) |

|

|

|

V |

||

±1, ±3 Suffix |

|

± |

4.35 |

± |

|

|

±2, ±4 Suffix |

|

± |

4.25 |

± |

|

|

Overvoltage Hysteresis VCell Decreasing |

VH |

± |

200 |

± |

mV |

|

Cell Discharging Cutoff (Pin 5 to Pin 6) |

|

|

|

|

|

|

|

|

|

|

|

|

|

Undervoltage Threshold, VCell Decreasing |

Vth(UV) |

|

|

|

V |

|

±1, ±3 Suffix |

|

± |

2.30 |

± |

|

|

±2, ±4 Suffix |

|

± |

2.28 |

± |

|

|

|

|

|

|

|

|

|

Input Bias Current During Cell Voltage Sample (Pin 5) |

IIIB |

± |

20 |

± |

μA |

|

Overvoltage Delay Time (Vcell = 4.5 V) |

t(ovd) |

± |

75 |

± |

ms |

|

Unervoltage Delay Time (Vcell = 2.1 V) |

t(uvd) |

± |

13 |

± |

ms |

|

Cell Voltage Sampling Period |

t(smpl) |

± |

2.0 |

± |

ms |

|

Cell Voltage Sampling Repitition Period |

t(rep) |

± |

26 |

± |

ms |

|

CURRENT SENSING |

|

|

|

|

|

|

|

|

|

|

|

|

|

Discharge/Charge Current Limit (Pin 2 to Pin 6) |

|

|

|

|

|

|

Discharge Threshold Voltage |

|

|

|

|

|

|

Vth(dschg) |

|

|

|

mV |

||

±1, ±2 Suffix |

|

± |

150 |

± |

|

|

±3, ±4 Suffix |

|

± |

75 |

± |

|

|

Discharge Current Hysteresis |

DCH |

± |

50 |

± |

% |

|

Charge Threshold Voltage |

Vth(chg) |

|

|

|

mV |

|

±1. ±2 Suffix |

|

± |

±150 |

± |

|

|

±3, ±4 Suffix |

|

± |

±75 |

± |

|

|

Charge Current Hysteresis |

CCH |

± |

25 |

± |

% |

|

|

|

|

|

|

|

|

Current Limit Delay Time (1.0 nF load @ CO & DO; to VDD/2) |

|

|

|

|

μs |

|

Charge Gate Drive Output (Pin 3) |

t(ccld) |

± |

10 |

± |

||

Discharge Gate Drive Output (Pin 1) |

t(dcld) |

± |

2.0 |

± |

μs |

|

OUTPUTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

Charge Gate Drive Output Low (Pin 3 to Pin 2 @ IO = 50 μA) |

Volc |

± |

0.2 |

± |

V |

|

Charge Gate Drive Output High (Pin 5 to Pin 3 @ IO = ±50 μA) |

Vohc |

± |

0.1 |

± |

V |

|

Discharge Gate Drive Output Low (Pin 1 to Pin 6 @ IO = 50 μA) |

Vold |

± |

0.2 |

± |

V |

|

Discharge Gate Drive Output High (Pin 5 to Pin 1 @ IO = ±50 μA) |

Vohd |

± |

0.2 |

± |

V |

|

TOTAL DEVICE |

|

|

|

|

|

|

|

|

|

|

|

|

|

Average Cell Current |

Icell |

|

|

|

|

|

Operating (Vcell = 3.9 V) |

|

± |

8.5 |

± |

μA |

|

Sleepmode (Vcell = 2.0 V) |

|

± |

4.0 |

± |

nA |

|

Minimum Operating Cell Voltage |

Vcell |

± |

1.5 |

± |

V |

|

MOTOROLA ANALOG IC DEVICE DATA |

3 |

|

Loading...

Loading...