Motorola MC1741CDR2, MC1741CP1, MC1741CD Datasheet

Order this document by MC1741C/D

Internally Compensated,

High Performance

Operational Amplifier

The MC1741C was designed for use as a summing amplifier, integrator, or amplifier with operating characteristics as a function of the external feedback components.

•No Frequency Compensation Required

•Short Circuit Protection

•Offset Voltage Null Capability

•Wide Common Mode and Differential Voltage Ranges

•Low Power Consumption

•No Latch Up

MAXIMUM RATINGS

Rating |

Symbol |

Value |

Unit |

|

|

|

|

Power Supply Voltage |

VCC, VEE |

±18 |

Vdc |

Input Differential Voltage |

VID |

±30 |

V |

Input Common Mode Voltage (Note 1) |

VICM |

±15 |

V |

Output Short Circuit Duration (Note 2) |

tSC |

Continuous |

|

Operating Ambient Temperature Range |

TA |

0 to +70 |

°C |

Storage Temperature Range |

Tstg |

±55 to +125 |

°C |

NOTES: 1. For supply voltages less than +15 V, the absolute maximum input voltage is equal to the supply voltage.

2. Supply voltage equal to or less than 15 V.

Equivalent Circuit Schematic

(1/4 of Circuit Shown)

|

|

|

|

VCC |

Noninverting |

|

|

|

G |

|

|

|

|

|

Input |

|

|

4.5 k |

|

|

|

|

|

|

Inverting |

|

|

39 k |

25 |

|

|

|

||

Input |

|

|

30 pF 7.5 k |

Output |

|

|

|

|

|

|

|

|

|

50 |

Offset |

|

|

|

|

Null |

|

|

50 k |

50 |

1.0 k |

50 k |

1.0 k |

5.0 k |

|

VEE

VEE

MC1741C

OPERATIONAL

AMPLIFIER

SEMICONDUCTOR

TECHNICAL DATA

8

1

P1 SUFFIX

PLASTIC PACKAGE

CASE 626

8

1

D SUFFIX

PLASTIC PACKAGE

CASE 751 (SO±8)

PIN CONNECTIONS |

||||

Offset Null |

1 |

|

8 |

N.C. |

Inv. Input |

2 |

|

7 |

VCC |

Noninv. Input |

3 |

+ |

6 |

Output |

|

||||

VEE |

4 |

|

5 |

Offset Null |

|

|

(Top View) |

|

|

ORDERING INFORMATION

|

|

Operating |

|

Device |

Alternate |

Temperature Range |

Package |

|

|

|

|

MC1741CD |

± |

|

SO±8 |

|

|

TA = 0° to +70°C |

|

MC1741CP1 |

LM741CN |

Plastic DIP |

|

|

μA741TC |

|

|

|

|

|

|

Motorola, Inc. 1996 |

Rev 5 |

MC1741C

ELECTRICAL CHARACTERISTICS (VCC = +15 V, VEE = ±15 V, TA = 25°C, unless otherwise noted.)

|

Characteristic |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

Input Offset Voltage (RS ≤ 10 k) |

VIO |

± |

2.0 |

6.0 |

mV |

|

Input Offset Current |

IIO |

± |

20 |

200 |

nA |

|

Input Bias Current |

IIB |

± |

80 |

500 |

nA |

|

Input Resistance |

ri |

0.3 |

2.0 |

± |

MΩ |

|

Input Capacitance |

Ci |

± |

1.4 |

± |

pF |

|

Offset Voltage Adjustment Range |

VIOR |

± |

±15 |

± |

mV |

|

Common Mode Input Voltage Range |

VICR |

±12 |

±13 |

± |

V |

|

Large Signal Voltage Gain (VO = ±10 V, RL ≥ 2.0 k) |

AVOL |

20 |

200 |

± |

V/mV |

|

Output Resistance |

ro |

± |

75 |

± |

Ω |

|

Common Mode Rejection (RS ≤ 10 k) |

CMR |

70 |

90 |

± |

dB |

|

Supply Voltage Rejection (RS ≤ 10 k) |

PSR |

75 |

± |

± |

dB |

|

Output Voltage Swing |

VO |

|

|

|

V |

|

(RL ≥ |

10 k) |

|

±12 |

±14 |

± |

|

(RL ≥ |

2.0 k) |

|

±10 |

±13 |

± |

|

Output Short Circuit Current |

ISC |

± |

20 |

± |

mA |

|

Supply Current |

ID |

± |

1.7 |

2.8 |

mA |

|

Power Consumption |

PC |

± |

50 |

85 |

mW |

|

Transient Response (Unity Gain, Noninverting) |

|

|

|

|

|

|

(VI = 20 mV, RL ≥ 2.0 k, CL ≤ 100 pF) Rise Time |

tTLH |

± |

0.3 |

± |

μs |

|

(VI = 20 mV, RL ≥ 2.0 k, CL ≤ 100 pF) Overshoot |

os |

± |

15 |

± |

% |

|

(VI = 10 V, RL ≥ 2.0 k, CL ≤ 100 pF) Slew Rate |

SR |

± |

0.5 |

± |

V/μs |

|

ELECTRICAL CHARACTERISTICS (VCC = +15 V, VEE = ±15 V, TA = Tlow to Thigh, unless otherwise noted.)* |

|

|

||||

|

Characteristic |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

Input Offset Voltage (RS ≤ 10 kΩ) |

VIO |

± |

± |

7.5 |

mV |

|

Input Offset Current (TA = 0° to +70°C ) |

IIO |

± |

± |

300 |

nA |

|

Input Bias Current (TA = 0° to +70°C ) |

IIB |

± |

± |

800 |

nA |

|

Supply Voltage Rejection (RS ≤ 10 k) |

PSR |

75 |

± |

± |

dB |

|

Output Voltage Swing (RL ≥ 2.0 k) |

VO |

±10 |

±13 |

± |

V |

|

Large Signal Voltage Gain (RL ≥ 2.0 k, VO = ±10 V) |

AVOL |

15 |

± |

± |

V/mV |

|

* Tlow = 0°C Thigh = 70°C

2 |

MOTOROLA ANALOG IC DEVICE DATA |

MC1741C

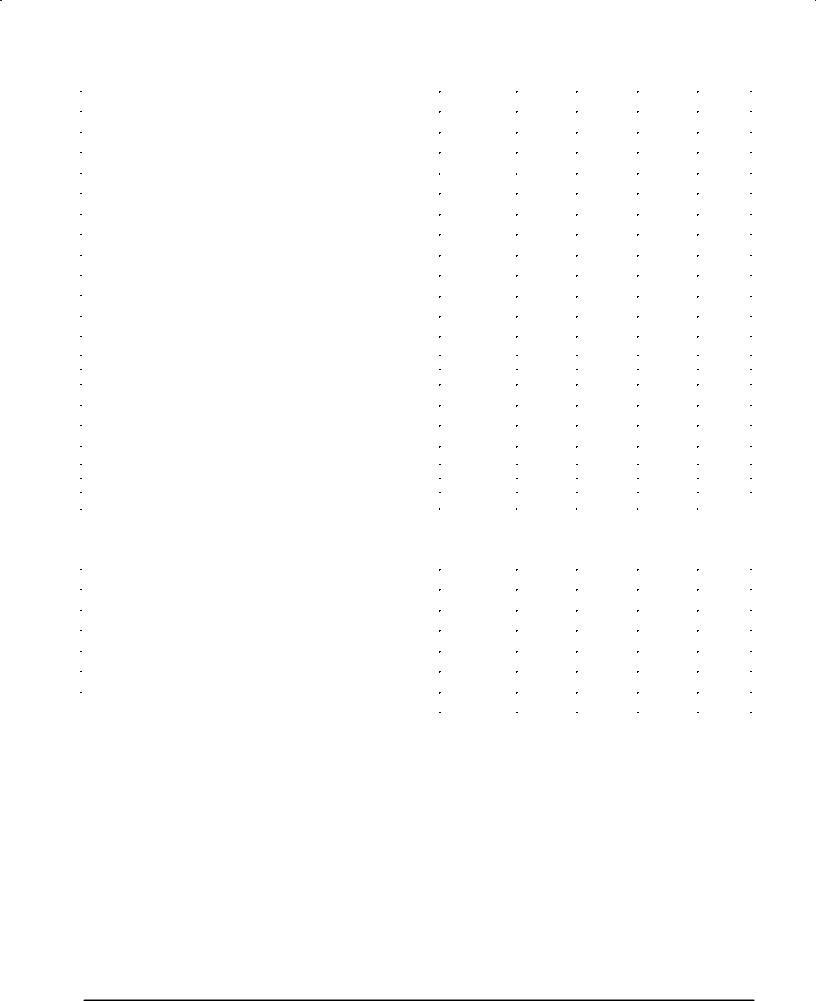

Figure 1. Burst Noise versus Source Resistance

1000

(μVpk) |

100 |

|

|

|

BW = 1.0 Hz to 1.0 kHz |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

,INPUT NOISE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

e |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

100 |

1.0 k |

10 k |

100 k |

1.0 M |

||

|

|

|

|

RS, SOURCE RESISTANCE (Ω) |

|

|

|

|

en, INPUT NOISE (μVpk)

Figure 2. RMS Noise versus Source Resistance

100

BW = 1.0 Hz to 1.0 kHz

10

1.0

0.1

10 |

100 |

1.0 |

10 k |

100 k |

1.0 M |

|

|

RS, SOURCE RESISTANCE (Ω) |

|

|

|

Figure 3. Output Noise versus Source Resistance |

Figure 4. Spectral Noise Density |

(mVrms) |

10 |

|

|

|

|

)Hz |

14.0 |

|

|

|

|

|

|

|

|

|

12.0 |

|

AV = 10, RS = 100 k Ω |

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

AV = 1000 |

|

|

|

10.0 |

|

|

||

NOISEOUTPUT |

1.0 |

|

|

|

|

(NOISEnV/√ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

8.0 |

|

|

|

|

|

|

|

10 |

|

|

INPUT |

6.0 |

|

|

|

|

e |

0.1 |

|

|

|

|

4.0 |

|

|

|

|

|

n |

|

|

|

|

|

|

|

|

|

|

|

, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.0 |

|

|

, |

|

|

|

|

|

|

|

|

|

|

n |

2.0 |

|

|

|

|

|

|

|

|

|

|

|

e |

|

|

|

|

|

|

0.01 |

100 |

1.0 k |

10 k |

100 k |

1.0 M |

0 |

100 |

1.0 k |

10 k |

100 k |

|

10 |

10 |

|||||||||

|

|

|

RS, SOURCE RESISTANCE (Ω) |

|

|

|

|

f, FREQUENCY (Hz) |

|

||

|

|

|

|

|

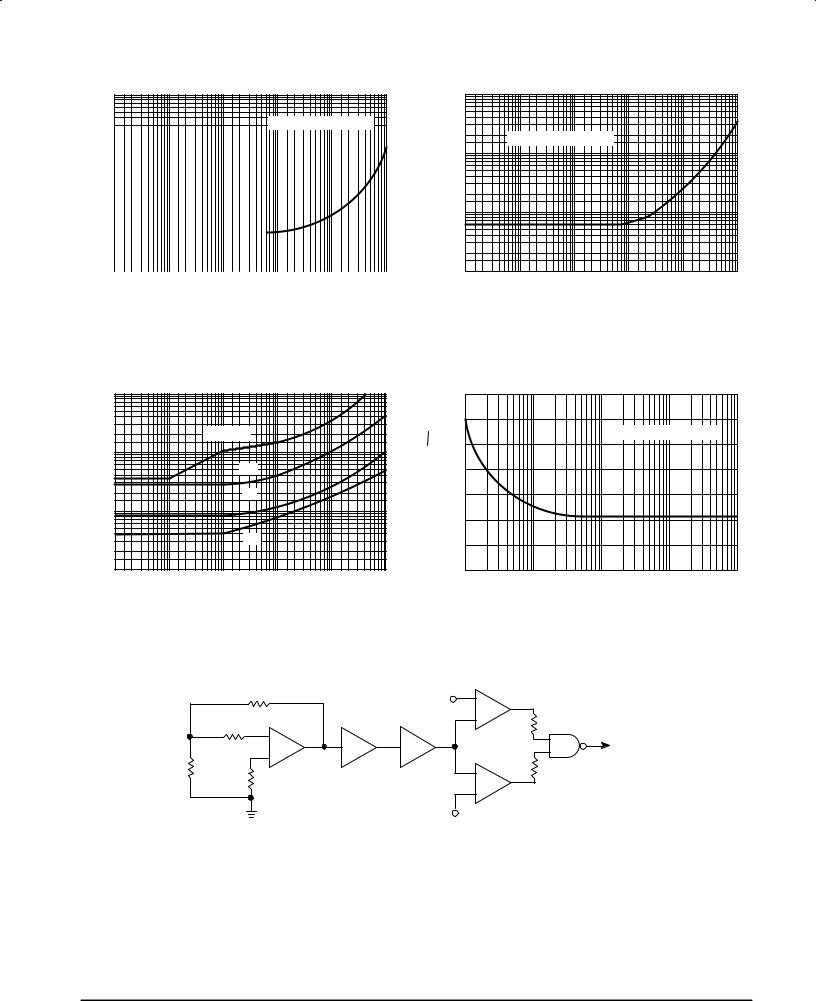

Figure 5. Burst Noise Test Circuit |

|

|

|

|

||

|

|

|

100 k |

|

Positive |

+ |

|

|

|

|

|

|

|

|

|

Threshold |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Voltage |

± |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 k |

± |

x500 |

x2 |

|

|

To |

Pass / Fail |

|

|

|

|

+ |

|

|

|

Indicator |

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

1.0 k |

|

|

+ |

100 k |

|

Low Pass |

|

Operational Amplifier |

|

||

|

Filter |

± |

|

|

Under Test |

||

|

1.0 Hz to 1.0 kHz |

|

|

|

|

|

Negative

Threshold

Voltage

Unlike conventional peak reading or RMS meters, this system was especially designed to provide the quick response time essential to burst (popcorn) noise testing.

The test time employed is 10 sec and the 20 mV peak limit refers to the operational amplifier input thus eliminating errors in the closed loop gain factor of the operational amplifier.

MOTOROLA ANALOG IC DEVICE DATA |

3 |

|

Loading...

Loading...