Fairchild Semiconductor DM74ALS5245WMX, DM74ALS5245WM, DM74ALS5245SJX, DM74ALS5245N Datasheet

October 1986

Revised February 2000

DM74ALS5245

Octal 3-STATE Transceiver

General Description

This octal bus transceiver is designed for asynchronous two-way communication between data buses. The inputs include hysteresis which provides improved noise rejection. Data is transmitted either from the A bus to the B bus or from the B bus to the A bus depending on the logic level of the direction control (DIR) input. The device can be disabled via the enable input (G) which causes the outputs to enter the high impedance mode so the buses are effectively isolated.

Features

■Input Hysteresis

■Low output noise generation

■High input noise immunity

■Advanced oxide-isolated, ion implanted Schottky TTL process

■Switching specification guaranteed over the full temperature and VCC range

■PNP inputs to reduce input loading

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74ALS5245WM |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

DM74ALS5245SJ |

M20D |

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

DM74ALS5245N |

N20A |

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

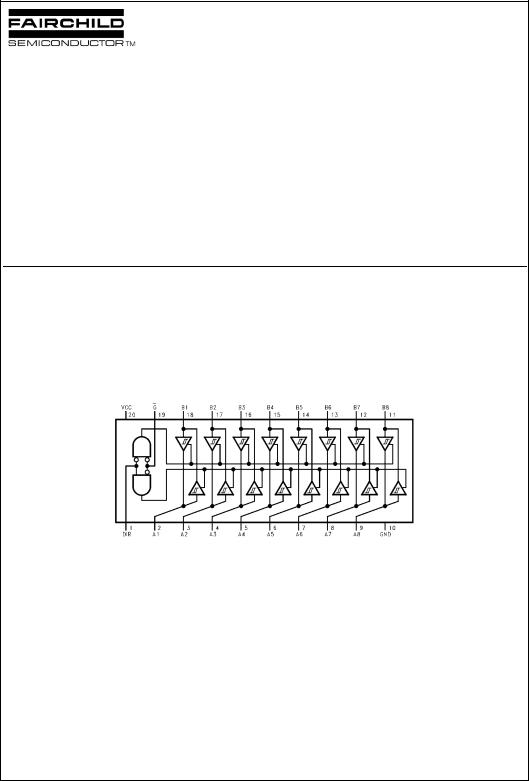

Connection Diagram

Function Table

|

|

Control Inputs |

Operation |

|

||

|

|

|

|

|

|

|

|

|

G |

|

DIR |

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

B Data to A Bus |

|

|

|

|

|

|

|

|

|

|

L |

|

H |

A Data to B Bus |

|

|

|

|

|

|

|

|

|

|

H |

|

X |

High Impedance |

|

|

|

|

|

|

|

|

L = LOW Logic Level |

H = HIGH Logic Level |

X = Don't Care (Either LOW or HIGH Logic Level) |

||||

Transceiver STATE-3 Octal DM74ALS5245

© 2000 Fairchild Semiconductor Corporation |

DS009175 |

www.fairchildsemi.com |

DM74ALS5245

Absolute Maximum Ratings(Note 1)

Supply Voltage |

7V |

Input Voltage |

|

Control Inputs |

7V |

I/O Ports |

5.5V |

Operating Free-Air Temperature Range |

0°C to +70°C |

Storage Temperature Range |

−65°C to +150°C |

Typical θJA |

|

N Package |

56.0°C/W |

M Package |

74.0°C/W |

Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristic tables are not guaranteed at the absolute maximum ratings. The “Recommended Operating Conditions” table will define the conditions for actual device operation.

Recommended Operating Conditions

Symbol |

Parameter |

Min |

Max |

Units |

|

|

|

|

|

VCC |

Supply Voltage |

4.5 |

5.5 |

V |

VIH |

HIGH Level Input Voltage |

2 |

|

V |

VIL |

LOW Level Input Voltage |

|

0.8 |

V |

IOH |

HIGH Level Output Current |

|

−15 |

mA |

IOL |

LOW Level Output Current |

|

24 |

mA |

TA |

Free Air Operating Temperature Range |

0 |

70 |

°C |

Electrical Characteristics

over recommended free air temperature range. All typical values are measured at VCC = 5V, TA = 25°C.

Symbol |

Parameter |

Test Conditions |

Min |

Typ |

Max |

Units |

|||

|

|

|

|

|

|

|

|

|

|

VIK |

Input Clamp Voltage |

VCC = Min, II = −18 mA |

|

|

|

−1.5 |

V |

||

HYS |

Hysteresis (VT+ − VT−) |

VCC = Min |

|

0.2 |

0.32 |

|

V |

||

VOH |

HIGH Level |

|

VCC = 4.5V to 5.5V |

IOH = −0.4 mA |

VCC − 2 |

|

|

|

|

|

Output Voltage |

VCC = Min |

IOH = −3 mA |

2.4 |

3.2 |

|

V |

||

|

|

|

|

|

IOH = Max |

2 |

|

|

|

VOL |

LOW Level |

VCC = Min |

IOL = 12 mA |

|

0.25 |

0.4 |

V |

||

|

Output Voltage |

|

|

IOL = 24 mA |

|

0.35 |

0.5 |

||

|

|

|

|

|

|||||

II |

Input Current at |

VCC = Max |

I/O Ports, VI = 5.5V |

|

|

100 |

μA |

||

|

Maximum Input Voltage |

|

|

Control Inputs, VI = 7V |

|

|

100 |

||

|

|

|

|

|

|

||||

IIH |

HIGH Level Input Current |

VCC = Max, VI = 2.7V |

|

|

|

20 |

μA |

||

IIL |

LOW Level Input Current |

VCC = Max, VI = 0.4V |

|

|

|

−100 |

μA |

||

IO |

Output Drive Current |

VCC = Max, VO = 2.25V |

|

−30 |

|

−112 |

mA |

||

ICC |

Supply Current |

VCC = Max |

Outputs HIGH |

|

30 |

45 |

|

||

|

|

|

|

|

Outputs LOW |

|

36 |

55 |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Outputs Disabled |

|

38 |

58 |

|

|

|

|

|

|

|

|

|

|

|

VOLP |

Quiet Output Maximum |

VCC = 5.0V, TA = 25°C |

|

|

0.5 |

|

V |

||

|

Dynamic VOL |

(Figures 1, 2; (Note 2)(Note 3)) |

|

|

|||||

|

|

|

|

|

|||||

VOLV |

Quiet Output Minimum |

VCC = 5.0V, TA = 25°C |

|

|

−0.2 |

|

V |

||

|

Dynamic VOL |

(Figures 1, 2; (Note 2)(Note 3)) |

|

|

|||||

|

|

|

|

|

|||||

VIHD |

Minimum High Level |

VCC = 5.0V, TA = 25°C |

|

|

1.6 |

|

V |

||

|

Dynamic Input Voltage |

(Note 2)(Note 4) |

|

|

|

||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

VILD |

Maximum Low Level |

VCC = 5.0V, TA = 25°C |

|

|

1.0 |

|

V |

||

|

Dynamic Input Voltage |

(Note 2)(Note 4) |

|

|

|

||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

Note 2: Plastic DIP package.

Note 3: n = number of device outputs; n−1 outputs switching, each driven 0V to 3V one output @ GND.

Note 4: n = number of device outputs; n outputs switching, n−1 inputs switching 0V to 3V. Input under test switching 3V to threshold (VILD); 0V to threshold (VIHD); f = 1 MHz.

www.fairchildsemi.com |

2 |

Switching Characteristics

over recommended operating free air temperature range

Symbol |

Parameter |

|

Conditions |

From (Input) |

Min |

Max |

Units |

||

|

To (Output) |

||||||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

tPLH |

Propagation Delay Time |

VCC = 4.5V to 5.5V, |

A or B to B or A |

3 |

10 |

ns |

|||

|

LOW-to-HIGH Level Output |

R1 = R2 = 500Ω, |

|||||||

|

|

|

|

|

|||||

tPHL |

Propagation Delay Time |

CL |

= 50 pF |

A or B to B or A |

3 |

10 |

ns |

||

|

HIGH-to-LOW Level Output |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPZH |

Output Enable Time |

|

|

|

|

|

|

|

|

|

|

|

G to A or B |

5 |

20 |

ns |

|||

|

to HIGH Level Output |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPZL |

Output Enable Time |

|

|

|

|

|

|

|

|

|

|

|

G to A or B |

5 |

20 |

ns |

|||

|

to LOW Level Output |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPHZ |

Output Disable Time |

|

|

|

|

|

|

|

|

|

|

|

G to A or B |

2 |

10 |

ns |

|||

|

from HIGH Level Output |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLZ |

Output Disable Time |

|

|

|

|

|

|

|

|

|

|

|

G to A or B |

4 |

15 |

ns |

|||

|

from LOW Level Output |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DM74ALS5245

3 |

www.fairchildsemi.com |

Loading...

Loading...