Fairchild Semiconductor DM74ALS253N, DM74ALS253MX, DM74ALS253M Datasheet

April 1984

Revised February 2000

DM74ALS253

3-STATE Dual 1-of-4 Line Data Selector/Multiplexer

General Description

This Data Selector/Multiplexer contains full on-chip decoding to select one-of-four data sources as a result of a unique two-bit binary code at the Select Inputs. Each of the two Data Selector/Multiplexer circuits have their own separate Data and Output Control inputs and a non-inverting 3- STATE output buffer. The Output Control inputs, when at the high level, place the corresponding output in the high impedance OFF-State. In order to prevent bus access conflicts, output disable times are shorter than output enable times. The Select input buffers incorporate internal overlap features to ensure that select input changes do not cause invalid output transients.

Features

■Advanced oxide-isolated, ion-implanted Schottky TTL process

■Switching performance is guaranteed over full temperature and VCC supply range

■Pin and functional compatible with LS family counterpart

■Improved output transient handling capability

■Output control circuitry incorporates power-up 3-STATE feature

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74ALS253M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

DM74ALS253N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram |

Function Table |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

Select |

|

|

Data Inputs |

|

Output |

Output |

||||

|

|

Inputs |

|

|

|

|

|

Control |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|

B |

A |

|

C0 |

C1 |

C2 |

C3 |

|

G |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

|

X |

X |

X |

X |

|

H |

Z |

|

|

|

L |

L |

|

L |

X |

X |

X |

|

L |

L |

|

|

|

L |

L |

|

H |

X |

X |

X |

|

L |

H |

|

|

|

L |

H |

|

X |

L |

X |

X |

|

L |

L |

|

|

|

L |

H |

|

X |

H |

X |

X |

|

L |

H |

|

|

|

H |

L |

|

X |

X |

L |

X |

|

L |

L |

|

|

|

H |

L |

|

X |

X |

H |

X |

|

L |

H |

|

|

|

H |

H |

|

X |

X |

X |

L |

|

L |

L |

|

|

|

H |

H |

|

X |

X |

X |

H |

|

L |

H |

|

|

|

|

|

|

|

|||||||

|

Address inputs A and B are common to both sections |

|

||||||||||

|

H = HIGH Level |

|

|

|

|

|

|

|

|

|||

L = LOW Level

X = Don't Care

Z = High Impedance

Selector/Multiplexer Data Line 4-of-1 Dual STATE-3 DM74ALS253

© 2000 Fairchild Semiconductor Corporation |

DS006215 |

www.fairchildsemi.com |

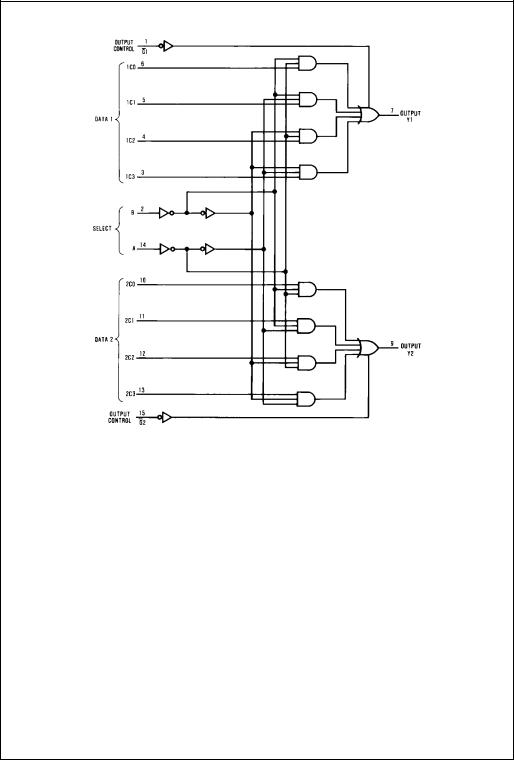

DM74ALS253

Logic Diagram

www.fairchildsemi.com |

2 |

Loading...

Loading...