Philips P89C52UBPN, P89C54UBAA, P89C51UBPN, P89C51UBAA, P89C54NBPN Datasheet

...

INTEGRATED CIRCUITS

89C51/89C52/89C54/89C58

80C51 8-bit microcontroller family 4K/8K/16K/32K Flash

Product specification |

1999 Oct 27 |

Replaces Datasheets 89C51 of 1999 Apr 01 and 89C52/89C54/89C58 of 1999 Apr 01

P s

on o s

Philips Semiconductors |

Product specification |

|

|

|

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

DESCRIPTION

The 89C51/89C52/89C54/89C58 contain a non-volatile FLASH program memory that is parallel programmable. For devices that are serial programmable (In System Programmable (ISP) with a boot loader), see the 89C51RC+/89C51RD+ datasheet.

Both families are Single-Chip 8-bit Microcontrollers manufactured in advanced CMOS process and are derivatives of the 80C51 microcontroller family. All the devices have the same instruction set as the 80C51.

SELECTION TABLE FOR FLASH DEVICES

ROM/EPROM |

RAM Size |

Programmable |

Hardware |

|

Memory Size |

Timer Counter |

Watchdog |

||

(X by 8) |

||||

(X by 8) |

(PCA) |

Timer |

||

|

||||

|

|

|

|

|

Multi-Time Programmable (MTP) devices: |

|

|||

|

|

|

|

|

89C51 |

|

|

|

|

|

|

|

|

|

4 k |

128 |

No |

No |

|

|

|

|

|

|

89C52/54/58 |

|

|

|

|

|

|

|

|

|

8 k/16 k/32 k |

256 |

No |

No |

|

|

|

|

|

|

Serial In-System Programmable devices: |

|

|||

|

|

|

|

|

89C51RC+ |

|

|

|

|

|

|

|

|

|

32 k |

512 |

Yes |

Yes |

|

|

|

|

|

|

89C51RD+ |

|

|

|

|

|

|

|

|

|

64 k |

1024 |

Yes |

Yes |

|

|

|

|

|

|

FEATURES

•80C51 Central Processing Unit

•On-chip FLASH Program Memory

•Speed up to 33 MHz

•Full static operation

•RAM expandable externally to 64 k bytes

•4 level priority interrupt

•6 interrupt sources

•Four 8-bit I/O ports

•Full-duplex enhanced UART

±Framing error detection

±Automatic address recognition

•Power control modes

±Clock can be stopped and resumed

±Idle mode

±Power down mode

•Programmable clock out

•Second DPTR register

•Asynchronous port reset

•Low EMI (inhibit ALE)

•3 16-bit timers

•Wake up from power down by an external interrupt

ORDERING INFORMATION

|

MEMORY SIZE |

MEMORY SIZE |

MEMORY SIZE |

MEMORY SIZE |

TEMPERATURE |

VOLTAGE |

FREQ. |

DWG. |

|

|

RANGE °C |

||||||||

|

4 k × 8 |

8 k × 8 |

16 k × 8 |

32 k × 8 |

RANGE |

(MHz) |

# |

||

|

AND PACKAGE |

||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UBA A |

P89C52UBA A |

P89C54UBA A |

P89C58UBA A |

0 to +70, Plastic |

5 V |

0 to 33 |

SOT187-2 |

|

Leaded Chip Carrier |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UBP N |

P89C52UBP N |

P89C54UBP N |

P89C58UBP N |

0 to +70, Plastic |

5 V |

0 to 33 |

SOT129-1 |

|

Dual In-line Package |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UBB B |

P89C52UBB B |

P89C54UBB B |

P89C58UBB B |

0 to +70, Plastic |

5 V |

0 to 33 |

QFP442 |

|

Quad Flat Pack |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UFA A |

P89C52UFA A |

P89C54UFA A |

P89C58UFA A1 |

±40 to +85, Plastic |

5 V |

0 to 33 |

SOT187-2 |

|

Leaded Chip Carrier |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UFP N |

P89C52UFP N |

P89C54UFP N |

P89C58UFP N1 |

±40 to +85, Plastic |

5 V |

0 to 33 |

SOT129-1 |

|

Dual In-line Package |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

FLASH |

P89C51UFB B |

P89C52UFB B |

P89C54UFB B |

P89C58UFB B1 |

±40 to +85, Plastic |

5 V |

0 to 33 |

QFP442 |

|

Quad Flat Pack |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

1.Contact Philips Sales for availability.

2.SOT not assigned for this package outline.

PART NUMBER DERIVATION

DEVICE NUMBER (P89CXX) |

OPERATING FREQUENCY, MAX (V) |

TEMPERATURE RANGE (B) |

PACKAGE (AA, BB, PN) |

|

|

|

|

|

|

P89C51 FLASH |

|

|

AA = PLCC |

|

P89C52 FLASH |

U = 33 MHz |

B = 0_C to 70_C |

BB = PQFP |

|

P89C54 FLASH |

F = ±40_C to 85_C |

PN = PDIP |

||

|

||||

P89C58 FLASH |

|

|

|

|

|

|

|

|

1999 Oct 27 |

2 |

853±2148 22592 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

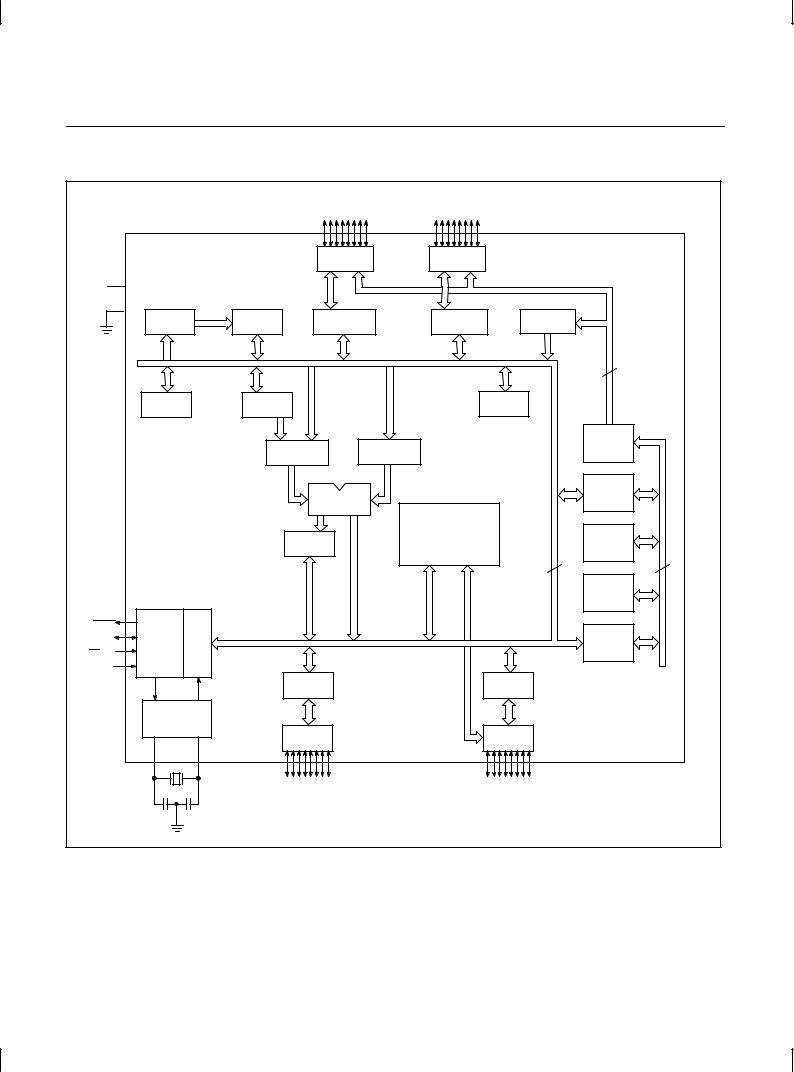

BLOCK DIAGRAM

|

|

|

|

P0.0±P0.7 |

P2.0±P2.7 |

|

|

|

|

|

|

PORT 0 |

PORT 2 |

|

|

|

|

|

|

DRIVERS |

DRIVERS |

|

|

VCC |

|

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

|

RAM ADDR |

RAM |

PORT 0 |

PORT 2 |

FLASH |

|

|

|

REGISTER |

|

LATCH |

LATCH |

|

|

|

|

|

|

|

|

|

|

8 |

|

B |

|

ACC |

|

|

STACK |

|

|

REGISTER |

|

|

|

POINTER |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

PROGRAM |

|

|

|

|

|

TMP1 |

|

ADDRESS |

|

|

|

|

TMP2 |

|

REGISTER |

|

|

|

|

|

ALU |

|

|

BUFFER |

|

|

|

|

|

|

|

|

|

|

|

|

|

SFRs |

|

|

|

|

|

|

|

TIMERS |

|

PC |

|

|

|

|

PSW |

|

INCRE- |

|

|

|

|

|

|

|

|

MENTER |

|

|

|

|

|

|

8 |

16 |

|

|

|

|

|

|

|

PROGRAM |

|

|

|

|

|

|

|

COUNTER |

PSEN |

|

INSTRUCTION |

REGISTER |

|

|

|

|

ALE |

TIMING |

|

|

|

DPTR'S |

||

EAVPP |

AND |

|

|

|

MULTIPLE |

||

CONTROL |

|

|

|

|

|||

RST |

|

|

|

|

|

||

|

PD |

|

|

PORT 1 |

|

PORT 3 |

|

|

|

|

|

LATCH |

|

LATCH |

|

|

OSCILLATOR |

|

|

|

|

||

|

|

|

|

PORT 1 |

|

PORT 3 |

|

|

|

|

|

DRIVERS |

|

DRIVERS |

|

|

XTAL1 |

|

XTAL2 |

|

|

|

|

|

|

|

|

P1.0±P1.7 |

|

P3.0±P3.7 |

|

|

|

|

|

|

|

|

SU01066 |

1999 Oct 27 |

|

|

|

|

3 |

|

|

Philips Semiconductors

80C51 8-bit microcontroller family 4K/8K/16K/32K Flash

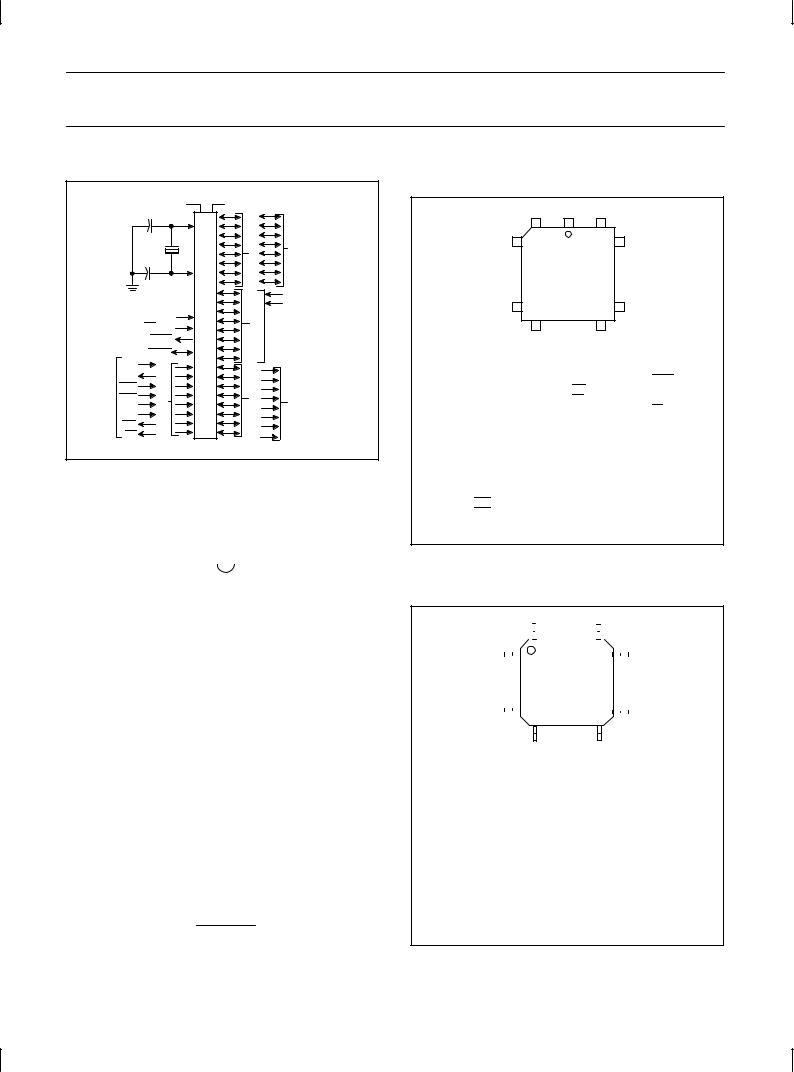

LOGIC SYMBOL

|

|

VCC |

VSS |

|

|

|

XTAL1 |

|

|

|

|

|

0 |

ADDRESS AND |

|

|

|

PORT |

DATA BUS |

|

|

|

|

|

|

|

XTAL2 |

|

|

|

|

|

|

T2 |

|

|

|

1 |

T2EX |

|

|

RST |

|

|

|

|

PORT |

|

|

|

|

EA/VPP |

|

|

|

|

|

|

|

|

|

PSEN |

|

|

FUNCTIONSSECONDARY |

ALE/PROG |

2PORT |

|

|

RxD |

3PORT |

|

||

|

|

|

|

|

|

TxD |

|

|

|

|

INT0 |

|

|

|

|

INT1 |

|

|

ADDRESS BUS |

|

T0 |

|

|

|

|

|

|

|

|

|

T1 |

|

|

|

|

WR |

|

|

|

|

RD |

|

|

|

|

|

|

|

SU00830 |

PIN CONFIGURATIONS

Dual In-Line Package Pin Functions

|

T2/P1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

|

|

|

40 |

|

VCC |

||||

T2EX/P1.1 |

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

39 |

|

P0.0/AD0 |

|||||

|

|

P1.2 |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

38 |

|

P0.1/AD1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.3 |

4 |

|

|

|

37 |

|

P0.2/AD2 |

||

|

|

P1.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

36 |

|

P0.3/AD3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.5 |

6 |

|

|

|

35 |

|

P0.4/AD4 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.6 |

7 |

|

|

|

34 |

|

P0.5/AD5 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.7 |

8 |

|

|

|

33 |

|

P0.6/AD6 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RST |

9 |

|

|

|

32 |

|

P0.7/AD7 |

||

|

|

|

|

|

DUAL |

|

|

|

|

|

|

|

RxD/P3.0 |

10 |

|

31 |

|

EA/VPP |

|||||

|

|

|

|

IN-LINE |

|

|

|

|

|

||

|

TxD/P3.1 |

11 |

PACKAGE |

30 |

|

ALE |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

|

29 |

|

|

|

|

|

INT0/P3.2 |

|

|

|

|

PSEN |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

28 |

|

P2.7/A15 |

||

|

INT1/P3.3 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

T0/P3.4 |

14 |

|

|

|

27 |

|

P2.6/A14 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

T1/P3.5 |

15 |

|

|

|

26 |

|

P2.5/A13 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

|

25 |

|

P2.4/A12 |

||

|

WR/P3.6 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

|

24 |

|

P2.3/A11 |

||

|

RD/P3.7 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL2 |

18 |

|

|

|

23 |

|

P2.2/A10 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL1 |

19 |

|

|

|

22 |

|

P2.1/A9 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

20 |

|

|

|

21 |

|

P2.0/A8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SU01063 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Product specification

89C51/89C52/89C54/89C58

Ceramic and Plastic Leaded Chip Carrier

Pin Functions

|

|

6 |

1 |

40 |

|

|

|

7 |

|

39 |

|

|

|

|

LCC |

|

|

|

|

17 |

|

29 |

|

|

|

18 |

|

28 |

|

Pin |

Function |

Pin |

Function |

Pin |

Function |

1 |

NIC* |

16 |

P3.4/T0 |

31 |

P2.7/A15 |

2 |

P1.0/T2 |

17 |

P3.5/T1 |

32 |

PSEN |

3 |

P1.1/T2EX |

18 |

P3.6/WR |

33 |

ALE |

4 |

P1.2 |

19 |

P3.7/RD |

34 |

NIC* |

5 |

P1.3 |

20 |

XTAL2 |

35 |

EA/VPP |

6 |

P1.4 |

21 |

XTAL1 |

36 |

P0.7/AD7 |

7 |

P1.5 |

22 |

VSS |

37 |

P0.6/AD6 |

8 |

P1.6 |

23 |

NIC* |

38 |

P0.5/AD5 |

9 |

P1.7 |

24 |

P2.0/A8 |

39 |

P0.4/AD4 |

10 |

RST |

25 |

P2.1/A9 |

40 |

P0.3/AD3 |

11 |

P3.0/RxD |

26 |

P2.2/A10 |

41 |

P0.2/AD2 |

12 |

NIC* |

27 |

P2.3/A11 |

42 |

P0.1/AD1 |

13 |

P3.1/TxD |

28 |

P2.4/A12 |

43 |

P0.0/AD0 |

14 |

P3.2/INT0 |

29 |

P2.5/A13 |

44 |

VCC |

15 |

P3.3/INT1 |

30 |

P2.6/A14 |

|

|

* NO INTERNAL CONNECTION |

SU01062 |

|

Plastic Quad Flat Pack Pin Functions

|

|

|

|

|

|

44 |

|

|

|

34 |

|

|

|

|||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

||||

|

|

|

|

|

|

PQFP |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

11 |

|

|

|

|

|

|

|

|

|

|

|

23 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

12 |

|

|

|

22 |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Pin |

Function |

|

|

Pin |

Function |

|

|

|

|

Pin |

Function |

|||||||||

1 |

P1.5 |

16 |

VSS |

31 |

P0.6/AD6 |

|||||||||||||||

2 |

P1.6 |

17 |

NIC* |

32 |

P0.5/AD5 |

|||||||||||||||

3 |

P1.7 |

18 |

P2.0/A8 |

33 |

P0.4/AD4 |

|||||||||||||||

4 |

RST |

19 |

P2.1/A9 |

34 |

P0.3/AD3 |

|||||||||||||||

5 |

P3.0/RxD |

20 |

P2.2/A10 |

35 |

P0.2/AD2 |

|||||||||||||||

6 |

NIC* |

21 |

P2.3/A11 |

36 |

P0.1/AD1 |

|||||||||||||||

7 |

P3.1/TxD |

22 |

P2.4/A12 |

37 |

P0.0/AD0 |

|||||||||||||||

8 |

|

|

|

|

|

23 |

P2.5/A13 |

38 |

VCC |

|||||||||||

P3.2/INT0 |

|

|||||||||||||||||||

9 |

|

|

|

|

|

24 |

P2.6/A14 |

39 |

NIC* |

|||||||||||

P3.3/INT1 |

|

|||||||||||||||||||

10 |

P3.4/T0 |

25 |

P2.7/A15 |

40 |

P1.0/T2 |

|||||||||||||||

11 |

P3.5/T1 |

26 |

|

|

|

41 |

P1.1/T2EX |

|||||||||||||

PSEN |

||||||||||||||||||||

12 |

|

|

|

|

27 |

ALE |

42 |

P1.2 |

||||||||||||

P3.6/WR |

|

|||||||||||||||||||

13 |

|

|

|

28 |

NIC* |

43 |

P1.3 |

|||||||||||||

P3.7/RD |

|

|||||||||||||||||||

14 |

XTAL2 |

29 |

|

|

44 |

P1.4 |

||||||||||||||

EA/VPP |

||||||||||||||||||||

15 |

XTAL1 |

30 |

P0.7/AD7 |

|

|

|

|

|

|

|

||||||||||

* NO INTERNAL CONNECTION |

SU01064 |

|

1999 Oct 27 |

4 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

PIN DESCRIPTIONS

|

|

|

|

PIN NUMBER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MNEMONIC |

DIP |

LCC |

QFP |

TYPE |

NAME AND FUNCTION |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

20 |

22 |

16 |

I |

Ground: 0 V reference. |

|||||||||||||||||||

|

VCC |

40 |

44 |

38 |

I |

Power Supply: This is the power supply voltage for normal, idle, and power-down operation. |

|||||||||||||||||||

|

P0.0±0.7 |

39±32 |

43±36 |

37±30 |

I/O |

Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to |

|||||||||||||||||||

|

|

|

|

|

|

|

|

them float and can be used as high-impedance inputs. Port 0 is also the multiplexed |

|||||||||||||||||

|

|

|

|

|

|

|

|

low-order address and data bus during accesses to external program and data memory. In |

|||||||||||||||||

|

|

|

|

|

|

|

|

this application, it uses strong internal pull-ups when emitting 1s. |

|||||||||||||||||

|

P1.0±P1.7 |

1±8 |

2±9 |

40±44, |

I/O |

Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s |

|||||||||||||||||||

|

|

|

|

|

|

1±3 |

|

written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, |

|||||||||||||||||

|

|

|

|

|

|

|

|

port 1 pins that are externally pulled low will source current because of the internal pull-ups. |

|||||||||||||||||

|

|

|

|

|

|

|

|

(See DC Electrical Characteristics: IIL). Alternate function for Port 1: |

|||||||||||||||||

|

|

|

|

1 |

2 |

40 |

I/O |

|

|

T2 (P1.0): Timer/Counter2 external count input/clockout (see Programmable Clock-Out). |

|||||||||||||||

|

|

|

|

2 |

3 |

41 |

I |

|

|

T2EX (P1.1): Timer/Counter2 reload/capture/direction control. |

|||||||||||||||

|

P2.0±P2.7 |

21±28 |

24±31 |

18±25 |

I/O |

Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s |

|||||||||||||||||||

|

|

|

|

|

|

|

|

written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, |

|||||||||||||||||

|

|

|

|

|

|

|

|

port 2 pins that are externally being pulled low will source current because of the internal |

|||||||||||||||||

|

|

|

|

|

|

|

|

pull-ups. (See DC Electrical Characteristics: IIL). Port 2 emits the high-order address byte |

|||||||||||||||||

|

|

|

|

|

|

|

|

during fetches from external program memory and during accesses to external data memory |

|||||||||||||||||

|

|

|

|

|

|

|

|

that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal |

|||||||||||||||||

|

|

|

|

|

|

|

|

pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses |

|||||||||||||||||

|

|

|

|

|

|

|

|

(MOV @Ri), port 2 emits the contents of the P2 special function register. |

|||||||||||||||||

|

P3.0±P3.7 |

10±17 |

11, |

5, |

I/O |

Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s |

|||||||||||||||||||

|

|

|

|

|

13±19 |

7±13 |

|

written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, |

|||||||||||||||||

|

|

|

|

|

|

|

|

port 3 pins that are externally being pulled low will source current because of the pull-ups. |

|||||||||||||||||

|

|

|

|

|

|

|

|

(See DC Electrical Characteristics: IIL). Port 3 also serves the special features of the |

|||||||||||||||||

|

|

|

|

|

|

|

|

89C51/89C52/89C54/89C58, as listed below: |

|||||||||||||||||

|

|

|

|

10 |

11 |

5 |

I |

|

|

RxD (P3.0): Serial input port |

|||||||||||||||

|

|

|

|

11 |

13 |

7 |

O |

|

|

TxD (P3.1): Serial output port |

|||||||||||||||

|

|

|

|

12 |

14 |

8 |

I |

|

|

|

|

|

|

|

(P3.2): External interrupt |

||||||||||

|

|

|

|

|

|

INT0 |

|||||||||||||||||||

|

|

|

|

13 |

15 |

9 |

I |

|

|

|

|

|

|

(P3.3): External interrupt |

|||||||||||

|

|

|

|

|

|

INT1 |

|||||||||||||||||||

|

|

|

|

14 |

16 |

10 |

I |

|

|

T0 (P3.4): Timer 0 external input |

|||||||||||||||

|

|

|

|

15 |

17 |

11 |

I |

|

|

T1 (P3.5): Timer 1 external input |

|||||||||||||||

|

|

|

|

16 |

18 |

12 |

O |

|

|

|

|

|

(P3.6): External data memory write strobe |

||||||||||||

|

|

|

|

|

|

WR |

|||||||||||||||||||

|

|

|

|

17 |

19 |

13 |

O |

|

|

|

|

(P3.7): External data memory read strobe |

|||||||||||||

|

|

|

|

|

|

RD |

|||||||||||||||||||

|

RST |

9 |

10 |

4 |

I |

Reset: A high on this pin for two machine cycles while the oscillator is running, resets the |

|||||||||||||||||||

|

|

|

|

|

|

|

|

device. An internal diffused resistor to VSS permits a power-on reset using only an external |

|||||||||||||||||

|

|

|

|

|

|

|

|

capacitor to VCC. |

|||||||||||||||||

|

ALE |

30 |

33 |

27 |

O |

Address Latch Enable: Output pulse for latching the low byte of the address during an |

|||||||||||||||||||

|

|

|

|

|

|

|

|

access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the |

|||||||||||||||||

|

|

|

|

|

|

|

|

oscillator frequency, and can be used for external timing or clocking. Note that one ALE |

|||||||||||||||||

|

|

|

|

|

|

|

|

pulse is skipped during each access to external data memory. ALE can be disabled by |

|||||||||||||||||

|

|

|

|

|

|

|

|

setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction. |

|||||||||||||||||

|

|

|

|

29 |

32 |

26 |

O |

Program Store Enable: The read strobe to external program memory. When executing |

|||||||||||||||||

|

PSEN |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

code from the external program memory, |

|

|

is activated twice each machine cycle, |

||||||||||||||

|

|

|

|

|

|

|

|

PSEN |

|||||||||||||||||

|

|

|

|

|

|

|

|

except that two |

PSEN |

activations are skipped during each access to external data memory. |

|||||||||||||||

|

|

|

|

|

|

|

|

|

PSEN |

is not activated during fetches from internal program memory. |

|||||||||||||||

|

|

|

31 |

35 |

29 |

I |

External Access Enable/Programming Supply Voltage: |

|

must be externally held low |

||||||||||||||||

|

EA/VPP |

EA |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

to enable the device to fetch code from external program memory locations 0000H to the |

|||||||||||||||||

|

|

|

|

|

|

|

|

maximum internal memory boundary. If |

EA |

is held high, the device executes from internal |

|||||||||||||||

|

|

|

|

|

|

|

|

program memory unless the program counter contains an address greater than 0FFFH for |

|||||||||||||||||

|

|

|

|

|

|

|

|

4 k devices, 1FFFH for 8 k devices, 3FFFH for 16 k devices, and 7FFFH for 32 k devices. |

|||||||||||||||||

|

|

|

|

|

|

|

|

The value on the |

|

pin is latched when RST is released and any subsequent changes |

|||||||||||||||

|

|

|

|

|

|

|

|

EA |

|||||||||||||||||

|

|

|

|

|

|

|

|

have no effect. This pin also receives the 12.00 V programming supply voltage (VPP) during |

|||||||||||||||||

|

|

|

|

|

|

|

|

FLASH programming. |

|||||||||||||||||

|

XTAL1 |

19 |

21 |

15 |

I |

Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock |

|||||||||||||||||||

|

|

|

|

|

|

|

|

generator circuits. |

|||||||||||||||||

|

XTAL2 |

18 |

20 |

14 |

O |

Crystal 2: Output from the inverting oscillator amplifier. |

|||||||||||||||||||

NOTE: To avoid ªlatch-upº effect at power-on, the voltage on any pin (other than V ) at any time must not be higher than V |

CC |

+ 0.5 V or |

PP |

|

|

VSS ± 0.5 V, respectively. |

|

|

1999 Oct 27 |

5 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

Table 1. 89C51/89C52/89C54/89C58 Special Function Registers

SYMBOL |

DESCRIPTION |

DIRECT |

|

|

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION |

RESET |

|||||||||||||||||||||

ADDRESS |

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

VALUE |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ACC* |

Accumulator |

E0H |

|

E7 |

|

E6 |

E5 |

E4 |

|

E3 |

|

E2 |

E1 |

E0 |

00H |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AUXR# |

Auxiliary |

8EH |

± |

|

± |

|

|

± |

± |

± |

|

± |

|

|

± |

|

AO |

xxxxxxx0B |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AUXR1# |

Auxiliary 1 |

A2H |

± |

|

± |

|

|

± |

± |

|

GF2 |

0 |

|

|

± |

|

DPS |

xxxx00x0B |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B* |

B register |

F0H |

|

F7 |

|

F6 |

F5 |

F4 |

|

F3 |

|

F2 |

F1 |

F0 |

00H |

||||||||||||

DPTR: |

Data Pointer (2 bytes) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DPH |

Data Pointer High |

83H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

DPL |

Data Pointer Low |

82H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

|

|

|

|

AF |

|

AE |

AD |

AC |

|

AB |

|

AA |

A9 |

A8 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IE* |

Interrupt Enable |

A8H |

|

EA |

± |

|

|

ET2 |

ES |

|

ET1 |

|

EX1 |

ET0 |

EX0 |

0x000000B |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BF |

|

BE |

BD |

BC |

|

BB |

|

BA |

B9 |

B8 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IP* |

Interrupt Priority |

B8H |

± |

|

± |

|

|

PT2 |

PS |

|

PT1 |

|

PX1 |

PT0 |

PX0 |

xx000000B |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B7 |

|

B6 |

B5 |

B4 |

|

B3 |

|

B2 |

B1 |

B0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPH# |

Interrupt Priority High |

B7H |

± |

|

± |

|

|

PT2H |

PSH |

PT1H |

PX1H |

PT0H |

PX0H |

xx000000B |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

87 |

|

86 |

|

|

85 |

84 |

83 |

|

82 |

|

|

81 |

|

80 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0* |

Port 0 |

80H |

AD7 |

AD6 |

AD5 |

AD4 |

|

AD3 |

|

AD2 |

AD1 |

AD0 |

FFH |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

97 |

|

96 |

|

|

95 |

94 |

93 |

|

92 |

|

|

91 |

|

90 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1* |

Port 1 |

90H |

± |

|

± |

|

|

± |

± |

± |

|

± |

|

|

T2EX |

T2 |

FFH |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A7 |

|

A6 |

A5 |

A4 |

|

A3 |

|

A2 |

A1 |

A0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P2* |

Port 2 |

A0H |

AD15 |

AD14 |

AD13 |

AD12 |

AD11 |

AD10 |

AD9 |

AD8 |

FFH |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B7 |

|

B6 |

B5 |

B4 |

|

B3 |

|

B2 |

B1 |

B0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3* |

Port 3 |

B0H |

|

RD |

|

|

WR |

|

T1 |

T0 |

|

INT1 |

|

|

INT0 |

|

TxD |

RxD |

FFH |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

PCON#1 |

Power Control |

87H |

SMOD1 |

SMOD0 |

± |

POF2 |

|

GF1 |

|

GF0 |

PD |

IDL |

00xxx000B |

||||||||||||||

|

|

|

|

D7 |

|

D6 |

D5 |

D4 |

|

D3 |

|

D2 |

D1 |

D0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

PSW* |

Program Status Word |

D0H |

|

CY |

|

AC |

F0 |

RS1 |

|

RS0 |

|

OV |

± |

|

P |

000000x0B |

|||||||||||

RACAP2H# |

Timer 2 Capture High |

CBH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

RACAP2L# |

Timer 2 Capture Low |

CAH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

SADDR# |

Slave Address |

A9H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

SADEN# |

Slave Address Mask |

B9H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

SBUF |

Serial Data Buffer |

99H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

xxxxxxxxB |

|

|

|

|

9F |

|

9E |

9D |

9C |

|

9B |

|

9A |

99 |

|

98 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

SCON* |

Serial Control |

98H |

SM0/FE |

SM1 |

SM2 |

REN |

|

TB8 |

|

RB8 |

TI |

RI |

00H |

||||||||||||||

SP |

Stack Pointer |

81H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

07H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

8F |

|

8E |

8D |

8C |

|

8B |

|

8A |

89 |

|

88 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

TCON* |

Timer Control |

88H |

TF1 |

TR1 |

TF0 |

TR0 |

|

IE1 |

|

IT1 |

IE0 |

IT0 |

00H |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

CF |

|

CE |

CD |

CC |

|

CB |

|

CA |

C9 |

C8 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

T2CON* |

Timer 2 Control |

C8H |

TF2 |

EXF2 |

RCLK |

TCLK |

EXEN2 |

|

TR2 |

C/T2 |

|

CP/RL2 |

00H |

||||||||||||||

T2MOD# |

Timer 2 Mode Control |

C9H |

± |

|

± |

|

|

± |

± |

± |

|

± |

|

|

T2OE |

DCEN |

xxxxxx00B |

||||||||||

TH0 |

Timer High 0 |

8CH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

TH1 |

Timer High 1 |

8DH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

TH2# |

Timer High 2 |

CDH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

TL0 |

Timer Low 0 |

8AH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

TL1 |

Timer Low 1 |

8BH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

TL2# |

Timer Low 2 |

CCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

TMOD |

Timer Mode |

89H |

GATE |

|

C/T |

|

M1 |

M0 |

GATE |

|

C/T |

M1 |

M0 |

00H |

|||||||||||||

*SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

± Reserved bits.

1.Reset value depends on reset source.

2.Bit will not be affected by reset.

1999 Oct 27 |

6 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

FLASH EPROM MEMORY

General Description

The 89C51/89C52/89C54/89C58 FLASH reliably stores memory contents even after 100 erase and program cycles. The cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling.

Features

•FLASH EPROM internal program memory with Chip Erase

•Up to 64 k byte external program memory if the internal program memory is disabled (EA = 0)

•Programmable security bits

•100 minimum erase/program cycles for each byte

•10 year minimum data retention

•Programming support available from many popular vendors

OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

RESET

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-on reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-on, the voltage on VCC and RST must come up at the same time for a proper start-up. Ports 1, 2, and 3 will asynchronously be driven to their reset condition when a voltage above VIH1 (min.) is applied to RESET.

The value on the EA pin is latched when RST is deasserted and has no further effect.

1999 Oct 27 |

7 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

LOW POWER MODES

Stop Clock Mode

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power

consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

Design Consideration

•When the idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

Idle Mode

In the idle mode (see Table 2), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

Power-Down Mode

To save even more power, a Power Down mode (see Table 2) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return VCC to the minimum specified operating voltages before the Power Down Mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power Down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power Down the reset or external interrupt should not be executed before VCC is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10ms).

With an external interrupt, INT0 and INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power Down.

ONCE Mode

The ONCE (ªOn-Circuit Emulationº) Mode facilitates testing and debugging of systems without the device having to be removed from the circuit. The ONCE Mode is invoked by:

1.Pull ALE low while the device is in reset and PSEN is high;

2.Hold ALE low as RST is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into a float state, and the other port pins and ALE and PSEN are weakly pulled high. The oscillator circuit remains active. While the device is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

Programmable Clock-Out

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

1.to input the external clock for Timer/Counter 2, or

2.to output a 50% duty cycle clock ranging from 61Hz to 4MHz at a 16MHz operating frequency.

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

Oscillator Frequency

4 (65536 RCAP2H, RCAP2L)

Where (RCAP2H,RCAP2L) = the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will be the same.

Table 2. External Pin Status During Idle and Power-Down Mode

|

|

|

|

|

|

|

|

|

|

MODE |

PROGRAM MEMORY |

ALE |

|

PSEN |

PORT 0 |

PORT 1 |

PORT 2 |

PORT 3 |

|

Idle |

Internal |

1 |

|

1 |

|

Data |

Data |

Data |

Data |

|

|

|

|

|

|

|

|

|

|

Idle |

External |

1 |

|

1 |

|

Float |

Data |

Address |

Data |

|

|

|

|

|

|

|

|

|

|

Power-down |

Internal |

0 |

|

0 |

|

Data |

Data |

Data |

Data |

|

|

|

|

|

|

|

|

|

|

Power-down |

External |

0 |

|

0 |

|

Float |

Data |

Data |

Data |

1999 Oct 27 |

8 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

TIMER 2 OPERATION

Timer 2

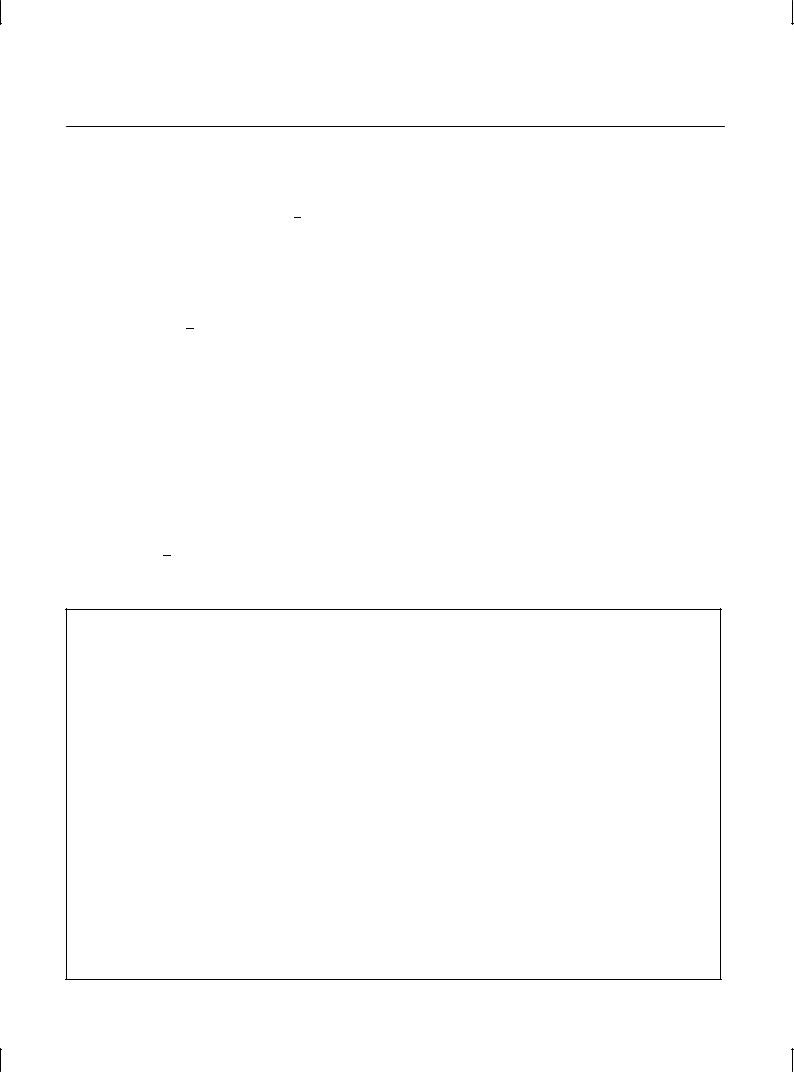

Timer 2 is a 16-bit Timer/Counter which can operate as either an event timer or an event counter, as selected by C/T2* in the special function register T2CON (see Figure 1). Timer 2 has three operating modes: Capture, Auto-reload (up or down counting), and Baud Rate Generator, which are selected by bits in the T2CON as shown in Table 3.

Capture Mode

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2=0, then timer 2 is a 16-bit timer or counter (as selected by C/T2* in T2CON) which, upon overflowing sets bit TF2, the timer 2 overflow bit. This bit can be used to generate an interrupt (by enabling the Timer 2 interrupt bit in the

IE register). If EXEN2= 1, Timer 2 operates as described above, but with the added feature that a 1- to -0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2 like TF2 can generate an interrupt (which vectors to the same location as Timer 2 overflow interrupt. The Timer 2 interrupt service routine can interrogate TF2 and EXF2 to determine which event caused the interrupt). The capture mode is illustrated in Figure 2 (There is no reload value for TL2 and TH2 in this mode. Even when a capture event occurs from T2EX, the counter keeps on counting T2EX pin transitions or osc/12 pulses.).

Figure 3). When reset is applied the DCEN=0 which means Timer 2 will default to counting up. If DCEN bit is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 4 shows Timer 2 which will count up automatically since DCEN=0. In this mode there are two options selected by bit EXEN2 in T2CON register. If EXEN2=0, then Timer 2 counts up to 0FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This causes the Timer 2 registers to be reloaded with the 16-bit value in RCAP2L and RCAP2H. The values in RCAP2L and RCAP2H are preset by software means.

If EXEN2=1, then a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at input T2EX. This transition also sets the EXF2 bit. The Timer 2 interrupt, if enabled, can be generated when either TF2 or EXF2 are 1.

In Figure 5 DCEN=1 which enables Timer 2 to count up or down. This mode allows pin T2EX to control the direction of count. When a logic 1 is applied at pin T2EX Timer 2 will count up. Timer 2 will overflow at 0FFFFH and set the TF2 flag, which can then generate an interrupt, if the interrupt is enabled. This timer overflow also causes the 16±bit value in RCAP2L and RCAP2H to be reloaded into the timer registers TL2 and TH2.

When a logic 0 is applied at pin T2EX this causes Timer 2 to count down. The timer will underflow when TL2 and TH2 become equal to the value stored in RCAP2L and RCAP2H. Timer 2 underflow sets the TF2 flag and causes 0FFFFH to be reloaded into the timer registers TL2 and TH2.

Auto-Reload Mode (Up or Down Counter)

In the 16-bit auto-reload mode, Timer 2 can be configured (as either a timer or counter [C/T2* in T2CON]) then programmed to count up or down. The counting direction is determined by bit DCEN (Down Counter Enable) which is located in the T2MOD register (see

The external flag EXF2 toggles when Timer 2 underflows or overflows. This EXF2 bit can be used as a 17th bit of resolution if needed. The EXF2 flag does not generate an interrupt in this mode of operation.

|

|

|

|

|

|

(MSB) |

|

|

|

|

|

|

|

|

|

|

(LSB) |

|||

|

|

|

|

|

|

TF2 |

|

EXF2 |

RCLK |

TCLK |

EXEN2 |

TR2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

C/T2 |

|

CP/RL2 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Symbol |

Position |

Name and Significance |

|

|

|

|

|

|

|

|

|

|

|

|||||||

TF2 |

T2CON.7 |

Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set |

||||||||||||||||||

|

|

|

|

|

|

|

when either RCLK or TCLK = 1. |

|

|

|

|

|

|

|

|

|

|

|||

EXF2 |

T2CON.6 |

Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and |

||||||||||||||||||

|

|

|

|

|

|

|

EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to the Timer 2 |

|||||||||||||

|

|

|

|

|

|

|

interrupt routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down |

|||||||||||||

|

|

|

|

|

|

|

counter mode (DCEN = 1). |

|

|

|

|

|

|

|

|

|

|

|

||

RCLK |

T2CON.5 |

Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock |

||||||||||||||||||

|

|

|

|

|

|

|

in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock. |

|||||||||||||

TCLK |

T2CON.4 |

Transmit clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its transmit clock |

||||||||||||||||||

|

|

|

|

|

|

|

in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock. |

|||||||||||||

EXEN2 |

T2CON.3 |

Timer 2 external enable flag. When set, allows a capture or reload to occur as a result of a negative |

||||||||||||||||||

|

|

|

|

|

|

|

transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2 = 0 causes Timer 2 to |

|||||||||||||

|

|

|

|

|

|

|

ignore events at T2EX. |

|

|

|

|

|

|

|

|

|

|

|

||

TR2 |

T2CON.2 |

Start/stop control for Timer 2. A logic 1 starts the timer. |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

T2CON.1 |

Timer or counter select. (Timer 2) |

|

|

|

|

|

|

|

|

|

|

||||

C/T2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

0 = Internal timer (OSC/12) |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

1 = External event counter (falling edge triggered). |

|

|

|

|

|

|

|

|

||||

|

|

|

T2CON.0 |

Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN2 = 1. When |

||||||||||||||||

CP/RL2 |

||||||||||||||||||||

|

|

|

|

|

|

|

cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when |

|||||||||||||

EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow.

SU00728

Figure 1. Timer/Counter 2 (T2CON) Control Register

1999 Oct 27 |

9 |

Philips Semiconductors |

Product specification |

|

|

|

|

80C51 8-bit microcontroller family

89C51/89C52/89C54/89C58

4K/8K/16K/32K Flash

Table 3. Timer 2 Operating Modes

|

|

|

|

|

|

RCLK + TCLK |

CP/RL2 |

|

TR2 |

MODE |

|

0 |

0 |

|

1 |

16-bit Auto-reload |

|

|

|

|

|

|

|

0 |

1 |

|

1 |

16-bit Capture |

|

|

|

|

|

|

|

1 |

X |

|

1 |

Baud rate generator |

|

|

|

|

|

|

|

X |

X |

|

0 |

(off) |

|

|

|

|

|

|

|

OSC |

12 |

|

|

|

|

C/T2 = 0 |

|

|

|

|

|

TL2 |

TH2 |

TF2 |

|

|

(8-bits) |

(8-bits) |

|

|

|

|

||

|

C/T2 = 1 |

|

|

|

T2 Pin |

|

Control |

|

|

|

|

|

|

|

|

TR2 |

Capture |

|

|

|

|

|

|

|

|

Transition |

|

|

Timer 2 |

|

Detector |

|

|

Interrupt |

|

|

RCAP2L |

RCAP2H |

|

T2EX Pin |

|

|

|

EXF2 |

|

Control |

|

|

|

|

EXEN2 |

|

|

SU00066 |

|

|

|

|

Figure 2. Timer 2 in Capture Mode

T2MOD |

Address = 0C9H |

|

|

|

|

|

|

|

Reset Value = XXXX XX00B |

|||||

|

Not Bit Addressable |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ð |

|

Ð |

Ð |

|

Ð |

Ð |

Ð |

T2OE |

DCEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

7 |

|

6 |

5 |

|

4 |

3 |

2 |

1 |

0 |

|

|

|

Symbol |

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Ð |

Not implemented, reserved for future use.* |

|

|

|

|

|

|

|

||||||

T2OE |

Timer 2 Output Enable bit. |

|

|

|

|

|

|

|

|

|

||||

DCEN |

Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter. |

|||||||||||||

* User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is

indeterminate.

SU00729

Figure 3. Timer 2 Mode (T2MOD) Control Register

1999 Oct 27 |

10 |

Loading...

Loading...