ON Semiconductor 74FST3245QSR, 74FST3245QS, 74FST3245DWR2, 74FST3245DW, 74FST3245DTR2 Datasheet

...

74FST3245

8-Bit Bus Switch

The ON Semiconductor 74FST3245 is an 8±bit, high performance switch. The device is CMOS TTL compatible when operating between 4 and 5.5 Volts. The device exhibits extremely low RON and adds nearly zero propagation delay. The device adds no noise or ground bounce to the system.

The device consists of an 8±bit switch. Port A is connected to Port B when OE is low. If OE is high, the switch is high Z.

•RON 4 Typical

•Less Than 0.25 ns±Max Delay Through Switch

•Nearly Zero Standby Current

•No Circuit Bounce

•Control Inputs are TTL/CMOS Compatible

•Pin±For±Pin Compatible with QS3245, FST3245, CBT3245

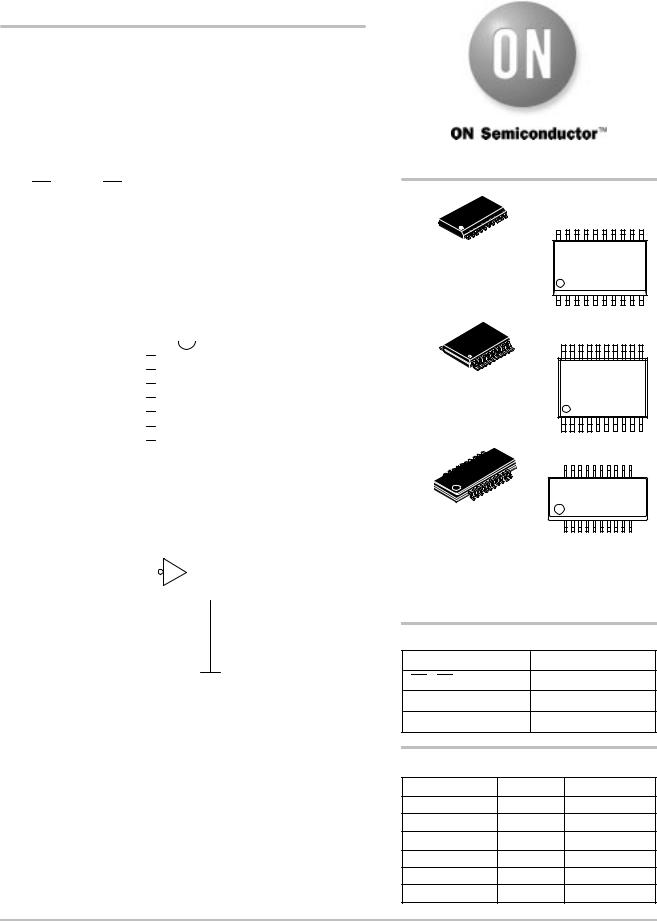

•All Popular Packages: QSOP±20, TSSOP±20, SOIC±20

|

|

|

NC |

1 |

|

|

20 |

|

|

|

VCC |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A0 |

2 |

|

|

19 |

|

|

|

OE |

|

|

|||

|

|

|

|

|

||||||||||||

|

|

|

A1 |

3 |

|

|

18 |

|

|

|

B0 |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A2 |

4 |

|

|

17 |

|

|

|

B1 |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A3 |

5 |

|

|

16 |

|

|

|

B2 |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A4 |

6 |

|

|

15 |

|

|

|

B3 |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A5 |

7 |

|

|

14 |

|

|

|

B4 |

|||||

|

|

|

|

|

||||||||||||

|

|

|

A6 |

|

8 |

|

|

13 |

|

|

|

B5 |

||||

|

|

|

|

|

|

|

||||||||||

|

|

|

A7 |

|

9 |

|

|

12 |

|

|

|

B6 |

||||

|

|

|

|

|

|

|

||||||||||

|

|

|

GND |

|

10 |

|

|

11 |

|

|

|

B7 |

||||

|

|

|

|

|

|

|

||||||||||

|

|

|

Figure 1. 20±Lead Pinout |

|||||||||||||

|

|

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

A |

0 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

18 |

B |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

0 |

||||||

9 |

|

|

|

|

|

|

11 |

|

|

A7 |

|

|

|

|

B7 |

||||

|

|

|

|

||||||

|

Figure 2. Logic Diagram |

||||||||

TRUTH TABLE |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Input |

OE |

|

|

|

Function |

|||

|

L |

|

|

Connect |

|||||

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

Disconnect |

|||||

|

|

|

|

|

|

|

|

|

|

http://onsemi.com

|

|

MARKING |

|

20 |

|

DIAGRAMS |

|

|

|

||

|

20 |

|

|

1 |

|

FST3245 |

|

SO±20 |

|

||

|

AWLYYWW |

||

DW SUFFIX |

|||

|

|||

CASE 751D |

|

||

|

1 |

|

|

20 |

20 |

|

|

|

|

||

1 |

|

FST |

|

|

3245 |

||

TSSOP±20 |

|||

ALYW |

|||

DT SUFFIX |

|||

|

|||

CASE 948E |

|

||

|

1 |

|

|

20 |

20 |

|

|

|

|

||

|

|

FST3245 |

|

1 |

|

AWLYWW |

|

QSOP±20 |

1 |

|

|

|

|

||

QS SUFFIX |

|

||

CASE 492A |

|

||

A |

= Assembly Location |

||

L, WL |

= Wafer Lot |

|

|

Y |

= Year |

|

|

W, WW = Work Week |

|

||

PIN NAMES |

|

|

|

Pin |

|

Description |

|

OE1, OE2 |

Bus Switch Enables |

||

1A, 2A |

|

Bus A |

|

1B, 2B |

|

Bus B |

|

ORDERING INFORMATION |

|

||

Device |

Package |

Shipping |

|

74FST3245DW |

SO±20 |

38 Units/Rail |

|

74FST3245DWR2 |

SO±20 |

1000 Units/Reel |

|

74FST3245DT |

TSSOP±20 |

75 Units/Rail |

|

74FST3245DTR2 |

TSSOP±20 |

2500 Units/Reel |

|

74FST3245QS |

QSOP±20 |

55 Units/Rail |

|

74FST3245QSR |

QSOP±20 |

2500 Units/Reel |

|

Semiconductor Components Industries, LLC, 2001 |

1 |

Publication Order Number: |

August, 2001 ± Rev. 0 |

|

74FST3245/D |

74FST3245

MAXIMUM RATINGS

Symbol |

|

Parameter |

Value |

Unit |

|

|

|

|

|

VCC |

DC Supply Voltage |

|

±0.5 to 7.0 |

V |

VI |

DC Input Voltage |

|

±0.5 to 7.0 |

V |

VO |

DC Output Voltage |

|

±0.5 to 7.0 |

V |

IIK |

DC Input Diode Current |

VI GND |

±50 |

mA |

IOK |

DC Output Diode Current |

VO GND |

±50 |

mA |

IO |

DC Output Sink Current |

|

128 |

mA |

ICC |

DC Supply Current per Supply Pin |

|

100 |

mA |

IGND |

DC Ground Current per Ground Pin |

|

100 |

mA |

TSTG |

Storage Temperature Range |

|

±65 to 150 |

C |

TL |

Lead Temperature, 1 mm from Case for 10 Seconds |

260 |

C |

|

TJ |

Junction Temperature Under Bias |

|

150 |

C |

JA |

Thermal Resistance (Note 1) |

SOIC |

96 |

C/W |

|

|

TSSOP |

128 |

|

|

|

QSOP |

200 |

|

|

|

|

|

|

MSL |

Moisture Sensitivity |

|

Level 1 |

|

|

|

|

|

|

FR |

Flammability Rating |

Oxygen Index: 28 to 34 |

UL 94 V±0 @ 0.125 in |

|

VESD |

ESD Withstand Voltage |

Human Body Model (Note 2) |

2000 |

V |

|

|

Machine Model (Note 3) |

|

|

|

|

|

200 |

|

ILATCH±UP |

Latch±Up Performance |

Above VCC and Below GND at 85 C (Note 4) |

500 |

mA |

Maximum Ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum±rated conditions is not implied. Functional operation should be restricted to the Recommended Operating Conditions.

1.Measured with minimum pad spacing on an FR4 board, using 10 mm±by±1 inch, 2±ounce copper trace with no air flow.

2.Tested to EIA/JESD22±A114±A.

3.Tested to EIA/JESD22±A115±A.

4.Tested to EIA/JESD78.

RECOMMENDED OPERATING CONDITIONS

Symbol |

|

Parameter |

Min |

Max |

Unit |

|

|

|

|

|

|

VCC |

Supply Voltage |

Operating, Data Retention Only |

4.0 |

5.5 |

V |

VI |

Input Voltage |

(Note ) |

0 |

5.5 |

V |

VO |

Output Voltage |

(HIGH or LOW State) |

0 |

VCC |

V |

TA |

Operating Free±Air Temperature |

|

±40 |

85 |

C |

t/ V |

Input Transition Rise or Fall Rate |

Switch Control Input |

0 |

5 |

ns/V |

|

|

Switch I/O |

0 |

DC |

|

|

|

|

|

|

|

5. Unused control inputs may not be left open. All control inputs must be tied to a high or low logic input voltage level.

http://onsemi.com

2

74FST3245

DC ELECTRICAL CHARACTERISTICS

|

|

|

VCC |

TA = ±40 C to 85 C |

|

||

Symbol |

Parameter |

Conditions |

(V) |

Min |

Typ* |

Max |

Unit |

|

|

|

|

|

|

|

|

VIK |

Clamp Diode Resistance |

IIN = ±18mA |

4.5 |

|

|

±1.2 |

V |

VIH |

High±Level Input Voltage |

|

4.0 to 5.5 |

2.0 |

|

|

V |

VIL |

Low±Level Input Voltage |

|

4.0 to 5.5 |

|

|

0.8 |

V |

II |

Input Leakage Current |

0 VIN 5.5 V |

5.5 |

|

|

1.0 |

A |

IOZ |

OFF±STATE Leakage Current |

0 A, B VCC |

5.5 |

|

|

1.0 |

A |

RON |

Switch On Resistance (Note 6) |

VIN = 0 V, IIN = 64 mA |

4.5 |

|

4 |

7 |

|

|

|

VIN = 0 V, IIN = 30 mA |

4.5 |

|

4 |

7 |

|

|

|

VIN = 2.4 V, IIN = 15 mA |

4.5 |

|

8 |

15 |

|

|

|

VIN = 2.4 V, IIN = 15 mA |

4.0 |

|

11 |

20 |

|

ICC |

Quiescent Supply Current |

VIN = VCC or GND, IOUT = 0 |

5.5 |

|

|

3 |

A |

ICC |

Increase In ICC per Input |

One input at 3.4 V, Other inputs at VCC or GND |

5.5 |

|

|

2.5 |

mA |

*Typical values are at VCC = 5.0 V and TA = 25 C.

6. Measured by the voltage drop between A and B pins at the indicated current through the switch.

AC ELECTRICAL CHARACTERISTICS

|

|

|

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA = ±40 C to 85 C |

|

|

|||

|

|

|

|

VCC = 4.5 to 5.5 V |

|

VCC = 4.0 V |

|

|||

Symbol |

Parameter |

Conditions |

Figures |

Min |

|

Max |

|

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

tPHL, |

Prop Delay Bus to Bus |

VI = OPEN |

3 and 4 |

|

|

0.25 |

|

|

0.25 |

ns |

tPLH |

(Note 7) |

|

|

|

|

|

|

|

|

|

tPZH, |

Output Enable Time |

VI = 7 V for tPZL |

3 and 4 |

1.5 |

|

5.9 |

|

|

6.4 |

ns |

tPZL |

|

VI = OPEN for tPZH |

|

|

|

|

|

|

|

|

tPHZ, |

Output Disable Time |

VI = 7 V for tPLZ |

3 and 4 |

1.5 |

|

6.0 |

|

|

5.7 |

ns |

tPLZ |

|

VI = OPEN for tPHZ |

|

|

|

|

|

|

|

|

7.This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On resistance of the switch and the 50 pF load capacitance, when driven by an ideal voltage source (zero output impedance).

CAPACITANCE (Note 8)

Symbol |

Parameter |

|

|

|

Conditions |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

CIN |

Control Pin Input Capacitance |

VCC = 5.0 V |

|

3 |

|

pF |

||

CI/O |

Input/Output Capacitance |

VCC, |

|

= 5.0 V |

|

5 |

|

pF |

OE |

|

|

||||||

8. TA = 25 C, f = 1 MHz, Capacitance is characterized but not tested.

http://onsemi.com

3

Loading...

Loading...