Texas Instruments UCC3946PWTR, UCC3946PW, UCC3946N, UCC3946DTR, UCC3946D Datasheet

...

UCC1946

UCC2946

UCC3946

Microprocessor Supervisor with Watchdog Timer

FEATURES

•Fully Programmable Reset Threshold

•Fully Programmable Reset Period

•Fully Programmable Watchdog Period

•2% Accurate Reset Threshold

•VDD Can Go as Low as 2V

•18 A Maximum IDD

•Reset Valid Down to 1V

DESCRIPTION

The UCC3946 is designed to provide accurate microprocessor supervision, including reset and watchdog functions. During power up, the IC asserts a reset signal RES with VDD as low as 1V. The reset signal remains asserted until the VDD voltage rises and remains above the reset threshold for the reset period. Both reset threshold and reset period are programmable by the user. The IC is also resistant to glitches on the VDD line. Once RES has been deasserted, any drops below the threshold voltage need to be of certain time duration and voltage magnitude to generate a reset signal. These values are shown in Figure 1. An I/O line of the microprocessor may be tied to the watchdog input (WDI) for watchdog functions. If the I/O line is not toggled within a set watchdog period, programmable by the user, WDO will be asserted. The watchdog function will be disabled during reset conditions.

The UCC3946 is available in 8-pin SOIC(D), 8-pin DIP (N or J) and 8-pin TSSOP(PW) packages to optimize board space.

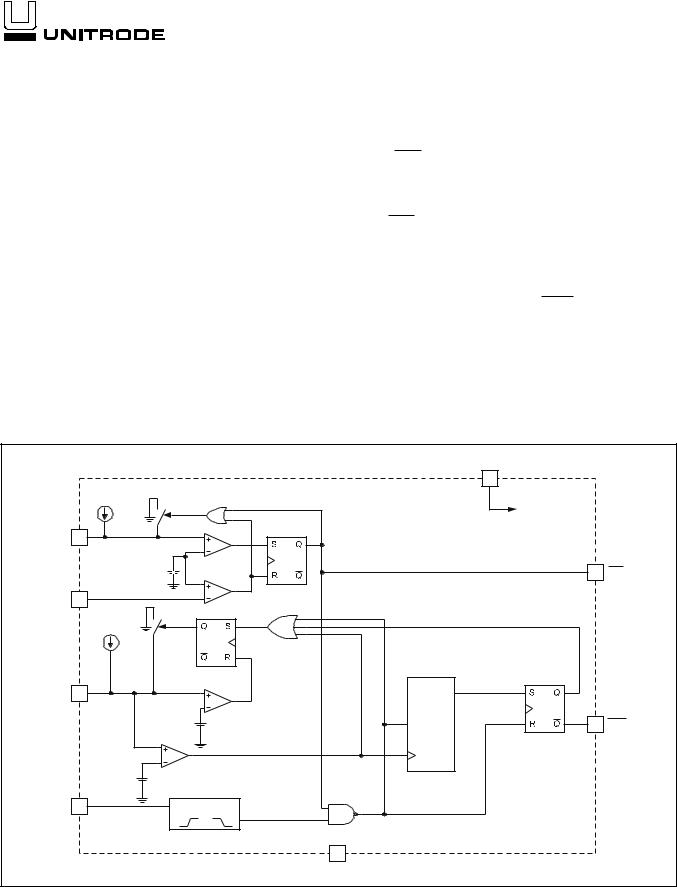

BLOCK DIAGRAM

|

|

|

|

|

VDD |

|

|

|

|

|

|

8 |

|

|

|

400nA |

|

|

POWER TO |

|

|

|

|

|

|

|

|

|

|

|

|

|

CIRCUITRY |

|

RP |

4 |

|

|

|

|

|

|

|

1.235V . |

|

|

3 |

RES |

RTH |

2 |

|

|

|

|

|

|

|

POWER ON RESET |

|

|

|

|

|

|

400nA |

|

|

|

|

|

|

|

8-BIT COUNTER |

|

|

|

WP |

6 |

|

|

A3 |

|

|

|

|

|

|

A2 |

|

|

|

|

100mV |

CLR |

A1 |

5 |

WDO |

|

|

|

|

A0 |

|

|

|

|

|

CLK |

|

|

|

|

|

1.235V |

|

|

|

|

|

|

WATCHDOG TIMING |

|

|

|

|

WDI |

7 |

EDGE DETECT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

GND |

|

|

UDG-98001 |

|

|

|

|

|

|

|

Note: Pinout represents the 8-pin TSSOP package.

SLUS247B - FEBRUARY 2000

UCC1946

UCC2946

UCC3946

ABSOLUTE MAXIMUM RATINGS |

CONNECTION DIAGRAM |

VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10V Storage Temperature . . . . . . . . . . . . . . . . . . . –65°C to +150°C Junction Temperature. . . . . . . . . . . . . . . . . . . –55°C to +150°C Lead Temperature (Soldering, 10 sec.) . . . . . . . . . . . . . +300°C

Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the Databook for thermal limitations and considerations of packages.

SOIC-8, TSSOP-8, DIL-8 (Top View) D, PW, N or J Package

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

1 |

|

|

|

8 |

VDD |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RTH |

2 |

|

|

|

7 |

WDI |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RES |

3 |

|

|

|

|

6 |

WP |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RP |

4 |

|

|

|

|

5 |

WDO |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ELECTRICAL CHARACTERISTICS: Unless otherwise specified, VDD = 2.1V to 5.5V for UCC1946 and UCC2946;

VDD = 2V to 5.5V for UCC3946; TA = 0°C to 70°C for UCC3946, –40°C to 95°C for UCC2946, and –55°C to 125°C for UCC1946; TA = TJ

PARAMETERS |

TEST CONDITIONS |

MIN |

|

TYP |

|

MAX |

MIN |

TYP |

MAX |

UNITS |

||

|

|

|

|

|

UCC3946 |

|

UCC1946 & UCC2946 |

|||||

Operating Voltage |

|

|

|

2.0 |

|

|

|

5.5 |

2.1 |

|

5.5 |

V |

Supply Current |

|

|

|

|

|

10 |

|

18 |

|

12 |

18 |

A |

Minimum VDD |

(Note 1) |

|

|

|

|

1 |

|

|

1.1 |

V |

||

Reset Section |

|

|

|

|

|

|

|

|

|

|

|

|

Reset Threshold |

VDD Rising |

1.210 |

|

1.235 |

|

1.260 |

1.170 |

1.235 |

1.260 |

V |

||

Threshold Hysteresis |

|

|

|

|

|

15 |

|

|

|

15 |

|

mV |

Input Leakage |

|

|

|

|

|

|

|

5 |

|

|

5 |

nA |

Output High Voltage |

ISOURCE = 2mA |

VDD – |

|

|

|

|

VDD – |

|

|

V |

||

|

|

|

|

0.3 |

|

|

|

|

0.3 |

|

|

|

Output Low Voltage |

ISINK = 2mA |

|

|

|

|

0.1 |

|

|

0.1 |

V |

||

|

VDD = 1V, ISINK = 20uA |

|

|

|

|

0.2 |

|

|

0.4 |

V |

||

VDD to Output Delay |

VDD = -1mV/ s (Note 2) |

|

|

120 |

|

|

|

120 |

|

s |

||

Reset Period |

CRP = 64nF |

160 |

|

200 |

|

260 |

140 |

200 |

320 |

ms |

||

Watchdog Section |

|

|

|

|

|

|

|

|

|

|

|

|

WDI Input High |

|

|

|

0.7· |

|

|

|

|

0.7· |

|

|

V |

|

|

|

|

VDD |

|

|

|

|

VDD |

|

|

|

WDI Input Low |

|

|

|

|

|

|

|

0.3· |

|

|

0.3· |

V |

|

|

|

|

|

|

|

|

VDD |

|

|

VDD |

|

Watchdog Period |

CWP = 64nF |

1.12 |

|

1.60 |

|

2.08 |

0.96 |

1.60 |

2.56 |

s |

||

Watchdog Pulse Width |

|

|

|

50 |

|

|

|

|

50 |

|

|

ns |

Output High Voltage |

ISOURCE = 2mA |

VDD – |

|

|

|

|

VDD – |

|

|

V |

||

|

|

|

|

0.3 |

|

|

|

|

0.3 |

|

|

|

Output Low Voltage |

ISINK = 2mA |

|

|

|

|

0.1 |

|

|

0.1 |

V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: This is the minimum supply voltage where RES is considered valid.

Note 2: Guaranteed by design. Not 100% tested in production.

2

Loading...

Loading...