TEXAS INSTRUMENTS UCC5686, UCC5687 Technical data

! |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UCC5686, UCC5687 |

|||||||||||||

|

27-LINE 3 V - 5 V LVD TERMINATOR FOR WIDE ULTRA2, ULTRA3, |

||||||||||||||||||||||||||||||||||||||||||

|

ULTRA160, AND ULTRA320 SCSI WITH INTEGRATED SPI 3 DELAY |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SLUS459B – OCTOBER 2000 – REVISED APRIL 2001 |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

D SCSI SPI-2, SPI-3, Ultra2, Ultra3, Ultra160, |

|

|

|

|

|

|

|

|

|

|

|

|

|

PM PACKAGE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

Ultra320 SCSI Compliance |

|

|

|

L24+ |

L24– L23+ |

|

|

|

|

|

|

|

(TOP VIEW) |

|

L5+ L5– L22+ |

|

L22– |

|

|

|

|

|||||||||||||||||||||

D |

Smallest Footprint |

|

|

|

|

L23– L9+ L9– L8+ L8– L7+ L7– L6+ L6– |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

D |

Lowest Channel |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Capacitance, 2 pF |

L25– |

|

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 |

|

|

|

|

|

{DISCNCT1 |

|||||||||||||||||||||||||||||||||

D |

Less than 0.5-pF Capacitance |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

|||||||||

L25+ |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

{DISCNCT2 |

|||||||||

|

Differential Between Pairs |

L26– |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

L21– |

|||||||

D |

2.7 V to 5.25 V Operation |

L26+ |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

L21+ |

|||||||

D |

Differential Failsafe Bias |

L27– |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

L20– |

|||||||

D |

Built–in SPI-3 Mode |

L27+ |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

L20+ |

|||||||

|

Change/Filter Delay |

STRMPWR |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

|

L19– |

|||||||

D |

64-Pin Low Profile QFP |

PTRMPWR |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

|

L19+ |

|||||||

REG |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

DIFSENS |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

SGND |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

DIFFB |

||||||||

|

|

PGND |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

L18– |

||||||||

|

|

LVD |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

L18+ |

||||||||

|

|

L10– |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

L17– |

||||||||

|

|

L10+ |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

L17+ |

||||||||

|

|

L11– |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

L16– |

||||||||

|

|

L11+ |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

L16+ |

||||||||

|

|

|

|

17 18 19 |

20 21 22 23 24 25 26 27 28 |

29 30 31 |

32 |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L12+ |

L12– L13+ |

|

L13– L1+ L1– L2+ L2– L3+ L3– L4+ L4– |

|

L14+ L14– L15+ |

|

L15– |

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

{For the UCC5687, Pin 47 is |

DISCNCT1 |

and Pin 48 is |

DISCNCT2. |

|

|||||||||||||||||||||||||||||||||||||

description

The UCC5686 is a twenty-seven line active terminator for low-voltage-differential (LVD) SCSI networks. This LVD SCSI-only design allows the user to reach peak bus performance, while reducing system cost. The device is designed as an active Y-terminator to improve the frequency response of the LVD SCSI Bus. Designed with a 2-pF (typical) channel capacitance, the UCC5686 allows for minimal bus loading for a maximum number of peripherals. With the UCC5686, the designer is able to comply with the Ultra2, Ultra3, Ultra160, and Ultra320 SCSI specifications. The UCC5686 also provides a much-needed system migration path for the ever improving SCSI system standards.

This device is available in the 64-pin low-profile QFP package for ease of layout use.

Single-ended (SE) and high-voltage differential (HVD) SCSI drivers are not supported.

AVAILABLE OPTIONS

|

DISCONNECT |

PACKAGED DEVICES† |

|

TA |

STATUS |

LOW PROFILE QFP |

|

|

|

(PM) |

|

0° C to 70° C |

REGULAR |

UCC5686PM |

|

|

|

||

REVERSE |

UCC5687PM |

||

|

†The PM package is available taped and reeled. Add TR suffix to device type (e.g. UCC5686PMTR) to order quantities of 1000 devices per reel.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2000, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

1 |

UCC5686, UCC5687 |

|

|

|

|

|

|

|

|

|

|

! |

|

27-LINE 3 V - 5 V LVD TERMINATOR FOR WIDE ULTRA2, ULTRA3, |

|

|

||||||||||

ULTRA160, AND ULTRA320 SCSI WITH INTEGRATED SPI 3 DELAY |

|

|

||||||||||

SLUS459B – OCTOBER 2000 – REVISED APRIL 2001 |

|

|

|

|

|

|

||||||

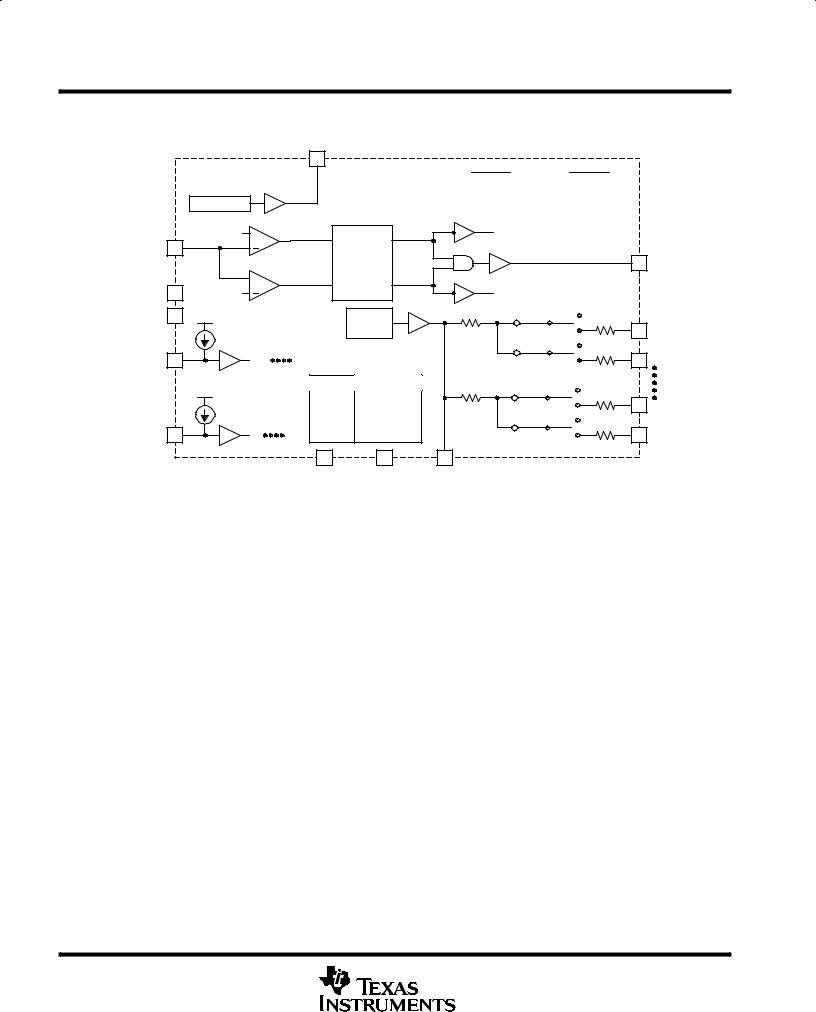

block diagram |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIFSENS |

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

|

|

|

|

|

–15mA |

≤ I |

SOURCE |

≤ |

–5mA |

|

*FOR THE UCC5687 PIN 47 IS DISCNCT1 AND PIN 48 IS DISCNCT2. |

|

|

|||

|

50 A ≤ ISINK ≤ |

200 A |

|

|

|

|||||||

|

|

|

|

|

|

|

||||||

|

REF 1.3V |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

1.3V +/– 0.1V |

|

|

|

|

|

|

|

2.15 V |

+ |

|

|

|

|

HPD |

|

|

|

||

DIFFB |

39 |

|

|

|

|

|

100 ms TO |

|

|

|

|

|

|

|

|

|

|

|

|

300 ms |

|

|

12 |

LVD |

|

|

|

|

|

|

|

|

DELAY/ |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

+ |

|

|

FILTER |

|

|

|

|

|

STRMPWR |

7 |

0.6V |

|

|

|

|

|

SE |

|

|

|

|

PTRMPWR |

8 |

|

|

|

|

|

|

REF |

125 |

52 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

1.25V |

– |

+ |

22 |

L1– |

|

|

|

|

|

|

|

|

|

+56mV |

|

|

|

|

|

|

|

|

|

|

SOURCE/SINK |

|

52 |

|

|

|

*DISCNCT1 |

48 |

|

|

L10 |

L27 |

REGULATOR |

+ |

– |

21 |

L1+ |

||

|

|

|

|

|

|

|

|

|

+56mV |

|

|

|

|

|

|

|

|

|

MODE |

ALL SWITCHES |

125 |

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

|

|

|

|

|

|

|

|

SE |

|

OPEN |

|

|

|

|

|

|

|

|

|

|

|

– |

+ |

5 |

L27– |

||

|

|

|

|

|

|

LVD |

|

DOWN |

+56mV |

|

|

|

|

|

|

|

|

|

HVD |

|

OPEN |

|

52 |

|

|

|

|

|

|

|

|

L9 DISCNCT |

OPEN |

|

|

|

||

*DISCNCT2 |

47 |

|

|

L1 |

+ |

– |

6 |

L27+ |

||||

|

|

|

|

|

|

|

|

|

+56mV |

|

|

|

|

|

|

|

|

|

10 |

|

11 |

9 |

|

|

|

|

|

|

|

|

|

SGND |

|

PGND |

REG |

|

|

UDG-00123 |

|

|

|

|

|

|

|

|

|

|

|

|

|

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†‡

Input voltage VIN (STRMPWR, PTRMPWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . 6 V |

|

Signal line input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . 0 V to 5 |

V |

Regulator output current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 0.75 |

A |

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

–55° C to 150° C |

|

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

–55° C to 150° C |

|

Lead temperature (soldering, 10 seconds) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 300° C |

|

†Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

‡Unless otherwise indicated, voltages are reference to ground and currents are positive into and negative out of the specified terminals. Consult Packaging Section of the Interface Products Data Book (TI Literature Number SLUD002) for thermal limitations and considerations of packages.

All voltages are referenced to GND.

2 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

! |

UCC5686, UCC5687 |

|

|

27-LINE 3 V - 5 V LVD TERMINATOR FOR WIDE ULTRA2, ULTRA3, |

|

|

ULTRA160, AND ULTRA320 SCSI WITH INTEGRATED SPI 3 DELAY |

|

|

SLUS459B – OCTOBER 2000 – REVISED APRIL 2001 |

|

|

|

|

electrical characteristics over recommended operating free-air temperature range, xTRMPWR = 2.7 V to 5.25 V, TA = 0_C to 70_C, DISCNCT1 = DISCNCT2 = 0 V for UCC5686,

DISCNCT1 = DISCNCT2 = open for UCC5687, TA = TJ. (unless otherwise noted)

PARAMETER |

|

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

|

|

xTRMPWR Supply Current Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

xTRMPWR supply current |

|

LVD mode |

|

|

|

65 |

mA |

|

|

|

|

|

|

|

|

|

Disabled terminator |

|

|

|

500 |

µ A |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

1.25 V Regulator Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.25 V regulator |

|

0.5 V ≤ VCM ≤ 2.0 V, |

See Note 1 |

1.15 |

1.25 |

1.35 |

V |

Regulator source current |

|

VREG = 0 V |

|

|

–300 |

–240 |

mA |

Regulator sink current |

|

VREG = 3.0 V |

|

240 |

300 |

|

mA |

1.3 V (DIFSENS) Regulator Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.3 V regulator |

|

–5mA ≤ IDIFSENS ≤ 50 µ A |

|

1.2 |

1.3 |

1.4 |

V |

Short-circuit source current |

|

VDIFSENS = 0 V |

|

–5 |

–8 |

–15 |

mA |

Short-circuit sinkcurrent |

|

VDIFSENS = 2.75 V |

|

50 |

|

200 |

µ A |

Differential Termination Section (Applies to each line pair 1–27) |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Differential bias voltage |

|

|

|

100 |

|

125 |

mV |

|

|

|

|

|

|

|

|

Differential impedance |

|

|

|

100 |

105 |

110 |

Ω |

|

|

|

|

|

|

|

|

Common-mode bias voltage |

|

L+ and L– shorted together |

|

1.15 |

1.25 |

1.35 |

V |

|

|

|

|

|

|

|

|

Common-mode impedance |

|

L+ and L– shorted together, |

See Note 2 |

110 |

140 |

165 |

Ω |

|

|

|

|

|

|

|

|

Disconnected Termination Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output leakage current |

|

|

|

|

10 |

400 |

nA |

|

|

|

|

|

|

|

|

Output capacitance |

|

SE measurement to GND, |

See Note 3 |

|

|

3 |

pF |

|

|

|

|

|

|

|

|

Disconnect Control (DISCNCT1) or (DISNCNT2) and DIFFB Input Section |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

DISCNCT threshold voltage |

|

|

|

0.8 |

1.3 |

2.0 |

V |

|

|

|

|

|

|

|

|

DISCNCT input current |

|

VDISCNCT = 0 V and 2.0 V |

|

–30 |

|

–10 |

µ A |

DIFFB SE to LVD threshold voltage |

|

|

|

0.5 |

|

0.7 |

V |

|

|

|

|

|

|

|

|

DIFFB LVD to HPD threshold voltage |

|

|

|

1.9 |

|

2.4 |

V |

|

|

|

|

|

|

|

|

DIFFB Input current |

|

0 V ≤ VDIFFB ≤ 2.75 V |

|

–10 |

|

10 |

µ A |

Low-Voltage Differential (LVD) Status Bit Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Source current |

|

VLOAD = 2.4 V |

|

|

–6 |

–4 |

mA |

Sink current |

|

VLOAD = 0.4 V |

|

2 |

5 |

|

mA |

Time Delay/Filter Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode change delay |

|

(See Note 4) |

|

100 |

190 |

300 |

ms |

|

|

|

|

|

|

|

|

Thermal Shutdown Section |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Thermal shutdown threshold |

|

For increasing temperature |

|

140 |

155 |

170 |

_C |

|

|

|

|

|

|

|

|

Thermal shutdown hysteresis |

|

|

|

|

10 |

|

_C |

|

|

|

|

|

|

|

|

NOTES: 1. VCM is applied to all L+ and L– lines simultaneously.

2.0V * 0.5 V

2.ZCM + IVCM (max) * IVCM (max) , VCM(max) = 2.0 V, VCM(min) = 0.5 V

3.Ensured by design, not production tested.

4.A new mode change can begin any time after a previous mode change has been detected.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

3 |

Loading...

Loading...