Philips 74HCT154U, 74HCT154N3, 74HCT154N, 74HCT154D, 74HC154U Datasheet

...

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

∙The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT154

4-to-16 line decoder/demultiplexer

Product specification |

|

September 1993 |

|||||

File under Integrated Circuits, IC06 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

|

|

4-to-16 line decoder/demultiplexer |

74HC/HCT154 |

|

|

|

|

FEATURES

·16-line demultiplexing capability

·Decodes 4 binary-coded inputs into one of 16 mutually exclusive outputs

·2-input enable gate for strobing or expansion

·Output capability: standard

·ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT154 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns

The 74HC/HCT154 decoders accept four active HIGH binary address inputs and provide 16 mutually exclusive active LOW outputs.

The 2-input enable gate can be used to strobe the decoder to eliminate the normal decoding “glitches” on the outputs, or it can be used for the expansion of the decoder.

The enable gate has two AND’ed inputs which must be LOW to enable the outputs.

The “154” can be used as a 1-to-16 demultiplexer by using one of the enable inputs as the multiplexed data input.

When the other enable is LOW, the addressed output will follow the state of the applied data.

SYMBOL |

PARAMETER |

CONDITIONS |

|

TYPICAL |

UNIT |

|||||

|

|

|

||||||||

HC |

|

HCT |

||||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

tPHL/ tPLH |

propagation delay An, |

|

n to |

|

n |

CL = 15 pF; VCC = 5 V |

11 |

|

13 |

ns |

E |

Y |

|

||||||||

CI |

input capacitance |

|

3.5 |

|

3.5 |

pF |

||||

CPD |

power dissipation capacitance per package |

notes 1 and 2 |

60 |

|

60 |

pF |

||||

Notes

1. CPD is used to determine the dynamic power dissipation (PD in mW): PD = CPD ´ VCC2 ´ fi + å (CL ´ VCC2 ´ fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

å (CL ´ VCC2 ´ fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC - 1.5 V

ORDERING INFORMATION

See “74HC/HCT/HCU/HCMOS Logic Package Information”.

September 1993 |

2 |

Philips Semiconductors |

|

|

|

|

|

|

|

Product specification |

|

|

|

|

|

|

|

|

|

|

|

4-to-16 line decoder/demultiplexer |

|

|

|

|

|

|

|

74HC/HCT154 |

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

PIN NO. |

|

|

SYMBOL |

NAME AND FUNCTION |

|||||

|

|

|

|

|

|

|

|

||

1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 13, 14, 15, 16, 17 |

|

|

|

0 to |

|

15 |

outputs (active LOW) |

||

|

|

Y |

Y |

||||||

18, 19 |

|

|

|

1 |

enable inputs (active LOW) |

||||

|

E |

0, |

E |

||||||

12 |

|

|

GND |

ground (0 V) |

|||||

23, 22, 21, 20 |

|

|

A0 to A3 |

address inputs |

|||||

24 |

|

|

VCC |

positive supply voltage |

|||||

|

|

|

|

(a) |

(b) |

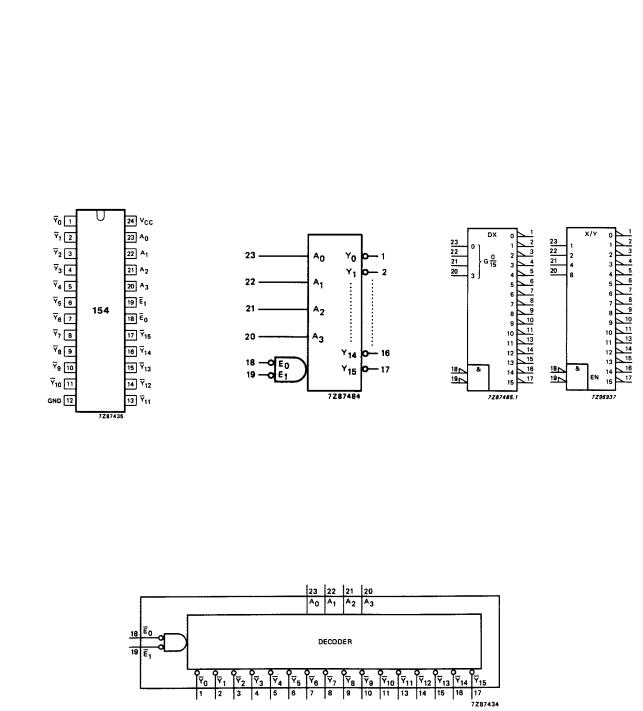

Fig.1 Pin configuration. |

|

Fig.2 Logic symbol. |

|

Fig.3 |

IEC logic symbol. |

|

|

|

|

|

|

Fig.4 |

Functional diagram. |

|

|

September 1993 |

3 |

Loading...

Loading...