Philips 74HCT4094U, 74HCT4094N, 74HCT4094DB, 74HCT4094D, 74HC4094U Datasheet

...

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

∙The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT4094

8-stage shift-and-store bus register

Product specification |

|

December 1990 |

|||||

File under Integrated Circuits, IC06 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

|

|

8-stage shift-and-store bus register |

74HC/HCT4094 |

|

|

|

|

FEATURES

·Output capability: standard

·ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT4094 are high-speed Si-gate CMOS devices and are pin compatible with the “4094” of the “4000B” series. They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT4094 are 8-stage serial shift registers having a storage latch associated with each stage for strobing data from the serial input (D) to the parallel buffered 3-state outputs (QP0 to QP7). The parallel outputs may be connected directly to common bus lines.

Data is shifted on the positive-going clock (CP) transitions.

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns

The data in each shift register stage is transferred to the storage register when the strobe input (STR) is HIGH. Data in the storage register appears at the outputs whenever the output enable input (OE) signal is HIGH.

Two serial outputs (QS1 and QS2) are available for cascading a number of “4094” devices. Data is available at QS1 on the positive-going clock edges to allow high-speed operation in cascaded systems in which the clock rise time is fast. The same serial information is available at QS2 on the next negative-going clock edge and is for cascading “4094” devices when the clock rise time is slow.

APPLICATIONS

·Serial-to-parallel data conversion

·Remote control holding register

SYMBOL |

PARAMETER |

CONDITIONS |

TYPICAL |

UNIT |

||

|

|

|||||

HC |

HCT |

|||||

|

|

|

|

|||

|

|

|

|

|

|

|

tPHL/ tPLH |

propagation delay |

CL = 15 pF; VCC = 5 V |

|

|

|

|

|

CP to QS1 |

|

15 |

19 |

ns |

|

|

CP to QS2 |

|

13 |

18 |

ns |

|

|

CP to QPn |

|

20 |

21 |

ns |

|

|

STR to QPn |

|

18 |

19 |

ns |

|

fmax |

maximum clock frequency |

|

95 |

86 |

MHz |

|

CI |

input capacitance |

|

3.5 |

3.5 |

pF |

|

CPD |

power dissipation capacitance per package |

notes 1 and 2 |

83 |

92 |

pF |

|

Notes

1. CPD is used to determine the dynamic power dissipation (PD in mW): PD = CPD ´ VCC2 ´ fi + å (CL ´ VCC2 ´ fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

å (CL ´ VCC2 ´ fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC - 1.5 V

ORDERING INFORMATION

See “74HC/HCT/HCU/HCMOS Logic Package Information”.

December 1990 |

2 |

Philips Semiconductors |

|

|

Product specification |

|

|

|

|

8-stage shift-and-store bus register |

74HC/HCT4094 |

||

|

|

|

|

PIN DESCRIPTION |

|

|

|

|

|

|

|

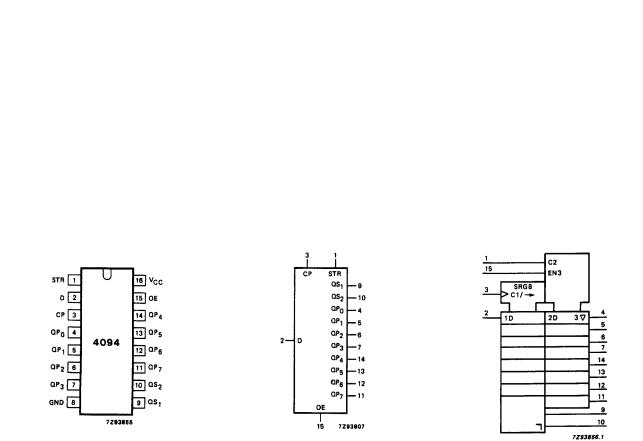

PIN NO. |

SYMBOL |

NAME AND FUNCTION |

|

|

|

|

|

1 |

STR |

strobe input |

|

2 |

D |

serial input |

|

3 |

CP |

clock input |

|

4, 5, 6, 7,14, 13, 12, 11 |

QP0 to QP7 |

parallel outputs |

|

8 |

GND |

ground (0 V) |

|

9, 10 |

QS1, QS2 |

serial outputs |

|

15 |

OE |

output enable input |

|

16 |

VCC |

positive supply voltage |

|

Fig.1 Pin configuration. |

|

Fig.2 Logic symbol. |

|

Fig.3 IEC logic symbol. |

|

|

|

|

|

December 1990 |

3 |

Loading...

Loading...