Philips 74HCT299U, 74HCT299N, 74HCT299DB, 74HCT299D, 74HC299N Datasheet

...

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

∙The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

∙The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT299

8-bit universal shift register; 3-state

Product specification |

|

December 1990 |

|||||

File under Integrated Circuits, IC06 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

|

|

8-bit universal shift register; 3-state |

74HC/HCT299 |

|

|

|

|

FEATURES

·Multiplexed inputs/outputs provide improved bit density

·Four operating modes:

–shift left

–shift right

–hold (store)

–load data

·Operates with output enable or at high-impedance OFF-state (Z)

·3-state outputs drive bus lines directly

·Can be cascaded for n-bits word length

·Output capability: bus driver (parallel I/Os), standard (serial outputs)

·ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT299 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns

The 74HC/HCT299 contain eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous shift-right, shift-left, parallel load and hold operations. The type of operation is determined by the mode select inputs (S0 and S1), as shown in the mode select table.

All flip-flop outputs have 3-state buffers to separate these outputs (I/O0 to I/O7) such, that they can serve as data inputs in the parallel load mode. The serial outputs (Q0 and Q7) are used for expansion in serial shifting of longer words.

A LOW signal on the asynchronous master reset input (MR) overrides the Sn and clock (CP) inputs and resets the flip-flops. All other state changes are initiated by the rising edge of the clock pulse. Inputs can change when the clock is either state, provided that the recommended set-up and hold times, relative to the rising edge of CP, are observed.

A HIGH signal on the 3-state output enable inputs (OE1 or

OE2) disables the 3-state buffers and the I/On outputs are set to the high-impedance OFF-state. In this condition, the shift, hold, load and reset operations can still occur. The 3-state buffers are also disabled by HIGH signals on both S0 and S1, when in preparation for a parallel load operation.

SYMBOL |

PARAMETER |

CONDITIONS |

TYPICAL |

UNIT |

||||

|

|

|||||||

HC |

HCT |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

tPHL/ tPLH |

propagation delay |

CL = 15 pF; VCC = 5 V |

|

|

|

|||

|

|

CP to Q0, Q7 |

|

20 |

19 |

ns |

||

|

|

CP to I/On |

|

20 |

19 |

ns |

||

tPHL |

|

|

|

20 |

23 |

ns |

||

|

MR |

to Q0, Q7 or I/On |

|

|||||

fmax |

maximum clock frequency |

|

50 |

46 |

MHz |

|||

CI |

input capacitance |

|

3.5 |

3.5 |

pF |

|||

CI/O |

input/output capacitance |

|

10 |

10 |

pF |

|||

CPD |

power dissipation capacitance per package |

notes 1 and 2 |

120 |

125 |

pF |

|||

Notes

1.CPD is used to determine the dynamic power dissipation (PD in mW):

PD = CPD ´ VCC2 ´ fi + å (CL ´ VCC2 ´ fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

å (CL ´ VCC2 ´ fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC - 1.5 V

ORDERING INFORMATION

See “74HC/HCT/HCU/HCMOS Logic Package Information”.

December 1990 |

2 |

Philips Semiconductors |

|

|

|

|

|

|

Product specification |

|

|

|

|

|

|

|

|

|

|

8-bit universal shift register; 3-state |

74HC/HCT299 |

|||||||

|

|

|

|

|

|

|

|

|

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

PIN NO. |

|

SYMBOL |

NAME AND FUNCTION |

|

||||

|

|

|

|

|

||||

1, 19 |

|

S0, S1 |

mode select inputs |

|

||||

2, 3 |

|

|

|

|

2 |

3-state output enable inputs (active LOW) |

|

|

|

OE |

1, |

OE |

|

||||

7, 13, 6, 14, 5, 15, 4, 16 |

|

I/O0 to I/O7 |

parallel data inputs or 3-state parallel outputs (bus driver) |

|||||

8, 17 |

|

Q0, Q7 |

serial outputs (standard output) |

|

||||

9 |

|

MR |

|

asynchronous master reset input (active LOW) |

|

|||

10 |

|

GND |

ground (0 V) |

|

||||

11 |

|

DSR |

serial data shift-right input |

|

||||

12 |

|

CP |

clock input (LOW-to-HIGH, edge-triggered) |

|

||||

18 |

|

DSL |

serial data shift-left input |

|

||||

20 |

|

VCC |

positive supply voltage |

|

||||

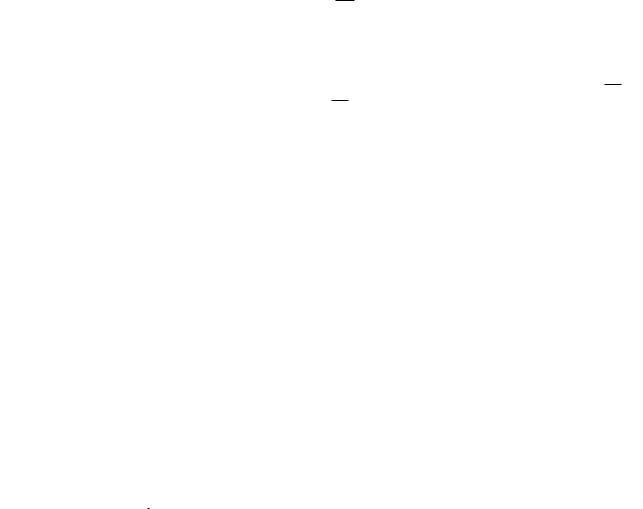

Fig.1 Pin configuration. |

|

Fig.2 Logic symbol. |

|

Fig.3 IEC logic symbol. |

|

|

|

|

|

December 1990 |

3 |

Philips Semiconductors |

Product specification |

|

|

8-bit universal shift register; 3-state |

74HC/HCT299 |

|

|

|

|

|

|

|

|

|

Fig.4 Functional diagram. |

|

|

|

|||||

MODE SELECT TABLE |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

INPUTS |

|

RESPONSE |

|

|

|

|

|

|

|

|

|

|

MR |

|

S1 |

|

S0 |

CP |

|

L |

X |

|

X |

X |

asynchronous reset; Q0−Q7 = LOW |

||

H |

H |

|

H |

− |

parallel load; I/On → Qn |

||

H |

L |

|

H |

− |

shift right; DSR → Q0, Q0 → Q1 etc. |

||

H |

H |

|

L |

− |

shift left; DSL → Q7, Q7 → Q6 etc. |

||

H |

L |

|

L |

X |

hold |

||

|

|

|

|

|

|

|

|

Notes

1.H = HIGH voltage level L = LOW voltage level

X = don’t care

− = LOW-to-HIGH CP transition

December 1990 |

4 |

Loading...

Loading...