Texas Instruments MSP430F149IPM, MSP430F133 Datasheet

|

Capture/Compare-With-Shadow Registers, |

|

2KB RAM |

|

|

– MSP430F149: |

|

|

Timer_B |

|

|

|

|

60KB+256B Flash Memory, |

|

D 16-Bit Timer With Three Capture/Compare |

|

||

|

2KB RAM |

||

|

Registers, Timer_A |

|

|

|

|

D Available in 64-Pin Quad Flat Pack (QFP) |

|

|

|

|

MSP430x13x, MSP430x14x |

|

|

|

MIXED SIGNAL MICROCONTROLLER |

|

|

|

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001 |

D |

Low Supply-Voltage Range, 1.8 V . . . 3.6 V |

D |

Serial Onboard Programming, |

D Ultralow-Power Consumption: |

|

No External Programming Voltage Needed |

|

|

– Standby Mode: 1.6 A |

|

Programmable Code Protection by Security |

|

– RAM Retention Off Mode: 0.1 A |

|

Fuse |

D |

Low Operating Current: |

D |

Family Members Include: |

|

– 2.5 A at 4 kHz, 2.2 V |

|

– MSP430F133: |

|

– 280 A at 1 MHz, 2.2 V |

|

8KB+256B Flash Memory, |

D Five Power-Saving Modes |

|

256B RAM |

|

D Wake-Up From Standby Mode in 6 s |

|

– MSP430F135: |

|

|

|

|

16KB+256B Flash Memory, |

D |

16-Bit RISC Architecture, |

|

512B RAM |

|

125-ns Instruction Cycle Time |

|

– MSP430F147: |

D 12-Bit A/D Converter With Internal |

|

32KB+256B Flash Memory, |

|

|

Reference, Sample-and-Hold and Autoscan |

|

1KB RAM |

|

Feature |

|

– MSP430F148: |

D 16-Bit Timer With Seven |

|

48KB+256B Flash Memory, |

|

|

|

||

D On-Chip Comparator

description

The Texas Instruments MSP430 series is an ultralow-power microcontroller family consisting of several devices featuring different sets of modules targeted to various applications. The microcontroller is designed to be battery operated for use in extended-time applications. The MSP430 achieves maximum code efficiency with its 16-bit RISC architecture, 16-bit CPU-integrated registers, and a constant generator. The digitally-controlled oscillator provides wake-up from low-power mode to active mode in less than 6 s. The MSP430x13x and the MSP430x14x series are microcontroller configurations with two built-in 16-bit timers, a fast 12-bit A/D converter, one or two universal serial synchronous/asynchronous communication interfaces (USART), and 48 I/O pins.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and process and transmit the data to a host system. The timers make the configurations ideal for industrial control applications such as ripple counters, digital motor control, EE-meters, hand-held meters, etc. The hardware multiplier enhances the performance and offers a broad code and hardware-compatible family solution.

|

AVAILABLE OPTIONS |

|

|

|

PACKAGED DEVICES |

TA |

|

|

|

PLASTIC 64-PIN QFP |

|

|

|

(PM) |

MSP430F133IPM

MSP430F135IPM –40° C to 85° C MSP430F147IPM MSP430F148IPM MSP430F149IPM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2001, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

1 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

pin designation, MSP430F133, MSP430F135

PM PACKAGE (TOP VIEW)

|

|

|

AV |

DV |

AV |

P6.2/A2 P6.1/A1 P6.0/A0 RST/NMI TCK TMS TDI TDO/TDI XT2IN |

|

XT2OUT P5.7/TBoutH P5.6/ACLK |

|

P5.5/SMCLK |

|

|

|||||||||||||||||||||||||

|

|

|

CC |

SS |

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DVCC |

|

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 |

|

|

|

|

P5.4/MCLK |

||||||||||||||||||||||||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

||||||

P6.3/A3 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

P5.3 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.4/A4 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

P5.2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.5/A5 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

P5.1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.6/A6 |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

P5.0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.7/A7 |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

P4.7/TBCLK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VREF+ |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

P4.6 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

XIN |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

P4.5 |

||||

XOUT/TCLK |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

P4.4 |

||||

VeREF+ |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

P4.3 |

|||||

VREF–/VeREF– |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

P4.2/TB2 |

|||||

P1.0/TACLK |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

P4.1/TB1 |

|||||

P1.1/TA0 |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

P4.0/TB0 |

|||||

P1.2/TA1 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

P3.7 |

|||||

P1.3/TA2 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

P3.6 |

|||||

P1.4/SMCLK |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

P3.5/URXD0 |

|||||

|

|

1718 19 |

20 21 22 23 24 25 26 27 28 |

29 30 31 |

32 |

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.5/TA0 |

P1.6/TA1 |

P1.7/TA2 |

P2.0/ACLK P2.1/TAINCLK P2.2/CAOUT/TA0 P2.3/CA0/TA1 P2.4/CA1/TA2 P2.5/Rosc P2.6/ADC12CLK P2.7/TA0 P3.0/STE0 |

|

P3.1/SIMO0 P3.2/SOMI0 P3.3/UCLK0 |

|

P3.4/UTXD0 |

|

|

|||||||||||||||||||||||||

2 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

pin designation, MSP430F147, MSP430F148, MSP430F149

PM PACKAGE (TOP VIEW)

|

|

|

AV |

DV |

AV |

|

P6.2/A2 P6.1/A1 P6.0/A0 RST/NMI TCK TMS TDI TDO/TDI XT2IN |

|

XT2OUT P5.7/TBoutH P5.6/ACLK |

|

P5.5/SMCLK |

|

|

|||||||||||||||||||||||||

|

|

|

CC |

SS |

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DVCC |

|

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 |

|

|

|

|

P5.4/MCLK |

|||||||||||||||||||||||||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

||||||

P6.3/A3 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

P5.3/UCLK1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.4/A4 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

P5.2/SOMI1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.5/A5 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

P5.1/SIMO1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.6/A6 |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

P5.0/STE1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P6.7/A7 |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

P4.7/TBCLK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VREF+ |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

P4.6/TB6 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

XIN |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

P4.5/TB5 |

||||

XOUT/TCLK |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

P4.4/TB4 |

||||

VeREF+ |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

P4.3/TB3 |

|||||

VREF–/VeREF– |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

P4.2/TB2 |

|||||

P1.0/TACLK |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

P4.1/TB1 |

|||||

P1.1/TA0 |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

P4.0/TB0 |

|||||

P1.2/TA1 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

P3.7/URXD1 |

|||||

P1.3/TA2 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

P3.6/UTXD1 |

|||||

P1.4/SMCLK |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

P3.5/URXD0 |

|||||

|

|

1718 19 |

20 21 22 23 24 25 26 27 28 |

29 30 31 |

32 |

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.5/TA0 |

P1.6/TA1 |

P1.7/TA2 |

|

P2.0/ACLK P2.1/TAINCLK P2.2/CAOUT/TA0 P2.3/CA0/TA1 P2.4/CA1/TA2 P2.5/Rosc P2.6/ADC12CLK P2.7/TA0 P3.0/STE0 |

|

P3.1/SIMO0 P3.2/SOMI0 P3.3/UCLK0 |

|

P3.4/UTXD0 |

|

|

|||||||||||||||||||||||||

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

3 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

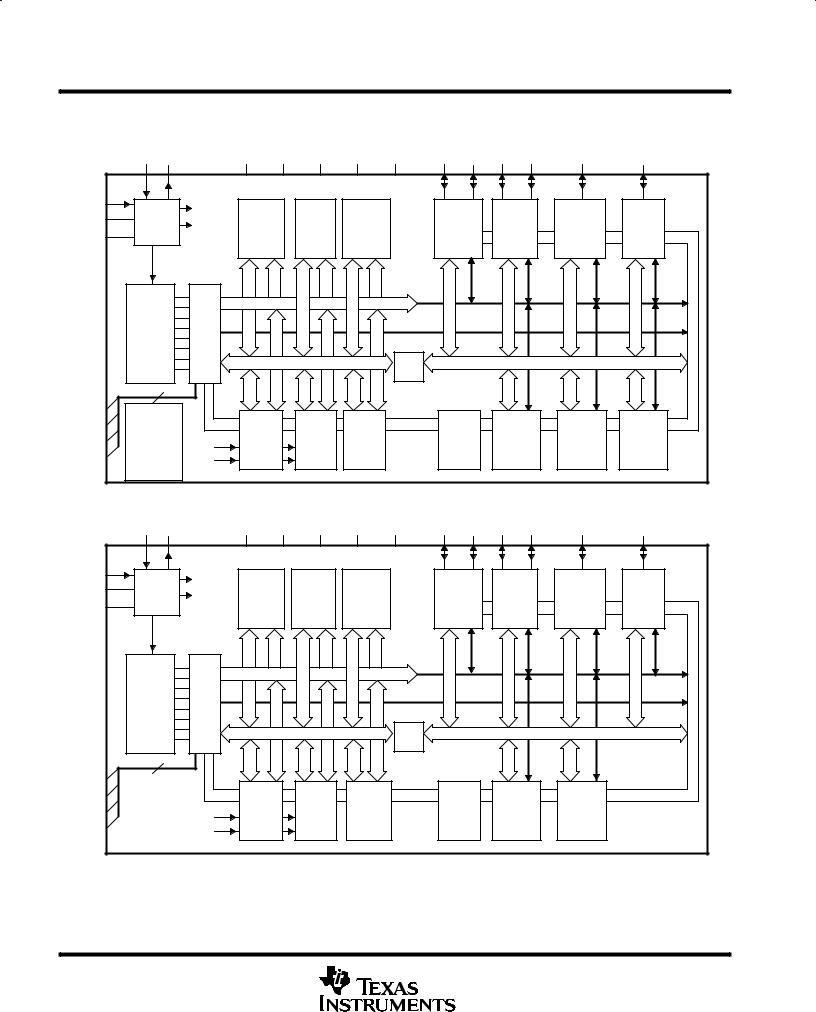

functional block diagrams

MSP430x14x |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

XIN XOUT/TCLK |

DVCC |

DVSS |

AVCC |

AVSS |

RST/NMI |

P1 |

P2 |

P3 |

P4 |

P5 |

P6 |

|||

Rosc |

Oscillator |

ACLK |

60 kB Flash |

2 kB RAM |

12 Bit ADC |

I/O Port 1/2 |

I/O Port 3/4 |

I/O Port 5 |

I/O Port 6 |

||||||

XT2IN |

|||||||||||||||

System |

SMCLK |

48 kB Flash |

2 kB RAM |

8 Channels |

16 I/Os, With |

16 I/Os |

8 I/Os |

8 I/Os |

|||||||

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||

XT2OUT |

Clock |

|

32 kB Flash |

|

<10 µ s Conv. |

Interrupt |

|

|

|

|

|||||

|

|

|

1 kB RAM |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

Capability |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

MCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Test |

MAB, 16 Bit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

JTAG |

|

|

|

|

|

MAB, 4 Bit |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

CPU |

|

|

|

|

|

|

|

MCB |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Incl. 16 Reg. |

Emulation Module |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

MDB, 16 Bit |

|

|

|

Bus |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

Conv |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

MDB, 8 Bit |

|

|

|

|

||

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS |

Multipy |

|

|

|

|

|

|

|

|

|

|

|

|

||

TCK |

MPY, MPYS |

|

Watchdog |

Timer_B7 |

Timer_A3 |

|

Power |

|

|

USART0 |

USART1 |

||||

|

Timer |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Comparator |

|

|

||||||

|

MAC,MACS |

|

|

|

|

|

|

on |

UART Mode |

UART Mode |

|||||

TDI |

8× |

8 Bit |

ACLK |

|

|

7 CC-Reg. |

3 CC-Reg. |

|

Reset |

|

A |

||||

TDO/TDI |

8× |

16 Bit |

SMCLK |

15 / 16 Bit |

Shadow |

|

|

|

|

|

|

SPI Mode |

SPI Mode |

||

16× 8 Bit |

|

|

Reg. |

|

|

|

|

|

|

|

|

||||

|

16× |

16 Bit |

|

|

|

|

|

|

|

|

|

|

|

|

|

MSP430x13x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XIN XOUT/TCLK |

DVCC |

DVSS |

AVCC |

AVSS |

RST/NMI |

P1 |

P2 |

P3 |

P4 |

P5 |

P6 |

|

Rosc |

Oscillator |

ACLK |

|

|

|

12 Bit ADC |

I/O Port 1/2 |

I/O Port 3/4 |

I/O Port 5 |

I/O Port 6 |

|||

|

|

|

|

||||||||||

XT2IN |

System |

SMCLK |

16 kB Flash |

512B RAM |

8 Channels |

16 I/Os, With |

16 I/Os |

8 I/Os |

8 I/Os |

||||

|

|

|

|||||||||||

|

Clock |

|

8 kB Flash |

256B RAM |

Interrupt |

|

|

|

|

||||

XT2OUT |

|

<10 µ s Conv. |

|

|

|

|

|||||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

Capability |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

MCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Test |

MAB, 16 Bit |

|

|

|

|

|

|

|

|

|

|

|

|

JTAG |

|

|

|

|

|

MAB, 4 Bit |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

CPU |

|

|

|

|

|

|

|

MCB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Incl. 16 Reg. |

Emulation Module |

|

|

|

|

|

|

|

|

|

|

|

|

|

MDB, 16 Bit |

|

|

|

Bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

Conv |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MDB, 8 Bit |

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

TMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

TCK |

|

|

Watchdog |

Timer_B3 |

Timer_A3 |

|

Power |

|

|

USART0 |

|

||

|

|

Timer |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

on |

Comparator |

|

|

||

TDI |

|

|

|

|

|

|

|

|

UART Mode |

|

|||

|

ACLK |

|

|

3 CC-Reg. |

3 CC-Reg. |

|

Reset |

|

|||||

|

|

|

|

|

A |

|

|||||||

TDO/TDI |

|

|

15 / 16 Bit |

Shadow |

|

|

|

|

|

SPI Mode |

|

||

|

SMCLK |

|

|

|

|

|

|

|

|||||

|

|

|

Reg. |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

|

|

|

|

MSP430x13x, MSP430x14x |

|

|

|

|

|

MIXED SIGNAL MICROCONTROLLER |

|

|

|

|

|

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001 |

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|

|

|

|

|

|

|

|

TERMINAL |

|

I/O |

DESCRIPTION |

|

|

NAME |

NO. |

|

||

|

|

|

|

||

|

|

|

|

|

|

|

AVCC |

64 |

|

Analog supply voltage, positive terminal. Supplies only the analog portion of the analog-to-digital converter. |

|

|

AVSS |

62 |

|

Analog supply voltage, negative terminal. Supplies only the analog portion of the analog-to-digital converter. |

|

|

DVCC |

1 |

|

Digital supply voltage, positive terminal. Supplies all digital parts. |

|

|

DVSS |

63 |

|

Digital supply voltage, negative terminal. Supplies all digital parts. |

|

|

P1.0/TACLK |

12 |

I/O |

General digital I/O pin/Timer_A, clock signal TACLK input |

|

|

|

|

|

|

|

|

P1.1/TA0 |

13 |

I/O |

General digital I/O pin/Timer_A, capture: CCI0A input, compare: Out0 output |

|

|

|

|

|

|

|

|

P1.2/TA1 |

14 |

I/O |

General digital I/O pin/Timer_A, capture: CCI1A input, compare: Out1 output |

|

|

|

|

|

|

|

|

P1.3/TA2 |

15 |

I/O |

General digital I/O pin/Timer_A, capture: CCI2A input, compare: Out2 output |

|

|

|

|

|

|

|

|

P1.4/SMCLK |

16 |

I/O |

General digital I/O pin/SMCLK signal output |

|

|

|

|

|

|

|

|

P1.5/TA0 |

17 |

I/O |

General digital I/O pin/Timer_A, compare: Out0 output |

|

|

|

|

|

|

|

|

P1.6/TA1 |

18 |

I/O |

General digital I/O pin/Timer_A, compare: Out1 output |

|

|

|

|

|

|

|

|

P1.7/TA2 |

19 |

I/O |

General digital I/O pin/Timer_A, compare: Out2 output/ |

|

|

|

|

|

|

|

|

P2.0/ACLK |

20 |

I/O |

General digital I/O pin/ACLK output |

|

|

|

|

|

|

|

|

P2.1/TAINCLK |

21 |

I/O |

General digital I/O pin/Timer_A, clock signal at INCLK |

|

|

|

|

|

|

|

|

P2.2/CAOUT/TA0 |

22 |

I/O |

General digital I/O pin/Timer_A, capture: CCI0B input/Comparator_A output |

|

|

|

|

|

|

|

|

P2.3/CA0/TA1 |

23 |

I/O |

General digital I/O pin/Timer_A, compare: Out1 output/Comparator_A input |

|

|

|

|

|

|

|

|

P2.4/CA1/TA2 |

24 |

I/O |

General digital I/O pin/Timer_A, compare: Out2 output/Comparator_A input |

|

|

|

|

|

|

|

|

P2.5/Rosc |

25 |

I/O |

General-purpose digital I/O pin, input for external resistor defining the DCO nominal frequency |

|

|

|

|

|

|

|

|

P2.6/ADC12CLK |

26 |

I/O |

General digital I/O pin, conversion clock – 12-bit ADC |

|

|

|

|

|

|

|

|

P2.7/TA0 |

27 |

I/O |

General digital I/O pin/Timer_A, compare: Out0 output |

|

|

|

|

|

|

|

|

P3.0/STE0 |

28 |

I/O |

General digital I/O, slave transmit enable – USART0/SPI mode |

|

|

|

|

|

|

|

|

P3.1/SIMO0 |

29 |

I/O |

General digital I/O, slave in/master out of USART0/SPI mode |

|

|

|

|

|

|

|

|

P3.2/SOMI0 |

30 |

I/O |

General digital I/O, slave out/master in of USART0/SPI mode |

|

|

|

|

|

|

|

|

P3.3/UCLK0 |

31 |

I/O |

General digital I/O, external clock input – USART0/UART or SPI mode, clock output – USART0/SPI mode |

|

|

|

|

|

|

|

|

P3.4/UTXD0 |

32 |

I/O |

General digital I/O, transmit data out – USART0/UART mode |

|

|

|

|

|

|

|

|

P3.5/URXD0 |

33 |

I/O |

General digital I/O, receive data in – USART0/UART mode |

|

|

|

|

|

|

|

|

P3.6/UTXD1† |

34 |

I/O |

General digital I/O, transmit data out – USART1/UART mode |

|

|

P3.7/URXD1† |

35 |

I/O |

General digital I/O, receive data in – USART1/UART mode |

|

|

P4.0/TB0 |

36 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR0 |

|

|

|

|

|

|

|

|

P4.1/TB1 |

37 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR1 |

|

|

|

|

|

|

|

|

P4.2/TB2 |

38 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR2 |

|

|

|

|

|

|

|

|

P4.3/TB3† |

39 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR3 |

|

|

P4.4/TB4† |

40 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR4 |

|

|

P4.5/TB5† |

41 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR5 |

|

|

P4.6/TB6† |

42 |

I/O |

General-purpose digital I/O, capture I/P or PWM output port – Timer_B7 CCR6 |

|

|

P4.7/TBCLK |

43 |

I/O |

General-purpose digital I/O, input clock TBCLK – Timer_B7 |

|

|

|

|

|

|

|

|

P5.0/STE1† |

44 |

I/O |

General-purpose digital I/O, slave transmit enable – USART1/SPI mode |

|

|

P5.1/SIMO1† |

45 |

I/O |

General-purpose digital I/O slave in/master out of USART1/SPI mode |

|

|

P5.2/SOMI1† |

46 |

I/O |

General-purpose digital I/O, slave out/master in of USART1/SPI mode |

|

|

P5.3/UCLK1† |

47 |

I/O |

General-purpose digital I/O, external clock input – USART1/UART or SPI mode, clock output – USART1/SPI |

|

|

|

|

|

mode |

|

|

|

|

|

|

|

|

P5.4/MCLK |

48 |

I/O |

General-purpose digital I/O, main system clock MCLK output |

|

|

|

|

|

|

|

|

P5.5/SMCLK |

49 |

I/O |

General-purpose digital I/O, submain system clock SMCLK output |

|

|

† 14x devices only |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

5 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

|

|

|

|

|

Terminal Functions (Continued) |

|

|

|

|

|

|

|

|

TERMINAL |

|

I/O |

DESCRIPTION |

|

|

NAME |

NO. |

||

|

|

|

|

||

|

|

|

|

|

|

|

P5.6/ACLK |

50 |

I/O |

General-purpose digital I/O, auxiliary clock ACLK output |

|

|

|

|

|

|

|

|

P5.7/TboutH |

51 |

I/O |

General-purpose digital I/O, switch all PWM digital output ports to high impedance – Timer_B7 TB0 to TB6 |

|

|

|

|

|

|

|

|

P6.0/A0 |

59 |

I/O |

General digital I/O, analog input a0 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.1/A1 |

60 |

I/O |

General digital I/O, analog input a1 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.2/A2 |

61 |

I/O |

General digital I/O, analog input a2 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.3/A3 |

2 |

I/O |

General digital I/O, analog input a3 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.4/A4 |

3 |

I/O |

General digital I/O, analog input a4 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.5/A5 |

4 |

I/O |

General digital I/O, analog input a5 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.6/A6 |

5 |

I/O |

General digital I/O, analog input a6 – 12-bit ADC |

|

|

|

|

|

|

|

|

P6.7/A7 |

6 |

I/O |

General digital I/O, analog input a7 – 12-bit ADC |

|

|

|

|

|

|

|

|

|

|

58 |

I |

Reset input, nonmaskable interrupt input port, or bootstrap loader start (in Flash devices). |

|

RST/NMI |

||||

|

|

|

|

|

|

|

TCK |

57 |

I |

Test clock. TCK is the clock input port for device programming test and bootstrap loader start (in Flash |

|

|

|

|

|

|

devices). |

|

|

|

|

|

|

|

TDI |

55 |

I |

Test data input. TDI is used as a data input port. The device protection fuse is connected to TDI. |

|

|

|

|

|

|

|

|

TDO/TDI |

54 |

I/O |

Test data output port. TDO/TDI data output or programming data input terminal |

|

|

|

|

|

|

|

|

TMS |

56 |

I |

Test mode select. TMS is used as an input port for device programming and test. |

|

|

|

|

|

|

|

|

VeREF+ |

10 |

I/P |

Input for an external reference voltage to the ADC |

|

|

VREF+ |

7 |

O |

Output of positive terminal of the reference voltage in the ADC |

|

|

VREF–/VeREF– |

11 |

O |

Negative terminal for the ADC’s reference voltage for both sources, the internal reference voltage, or an |

|

|

|

|

|

|

external applied reference voltage |

|

|

|

|

|

|

|

XIN |

8 |

I |

Input port for crystal oscillator XT1. Standard or watch crystals can be connected. |

|

|

|

|

|

|

|

|

XOUT/TCLK |

9 |

I/O |

Output terminal of crystal oscillator XT1 or test clock input |

|

|

|

|

|

|

|

|

XT2IN |

53 |

I |

Input port for crystal oscillator XT2. Only standard crystals can be connected. |

|

|

|

|

|

|

|

|

XT2OUT |

52 |

O |

Output terminal of crystal oscillator XT2 |

|

short-form description

processing unit

The processing unit is based on a consistent and orthogonal CPU and instruction set. This design structure results in a RISC-like architecture, highly transparent to the application development and notable for its ease of programming. All operations other than program-flow instructions are consequently performed as register operations in conjunction with seven addressing modes for source and four modes for destination operand.

CPU

The CPU has sixteen registers that provide reduced instruction execution time. This reduces the register-to-register operation execution time to one cycle of the processor frequency.

Four of the registers are reserved for special use as program counter, stack pointer, status register, and constant generator. The remaining registers are available as general-purpose registers.

Peripherals are connected to the CPU using a data address and control bus, and can be easily handled with all memory manipulation instructions.

Program Counter |

PC/R0 |

|

|

|

|

Stack Pointer |

SP/R1 |

|

SR/CG1/R2 |

|

|

Status Register |

|

|

|

|

|

Constant Generator |

CG2/R3 |

|

R4 |

|

|

General-Purpose Register |

|

|

R5 |

|

|

General-Purpose Register |

|

|

|

|

|

General-Purpose Register |

R14 |

|

R15 |

|

|

General-Purpose Register |

|

|

|

6 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

short-form description (continued)

instruction set

The instruction set for this register-to-register architecture constitutes a powerful and easy-to-use assembler language. The instruction set consists of 51 instructions with three formats and seven address modes. Table 1 provides a summary and example of the three types of instruction formats; the address modes are listed in Table 2.

Table 1. Instruction Word Formats

Dual operands, source-destination |

e.g. ADD |

R4,R5 |

R4 + R5 –––> R5 |

|

|

|

|

Single operands, destination only |

e.g. CALL |

R8 |

PC ––>(TOS), R8––> PC |

|

|

|

|

Relative jump, un/conditional |

e.g. JNE |

|

Jump-on-equal bit = 0 |

Each instruction operating on word and byte data is identified by the suffix B.

Examples: |

WORD INSTRUCTIONS |

BYTE INSTRUCTIONS |

||

|

MOV |

EDE, TONI |

MOV.B |

EDE,TONI |

|

ADD |

#235h,&MEM |

ADD.B |

#35h,&MEM |

|

PUSH |

R5 |

PUSH.B |

R5 |

|

SWPB |

R5 |

— |

|

Table 2. Address Mode Descriptions

ADDRESS MODE |

|

S |

D |

SYNTAX |

EXAMPLE |

OPERATION |

|

|

|

|

|

|

|

Register |

|

n |

n |

MOV Rs,Rd |

MOV R10,R11 |

R10 ––> R11 |

|

|

|

|

|

|

|

Indexed |

|

n |

n |

MOV X(Rn),Y(Rm) |

MOV 2(R5),6(R6) |

M(2+R5)––> M(6+R6) |

|

|

|

|

|

|

|

Symbolic (PC relative) |

|

n |

n |

MOV EDE,TONI |

|

M(EDE) ––> M(TONI) |

|

|

|

|

|

|

|

Absolute |

|

n |

n |

MOV &MEM,&TCDAT |

|

M(MEM) ––> M(TCDAT) |

|

|

|

|

|

|

|

Indirect |

|

n |

|

MOV @Rn,Y(Rm) |

MOV @R10,Tab(R6) |

M(R10) ––> M(Tab+R6) |

|

|

|

|

|

|

|

Indirect |

|

n |

|

MOV @Rn+,Rm |

MOV @R10+,R11 |

M(R10) ––> R11 |

autoincrement |

|

|

R10 + 2––> R10 |

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

Immediate |

|

n |

|

MOV #X,TONI |

MOV #45,TONI |

#45 ––> M(TONI) |

|

|

|

|

|

|

|

NOTE: S = source |

D = destination |

|

|

|||

Computed branches (BR) and subroutine call (CALL) instructions use the same address modes as other instructions. These address modes provide indirect addressing, which is ideally suited for computed branches and calls. The full use of this programming capability results in a program structure which is different from structures used with conventional 8- and 16-bit controllers. For example, numerous routines can be easily designed to deal with pointers and stacks instead of using flag-type programs for flow control.

operating modes and interrupts

The MSP430 operating modes provide advanced support of the requirements for ultralow-power and ultralowenergy consumption. This goal is achieved by intelligent management during the different operating modes of modules and CPU states and is fully supported during interrupt event handling. An interrupt event awakes the system from each of the various operating modes and returns, using the RETI instruction, to the mode that was selected before the interrupt event occurred. The different requirements on CPU and modules— driven by system cost and current consumption objectives— require the use of different clock signals:

DAuxiliary clock ACLK, sourced by LFXT1CLK (crystal frequency) and used by the peripheral modules

DMain system clock MCLK, used by the CPU and system

DSubsystem clock SMCLK, used by the peripheral modules

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

7 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

operating modes and interrupts (continued)

|

DIVA |

|

|

2 |

|

LFXT1CLK |

/1, /2, /4, /8 |

ACLK |

|

||

|

Auxiliary Clock |

|

|

|

|

OscOff |

XTS |

|

ACLKGEN |

|

XIN |

|

|

|

|

|

|

LFXT1 Oscillator |

|

|

|

|

|

|

High Frequency |

|

|

|

|

|

XT1 Oscillator, XTS = 1 |

SELM |

DIVM CPUOff |

|

|

|

|

|

||

XOUT |

Low Power |

2 |

2 |

|

|

|

|

|

|

||

|

LF Oscillator, XTS = 0 |

3 |

|

MCLK |

|

|

|

0.1 |

|

/1, /2, /4, /8, Off |

|

|

|

XT2CLK |

|

Main System |

|

|

|

2 |

|

||

|

|

|

MCLKGEN |

Clock |

|

|

|

|

|

||

|

XT2Off |

|

|

|

|

|

|

|

|

|

|

XT2IN |

|

|

|

|

|

XT2OUT |

XT2 Oscillator |

|

|

|

|

|

|

|

|

|

|

VCC |

VCC |

Rsel |

|

|

|

|

|

|

SCG0 |

DCO |

MOD |

|

SELS |

DIVS |

SCG1 |

|

|

|

|

|

3 |

5 |

DCOCLK |

|

2 |

|

|

|

|

0 |

DC |

Digital Controlled Oscillator DCO |

0 |

/1, /2, /4, /8, Off |

SMCLK |

|||

|

|

|

|

+ |

|

|||||

|

|

|

Generator |

|

|

|

SUB-System |

|||

|

|

|

Modulator MOD |

|

1 |

|

|

|||

P2.5/Rosc |

1 |

|

|

|

|

|

Clock |

|||

|

DCGEN |

|

|

DCOMOD |

|

SMCLKGEN |

||||

|

|

|

|

|

|

|

||||

|

|

|

DCOR |

|

|

|

|

|

|

|

The DCO generator is connected to pin P2.5/Rosc if DCOR control bit is set.

The port pin P2.5/Rosc is selected if DCOR control bit is reset (initial state).

P2.5

Any of these clock sources— LFXT1CLK, XT2CLK, or DCOCLK— can be used to drive the MSP430 system.

LFXT1CLK is defined by connecting a low-power, low-frequency crystal to the oscillator, by connecting a high-frequency crystal to the oscillator, or by applying an external clock source. The high-frequency crystal oscillator is used if control bit XTS is set. The crystal oscillator may be switched off if LFXT1CLK is not required for the current operating mode.

XT2CLK is defined by connecting a high-frequency crystal to the oscillator or by applying an external clock source. Crystal oscillator XT2 may be switched off using the XT2Off control bit if not required by the current operating mode.

When DCOCLK is active, its frequency is selected or adjusted by software. DCOCLK is inactive or stopped when it is not being used by the CPU or peripheral modules. The dc generator can be stopped when SCG0 is reset and DCOCLK is not required. The dc generator determines the basic DCO frequency, and can be set by one external resistor or adjusted in eight steps by selection of integrated resistors.

NOTE:

The system clock generator always starts with DCOCLK selected as MCLK (CPU clock) to ensure proper start of program execution. The software determines the final system clock through control bit manipulation.

The system clock MCLK is also selected by hardware to be the DCOCLK (DCO and DCGEN are on) if the crystal oscillator (XT1 or XT2) fails while being selected as MCLK. Without this forced clock mode the NMI, requested by the oscillator fault flag, can not be handled and control may be lost. Without forced-clock mode the processor could not execute any code until the failed oscillator restarts.

8 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

low-power consumption capabilities

The various operating modes are handled by software by controlling the operation of the internal clock system. This clock system provides a large combination of hardware and software capabilities to run the application while maintaining the lowest power consumption and optimizing system costs. This is accomplished by:

DUse of the internal clock (DCO) generator without any external components

DSelection of an external crystal or ceramic resonator for lowest frequency and cost

DSelection and activation of the proper clock signals (LFXT1CLK, XT2Off, and/or DCOCLK) and clock predivider function. Control bit XT2Off is embedded in control register BCSCTL1.

DApplication of an external clock source

The control bits that most influence the operation of the clock system and support fast turnon from low power operating modes are located in the status register SR. Four bits control the CPU and the system clock generator: SCG1, SCG0, OscOff, and CPUOff.

15 |

9 |

8 |

7 |

|

|

|

|

|

|

|

|

0 |

|

|

|

Reserved For Future |

|

V |

SCG1 |

SCG0 |

OscOff |

CPUOff |

GIE |

N |

Z |

C |

|||

|

Enhancements |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-0

CPUOff, SCG1, SCG0, and OscOff are the most important bits in low-power control when the basic function of the system clock generator is established. They are pushed to the stack whenever an interrupt is accepted and saved for returning to the operation before an interrupt request. They can be manipulated via indirect access to the data on the stack during execution of an interrupt handler so that program execution can resume in another power operating mode after return-from-interrupt.

CPUOff: |

Clock signal MCLK, used with the CPU, is active when the CPUOff bit is reset or stopped when |

|

set. |

SCG1: |

Clock signal SMCLK, used with peripherals, is enabled when the SCG1 bit is reset or stopped |

|

when set. |

OscOff: |

Crystal oscillator LFXT1 is active when the OscOff bit is reset. The LFXT1 oscillator can be inac- |

|

tive only when the OscOff bit is set and it is not used for MCLK. The setup time to start a crystal |

|

oscillation requires special consideration when the off option is used. Mask-programmable de- |

|

vices can disable this feature and the oscillator can never be switched off by software. |

SCG0: |

The dc generator is active when the SCG0 bit is reset. The DCO can be inactive only if the SCG0 |

|

bit is set and the DCOCLK signal is not used as MCLK or SMCLK. The dc current consumed |

|

by the dc generator defines the basic frequency of the DCOCLK. |

|

When the current is switched off (SCG0=1) the start of the DCOCLK is slightly delayed. This |

|

delay is in the microsecond range. |

DCOCLK: |

Clock signal DCOCLK is stopped if not used as MCLK or SMCLK. There are two situations when |

|

the SCG0 bit can not switch the DCOCLK signal off: |

The DCOCLK frequency is used as MCLK (CPUOff=0 and SELM.1=0), or the DCOCLK frequency is used as SMCLK (SCG1=0 and SELS=0).

If DCOCLK is required for operation, the SCG0 bit can not switch the dc generator off.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

9 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

interrupt vector addresses

The interrupt vectors and the power-up starting address are located in the address range 0FFFFh – 0FFE0h. The vector contains the 16-bit address of the appropriate interrupt-handler instruction sequence.

INTERRUPT SOURCE |

INTERRUPT FLAG |

SYSTEM INTERRUPT |

WORD ADDRESS |

PRIORITY |

|

|

|

|

|

|

|

Power-up |

WDTIFG |

Reset |

0FFFEh |

15, highest |

|

External Reset |

KEYV |

|

|

|

|

Watchdog |

(see Note 1) |

|

|

|

|

Flash memory |

|

|

|

|

|

|

|

|

|

|

|

NMI |

NMIIFG (see Notes 1 & 4) |

(Non)maskable |

|

|

|

Oscillator Fault |

OFIFG (see Notes 1 & 4) |

(Non)maskable |

0FFFCh |

14 |

|

Flash memory access violation |

ACCVIFG (see Notes 1 & 4) |

(Non)maskable |

|

|

|

|

|

|

|

|

|

Timer_B7 (see Note 5) |

BCCIFG0 (see Note 2) |

Maskable |

0FFFAh |

13 |

|

|

|

|

|

|

|

Timer_B7 (see Note 5) |

BCCIFG1 to BCCIFG6 |

Maskable |

0FFF8h |

12 |

|

TBIFG (see Notes 1 & 2) |

|||||

|

|

|

|

||

|

|

|

|

|

|

Comparator_A |

CAIFG |

Maskable |

0FFF6h |

11 |

|

|

|

|

|

|

|

Watchdog timer |

WDTIFG |

Maskable |

0FFF4h |

10 |

|

|

|

|

|

|

|

USART0 receive |

URXIFG0 |

Maskable |

0FFF2h |

9 |

|

|

|

|

|

|

|

USART0 transmit |

UTXIFG0 |

Maskable |

0FFF0h |

8 |

|

|

|

|

|

|

|

ADC |

ADCIFG (see Notes 1 & 2) |

Maskable |

0FFEEh |

7 |

|

|

|

|

|

|

|

Timer_A3 |

CCIFG0 (see Note 2) |

Maskable |

0FFECh |

6 |

|

|

|

|

|

|

|

|

CCIFG1, |

|

|

|

|

Timer_A3 |

CCIFG2, |

Maskable |

0FFEAh |

5 |

|

|

TAIFG (see Notes 1 & 2) |

|

|

|

|

|

|

|

|

|

|

|

P1IFG.0 (see Notes 1 & 2) |

|

|

|

|

I/O port P1 (eight flags) |

To |

Maskable |

0FFE8h |

4 |

|

|

P1IFG.7 (see Notes 1 & 2) |

|

|

|

|

|

|

|

|

|

|

USART1 receive |

URXIFG1 |

Maskable |

0FFE6h |

3 |

|

|

|

|

|

|

|

USART1 transmit |

UTXIFG1 |

|

0FFE4h |

2 |

|

|

|

|

|

|

|

|

P2IFG.0 (see Notes 1 & 2) |

|

|

|

|

I/O port P2 (eight flags) |

To |

Maskable |

0FFE2h |

1 |

|

|

P2IFG.7 (see Notes 1 & 2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

0FFE0h |

0, lowest |

NOTES: 1. Multiple source flags

2.Interrupt flags are located in the module.

3.Nonmaskable: neither the individual nor the general interrupt-enable bit will disable an interrupt event.

4.(Non)maskable: the individual interrupt-enable bit can disable an interrupt event, but the general-interrupt enable can not disable it.

5.Timer_B7 in MSP430x14x family has 7 CCRs; Timer_B3 in MSP430x13x family has 3 CCRs; in Timer_B3 there are only interrupt flags CCIFG0, 1, and 2, and the interrupt-enable bits CCIE0, 1, and 2 integrated.

special function registers

Most interrupt and module-enable bits are collected in the lowest address space. Special-function register bits not allocated to a functional purpose are not physically present in the device. This arrangement provides simple software access.

10 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

interrupt enable 1 and 2

Address |

7 |

|

6 |

5 |

4 |

3 |

|

2 |

1 |

0 |

|

|

0h |

|

UTXIE0 |

URXIE0 |

ACCVIE |

NMIIE |

|

|

|

OFIE |

WDTIE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-0 |

|

rw-0 |

rw-0 |

rw-0 |

|

|

|

rw-0 |

rw-0 |

||

WDTIE: |

|

Watchdog-timer-interrupt enable signal |

|

|

|

|

|

|

||||

OFIE: |

|

Oscillator-fault-interrupt enable signal |

|

|

|

|

|

|

||||

NMIIE: |

|

Nonmaskable-interrupt enable signal |

|

|

|

|

|

|

||||

ACCVIE: |

(Non)maskable-interrupt enable signal, access violation if FLASH memory/module is busy |

|||||||||||

URXIE0: |

USART0, UART, and SPI receive-interrupt enable signal |

|

|

|

|

|||||||

UTXIE0: |

USART0, UART, and SPI transmit-interrupt enable signal |

|

|

|

|

|||||||

Address |

7 |

|

6 |

5 |

4 |

3 |

|

2 |

1 |

0 |

|

|

01h |

|

|

|

|

UTXIE1 |

URXIE1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-0 |

rw-0 |

|

|

|

|

|

|

URXIE1: |

USART1, UART, and SPI receive-interrupt enable signal |

|

|

|

|

|||||||

UTXIE1: |

USART1, UART, and SPI transmit-interrupt enable signal |

|

|

|

|

|||||||

interrupt flag register 1 and 2

Address |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

|

2 |

1 |

0 |

|

02h |

UTXIFG0 |

URXIFG0 |

|

NMIIFG |

|

|

|

|

|

OFIFG |

WDTIFG |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-1 |

|

rw-0 |

|

rw-0 |

|

|

|

|

rw-1 |

rw-0 |

|||

WDTIFG: |

Set on overflow or security key violation or |

|

|

|

|

|

|

|||||||

|

|

reset on VCC power-on or reset condition at |

RST/NMI |

|

|

|

||||||||

OFIFG: |

Flag set on oscillator fault |

|

|

|

|

|

|

|

|

|||||

NMIIFG: |

Set via |

|

|

|

|

|

|

|

|

|

|

|||

RST/NMI pin |

|

|

|

|

|

|

|

|

||||||

URXIFG0: |

USART0, UART, and SPI receive flag |

|

|

|

|

|

|

|||||||

UTXIFG0: |

USART0, UART, and SPI transmit flag |

|

|

|

|

|

|

|||||||

Address |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

|

2 |

1 |

0 |

|

03h |

|

|

|

|

|

UTXIFG1 |

URXIFG1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-1 rw-0

URXIFG1: USART1, UART, and SPI receive flag

UTXIFG1: USART1, UART, and SPI transmit flag

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

11 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

module enable registers 1 and 2

Address |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

04h |

UTXE0 |

URXE0 |

|

|

|

|

|

|

|

USPIE0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-0 |

rw-0 |

|

|

|

|

|

|

URXE0: |

|

USART0, UART receive enable |

|

|

|

|

|

|

|

|

|

||||||||||

UTXE0: |

|

USART0, UART transmit enable |

|

|

|

|

|

|

|

|

|

||||||||||

USPIE0: |

|

USART0, SPI (synchronous peripheral interface) transmit and receive enable |

|

|

|||||||||||||||||

Address |

7 |

|

|

|

6 |

5 |

4 |

|

3 |

|

2 |

1 |

|

|

0 |

|

|||||

05h |

|

|

|

|

|

|

|

UTXE1 |

|

URXE1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USPIE1 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw-0 |

|

rw-0 |

|

|

|

|

|

|

|

|

|

|

URXE1: |

|

USART1, UART receive enable |

|

|

|

|

|

|

|

|

|

||||||||||

UTXE1: |

|

USART1, UART transmit enable |

|

|

|

|

|

|

|

|

|

||||||||||

USPIE1: |

|

USART1, SPI (synchronous peripheral interface) transmit and receive enable |

|

|

|||||||||||||||||

Legend: rw: |

|

|

|

Bit Can Be Read and Written |

|

|

|

|

|

|

|

|

|

||||||||

rw-0: |

|

|

|

Bit Can Be Read and Written. It Is Reset by PUC. |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

SFR Bit Not Present in Device |

|

|

|

|

|

|

|

|

|

||||||

memory organization |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

MSP430F133 |

|

MSP430F135 |

MSP430F147 |

|

MSP430F148 |

|

MSP430F149 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Memory |

|

|

|

Size |

|

|

8kB |

|

16kB |

32kB |

|

|

48kB |

|

60kB |

||||||

Main: interrupt vector |

|

|

Flash |

0FFFFh – 0FFE0h |

0FFFFh – 0FFE0h |

0FFFFh – 0FFE0h |

0FFFFh – 0FFE0h |

|

0FFFFh – 0FFE0h |

||||||||||||

Main: code memory |

|

|

|

Flash |

0FFFFh – 0E000h |

0FFFFh – 0C000h |

0FFFFh – 08000h |

0FFFFh – 04000h |

|

0FFFFh – 01100h |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Information memory |

|

|

|

Size |

|

256 Byte |

|

256 Byte |

256 Byte |

|

|

256 Byte |

|

256 Byte |

|||||||

|

|

|

|

|

|

Flash |

010FFh – 01000h |

010FFh – 01000h |

010FFh – 01000h |

010FFh – 01000h |

|

010FFh – 01000h |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Boot memory |

|

|

|

Size |

|

|

1kB |

|

1kB |

1kB |

|

|

1kB |

|

1kB |

||||||

|

|

|

|

|

|

ROM |

|

0FFFh – 0C00h |

|

0FFFh – 0C00h |

0FFFh – 0C00h |

0FFFh – 0C00h |

|

0FFFh – 0C00h |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

RAM |

|

|

|

Size |

|

256 Byte |

|

512 Byte |

1kB |

|

|

2kB |

|

2kB |

|||||||

|

|

|

|

|

|

|

|

02FFh – 0200h |

|

03FFh – 0200h |

05FFh – 0200h |

09FFh – 0200h |

|

09FFh – 0200h |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Peripherals |

|

|

|

16-bit |

|

01FFh – 0100h |

|

01FFh – 0100h |

01FFh – 0100h |

01FFh – 0100h |

|

01FFh – 0100h |

|||||||||

|

|

|

|

|

|

8-bit |

|

0FFh – 010h |

|

0FFh – 010h |

0FFh – 010h |

|

0FFh – 010h |

|

0FFh – 010h |

||||||

|

|

|

|

8-bit SFR |

|

0Fh – 00h |

|

0Fh – 00h |

0Fh – 00h |

|

|

0Fh – 00h |

|

0Fh – 00h |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

boot ROM containing bootstrap loader

The intention of the bootstrap loader is to download data into the flash memory module. Various write, read, and erase operations are needed for a proper download environment. The bootstrap loader is only available on F devices.

functions of the bootstrap loader:

Definition of read: |

Apply and transmit data of peripheral registers or memory to pin P1.1 (BSLTX) |

write: |

Read data from pin P2.2 (BSLRX) and write them into flash memory |

unprotected functions

Mass erase, erase of the main memory (segment 0 to segment n) and information memory (segment A and segment B)

Access to the MSP430 via the bootstrap loader is protected. It must be enabled before any protected function can be performed. The 256 bits in 0FFE0h to 0FFFFh provide the access key.

12 |

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

boot ROM containing bootstrap loader (continued)

protected functions

All protected functions can be executed only if the access is enabled.

DWrite/program byte into flash memory; parameters passed are start address and number of bytes (the segment-write feature of the flash memory is not supported and not useful with the UART protocol).

DSegment erase of segment 0 to segment n in main memory, and segment erase of segments A and B in the information memory.

DRead all data in main memory and information memory.

DRead and write to all byte peripheral modules and RAM.

DModify PC and start program execution immediately.

NOTE:

Unauthorized readout of code and data is prevented by the user’s definition of the data in the interrupt memory locations.

features of the bootstrap loader are:

DUART communication protocol, fixed to 9600 baud

DPort pin P1.1 for transmit, P2.2 for receive

DTI standard serial protocol definition

DImplemented in flash memory version only

DProgram execution starts with the user vector at 0FFFEh or with the bootstrap loader (start vector is at address 0C00h)

hardware resources used for serial input/output:

DPins P1.1 and P2.2 for serial data transmission

DTCK and RST/NMI to start program execution at the reset or bootstrap loader vector

DBasic clock module: Rsel=5, DCO=4, MOD=0, DCOCLK for MCLK and SMCLK, clock divider for MCLK

and SMCLK at default: dividing by 1

DTimer_A: Timer_A operates in continuous mode with MCLK source selected, input divider set to 1,

|

using CCR0, and polling of CCIFG0. |

D WDT: |

Watchdog Timer is halted |

DInterrupt: GIE=0, NMIIE=0, OFIE=0, ACCVIE=0

DMemory allocation and stack pointer:

If the stack pointer points to RAM addresses above 0220h, 6 bytes of the stack are allocated, plus RAM addresses 0200h to 0219h. Otherwise the stack pointer is set to 0220h and allocates RAM from 0200h to 021Fh.

NOTE:

When writing RAM data via the bootstrap loader, make sure that the stack is outside the range of the data to be written.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 |

13 |

MSP430x13x, MSP430x14x

MIXED SIGNAL MICROCONTROLLER

SLAS272C – JULY 2000 – REVISED FEBRUARY 2001

boot ROM containing bootstrap loader (continued)

Program execution begins with the user’s reset vector at FFFEh (standard method) if TCK is held high while RST/NMI goes from low to high:

RST/NMI

TCK

User Program Starts