OKI MSM5117405C-70TS-L, MSM5117405C-70SJ, MSM5117405C-60TS-K, MSM5117405C-50TS-K, MSM5117405C-70TS-K Datasheet

...

E2G0109-18-42 |

Preliminary |

|

¡ Semiconductor |

||

This version: Apr. 1998 |

||

MSM5117405C |

||

Semiconductor |

MSM5117405C

4,194,304-Word ´ 4-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO

DESCRIPTION

The MSM5117405C is a 4,194,304-word ´4-bit dynamic RAM fabricated in Oki's silicon-gate CMOS technology. The MSM5117405C achieves high integration, high-speed operation, and low-power consumption because Oki manufactures the device in a quadruple-layer polysilicon/double-layer metal CMOS process. The MSM5117405C is available in a 26/24-pin plastic SOJ or 26/24-pin plastic TSOP.

FEATURES

•4,194,304-word ´ 4-bit configuration

•Single 5 V power supply, ±10% tolerance

• Input : TTL compatible, low input capacitance

•Output : TTL compatible, 3-state

•Refresh : 2048 cycles/32 ms

•Fast page mode with EDO, read modify write capability

•CAS before RAS refresh, hidden refresh, RAS-only refresh capability

•Multi-bit test mode capability

•Package options:

26/24-pin 300 mil plastic SOJ (SOJ26/24-P-300-1.27) (Product : MSM5117405C-xxSJ) 26/24-pin 300 mil plastic TSOP (TSOPII26/24-P-300-1.27-K) (Product : MSM5117405C-xxTS-K)

(TSOPII26/24-P-300-1.27-L) (Product : MSM5117405C-xxTS-L) xx indicates speed rank.

PRODUCT FAMILY

Family |

Access Time (Max.) |

Cycle Time |

Power Dissipation |

|||||

|

|

|

|

(Min.) |

|

|

||

tRAC |

tAA |

tCAC |

tOEA |

Operating (Max.) |

Standby (Max.) |

|||

|

||||||||

|

|

|||||||

MSM5117405C-50 |

50 ns |

25 ns |

13 ns |

13 ns |

90 ns |

660 mW |

|

|

MSM5117405C-60 |

60 ns |

30 ns |

15 ns |

15 ns |

110 ns |

605 mW |

5.5 mW |

|

|

|

|

|

|

|

|

|

|

MSM5117405C-70 |

70 ns |

35 ns |

20 ns |

20 ns |

130 ns |

550 mW |

|

|

|

|

|

|

|

|

|

|

|

1/18

¡ Semiconductor |

MSM5117405C |

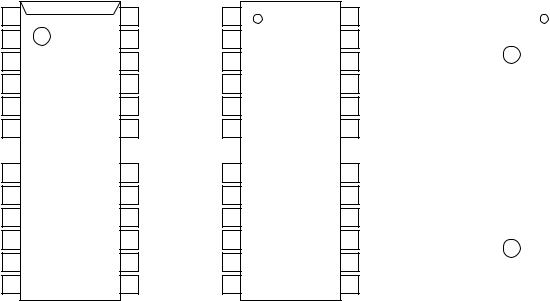

PIN CONFIGURATION (TOP VIEW) |

|

|

|||||

VCC |

1 |

26 |

VSS |

VCC |

1 |

26 |

VSS |

DQ1 |

2 |

25 |

DQ4 |

DQ1 |

2 |

25 |

DQ4 |

DQ2 |

3 |

24 |

DQ3 |

DQ2 |

3 |

24 |

DQ3 |

WE 4 |

23 |

CAS |

WE 4 |

23 |

CAS |

||

RAS |

5 |

22 |

OE |

RAS |

5 |

22 |

OE |

NC |

6 |

21 |

A9 |

NC |

6 |

21 |

A9 |

A10 |

8 |

19 |

A8 |

A10 |

8 |

19 |

A8 |

A0 |

9 |

18 |

A7 |

A0 |

9 |

18 |

A7 |

A1 |

10 |

17 |

A6 |

A1 |

10 |

17 |

A6 |

A2 |

11 |

16 |

A5 |

A2 |

11 |

16 |

A5 |

A3 |

12 |

15 |

A4 |

A3 |

12 |

15 |

A4 |

VCC 13 |

14 |

VSS |

VCC 13 |

14 |

VSS |

||

|

26/24-Pin Plastic SOJ |

|

|

26/24-Pin Plastic TSOP |

|

||

|

|

|

|

|

|

(K Type) |

|

|

|

|

|

|

VSS |

26 |

|

1 |

VCC |

|

|

|

|

|

DQ4 |

25 |

|

2 |

DQ1 |

DQ3 |

|

|

|

DQ2 |

24 |

|

3 |

||

CAS |

|

|

|

WE |

23 |

|

4 |

||

OE |

|

|

|

RAS |

22 |

|

5 |

||

A9 |

|

|

|

NC |

21 |

|

6 |

||

A8 |

|

|

|

A10 |

19 |

|

8 |

||

A7 |

|

|

|

A0 |

18 |

|

9 |

||

A6 |

|

|

|

A1 |

17 |

|

10 |

||

A5 |

|

|

|

A2 |

16 |

|

11 |

||

A4 |

|

|

|

A3 |

15 |

|

12 |

||

|

|

|

|

|

VSS |

14 |

|

13 |

VCC |

|

|

|

|

|

26/24-Pin Plastic TSOP

(L Type)

Pin Name |

Function |

|

|

A0 - A10 |

Address Input |

|

|

RAS |

Row Address Strobe |

|

|

CAS |

Column Address Strobe |

|

|

DQ1 - DQ4 |

Data Input/Data Output |

|

|

OE |

Output Enable |

|

|

WE |

Write Enable |

|

|

VCC |

Power Supply (5 V) |

VSS |

Ground (0 V) |

NC |

No Connection |

|

|

Note : The same power supply voltage must be provided to every VCC pin, and the same GND voltage level must be provided to every VSS pin.

2/18

¡ Semiconductor |

MSM5117405C |

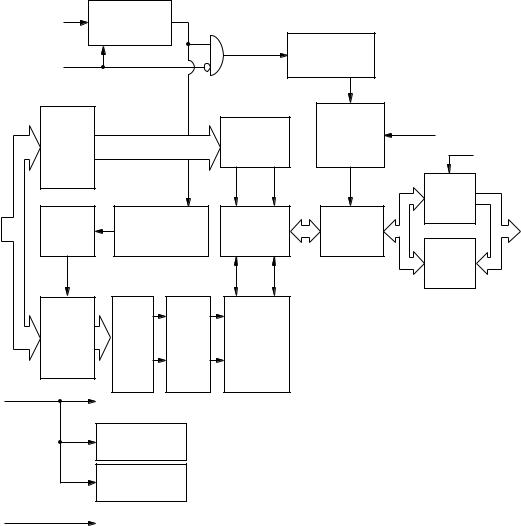

BLOCK DIAGRAM

RAS |

|

Timing |

|

|

|

|

|

|

|

Generator |

|

|

|

|

|

|

|||

|

|

|

|

|

Timing |

|

|

||

|

|

|

|

|

|

|

|

|

|

CAS |

|

|

|

|

Generator |

|

|

||

|

Column |

|

|

|

|

|

Write |

|

|

11 |

|

|

11 |

Column |

|

Clock |

WE |

|

|

Address |

|

|

Decoders |

|

Generator |

|

OE |

||

|

Buffers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

Output |

4 |

|

|

|

|

|

|

|

Buffers |

||

|

Internal |

|

Refresh |

|

|

I/O |

|

||

A0 - A10 |

|

Sense |

|

|

|

||||

Address |

|

4 |

|

4 DQ1 - DQ4 |

|||||

|

Control Clock |

Amplifiers |

4 |

|

|||||

|

Counter |

|

|

Selector |

Input |

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

4 |

4 |

|

|

|

|

|

|

|

|

Buffers |

||

|

|

|

|

|

|

|

|

|

|

|

Row |

|

Row |

Word |

Memory |

|

|

|

|

11 |

Address |

11 |

|

|

|

|

|||

De- |

|

|

|

|

|||||

Drivers |

Cells |

|

|

|

|

||||

|

Buffers |

|

|

|

|

|

|||

|

|

coders |

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

VCC

On Chip

VBB Generator

On Chip

IVCC Generator

VSS

3/18

¡ Semiconductor MSM5117405C

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

|

Parameter |

Symbol |

|

|

Rating |

|

Unit |

|

|

|

|

|

|

|

|

|

|

|

Voltage on Any Pin Relative to VSS |

VIN, VOUT |

|

–0.5 to VCC + 0.5 |

|

V |

||

|

Voltage on VCC Supply Relative to VSS |

VCC |

|

|

–0.5 to 7 |

|

V |

|

|

Short Circuit Output Current |

IOS |

|

50 |

|

|

mA |

|

|

Power Dissipation |

PD* |

|

1 |

|

|

W |

|

|

Operating Temperature |

Topr |

|

|

0 to 70 |

|

°C |

|

|

Storage Temperature |

Tstg |

|

|

–55 to 150 |

|

°C |

|

|

|

*: Ta = 25°C |

|

|

|

|

|

|

Recommended Operating Conditions |

|

|

|

|

(Ta = 0°C to 70°C) |

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Parameter |

Symbol |

Min. |

|

Typ. |

|

Max. |

Unit |

|

|

|

|

|

|

|

|

|

|

Power Supply Voltage |

VCC |

4.5 |

|

5.0 |

|

5.5 |

V |

|

VSS |

0 |

|

0 |

|

0 |

V |

|

|

|

|

|

|||||

|

Input High Voltage |

VIH |

2.4 |

|

— |

|

VCC + 0.5*1 |

V |

|

Input Low Voltage |

VIL |

–0.5*2 |

|

— |

|

0.8 |

V |

Notes : *1. TheinputvoltageisVCC +2.0Vwhenthepulsewidthislessthan20ns(thepulsewidth is with respect to the point at which VCC is applied).

*2. TheinputvoltageisVSS –2.0Vwhenthepulsewidthislessthan20ns(thepulsewidth is with respect to the point at which VSS is applied).

Capacitance

(VCC = 5 V ±10%, Ta = 25°C, f = 1 MHz)

Parameter |

Symbol |

Typ. |

Max. |

Unit |

|

|

|

|

|

Input Capacitance (A0 - A10) |

CIN1 |

— |

5 |

pF |

Input Capacitance (RAS, CAS, WE, OE) |

CIN2 |

— |

7 |

pF |

Output Capacitance (DQ1 - DQ4) |

CI/O |

— |

7 |

pF |

4/18

¡ Semiconductor |

|

|

|

|

|

|

MSM5117405C |

||||

DC Characteristics |

|

|

|

|

|

(VCC = 5 V ±10%, Ta = 0°C to 70°C) |

|||||

|

|

|

|

|

|

||||||

|

|

|

MSM5117405 |

MSM5117405 |

MSM5117405 |

|

|

||||

Parameter |

Symbol |

Condition |

C-50 |

C-60 |

C-70 |

Unit |

Note |

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Min. |

Max. |

Min. |

Max. |

Min. |

Max. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output High Voltage |

VOH |

IOH = –5.0 mA |

2.4 |

VCC |

2.4 |

VCC |

2.4 |

VCC |

V |

|

|

Output Low Voltage |

VOL |

IOL = 4.2 mA |

0 |

0.4 |

0 |

0.4 |

0 |

0.4 |

V |

|

|

|

|

0 V £ VI £ 6.5 V; |

|

|

|

|

|

|

|

|

|

Input Leakage Current |

ILI |

All other pins not |

–10 |

10 |

–10 |

10 |

–10 |

10 |

mA |

|

|

|

|

under test = 0 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Leakage Current |

ILO |

DQ disable |

–10 |

10 |

–10 |

10 |

–10 |

10 |

mA |

|

|

0 V £ VO £ VCC |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||

Average Power |

|

RAS, CAS cycling, |

|

|

|

|

|

|

|

|

|

Supply Current |

ICC1 |

— |

120 |

— |

110 |

— |

100 |

mA |

1, 2 |

||

tRC = Min. |

|||||||||||

(Operating) |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply |

|

RAS, CAS = VIH |

— |

2 |

— |

2 |

— |

2 |

|

|

|

ICC2 |

RAS, CAS |

|

|

|

|

|

|

mA |

1 |

||

Current (Standby) |

— |

1 |

— |

1 |

— |

1 |

|||||

|

³ VCC –0.2 V |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||

Average Power |

|

RAS cycling, |

|

|

|

|

|

|

|

|

|

Supply Current |

ICC3 |

CAS = VIH, |

— |

120 |

— |

110 |

— |

100 |

mA |

1, 2 |

|

(RAS-only Refresh) |

|

tRC = Min. |

|

|

|

|

|

|

|

|

|

Power Supply |

|

RAS = VIH, |

|

|

|

|

|

|

|

|

|

ICC5 |

CAS = VIL, |

— |

5 |

— |

5 |

— |

5 |

mA |

1 |

||

Current (Standby) |

|||||||||||

|

DQ = enable |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

Average Power |

|

RAS cycling, |

|

|

|

|

|

|

|

|

|

Supply Current |

ICC6 |

— |

120 |

— |

110 |

— |

100 |

mA |

1, 2 |

||

CAS before RAS |

|||||||||||

(CAS before RAS Refresh) |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Average Power |

|

RAS = VIL, |

|

|

|

|

|

|

|

|

|

Supply Current |

ICC7 |

CAS cycling, |

— |

100 |

— |

90 |

— |

80 |

mA |

1, 3 |

|

(Fast Page Mode) |

|

tHPC = Min. |

|

|

|

|

|

|

|

|

|

Notes : 1. ICC Max. is specified as ICC for output open condition.

2.The address can be changed once or less while RAS = VIL.

3.The address can be changed once or less while CAS = VIH.

5/18

¡ Semiconductor |

|

|

|

|

|

|

|

MSM5117405C |

||

AC Characteristics (1/2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

(VCC = 5 V ±10%, Ta = 0°C to 70°C) Note 1, 2, 3, 12, 13 |

|||||||

|

|

MSM5117405 |

MSM5117405 |

MSM5117405 |

|

|

||||

Parameter |

Symbol |

C-50 |

C-60 |

C-70 |

Unit |

Note |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Min. |

Max. |

Min. |

Max. |

Min. |

Max. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Random Read or Write Cycle Time |

tRC |

84 |

|

— |

104 |

— |

124 |

— |

ns |

|

Read Modify Write Cycle Time |

tRWC |

110 |

|

— |

135 |

— |

160 |

— |

ns |

|

Fast Page Mode Cycle Time |

tHPC |

20 |

|

— |

25 |

— |

30 |

— |

ns |

|

Fast Page Mode Read Modify Write |

tHPRWC |

58 |

|

— |

68 |

— |

78 |

— |

ns |

|

Cycle Time |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Access Time from RAS |

tRAC |

— |

|

50 |

— |

60 |

— |

70 |

ns |

4, 5, 6 |

Access Time from CAS |

tCAC |

— |

|

13 |

— |

15 |

— |

20 |

ns |

4, 5 |

Access Time from Column Address |

tAA |

— |

|

25 |

— |

30 |

— |

35 |

ns |

4, 6 |

Access Time from CAS Precharge |

tCPA |

— |

|

30 |

— |

35 |

— |

40 |

ns |

4 |

Access Time from OE |

tOEA |

— |

|

13 |

— |

15 |

— |

20 |

ns |

4 |

Output Low Impedance Time from CAS |

tCLZ |

0 |

|

— |

0 |

— |

0 |

— |

ns |

4 |

Data Output Hold After CAS Low |

tDOH |

5 |

|

— |

5 |

— |

5 |

— |

ns |

|

CAS to Data Output Buffer Turn-off Delay Time |

tCEZ |

0 |

|

13 |

0 |

15 |

0 |

20 |

ns |

7, 8 |

RAS to Data Output Buffer Turn-off Delay Time |

tREZ |

0 |

|

13 |

0 |

15 |

0 |

20 |

ns |

7, 8 |

OE to Data Output Buffer Turn-off Delay Time |

tOEZ |

0 |

|

13 |

0 |

15 |

0 |

20 |

ns |

7 |

WE to Data Output Buffer Turn-off Delay Time |

tWEZ |

0 |

|

13 |

0 |

15 |

0 |

20 |

ns |

7 |

Transition Time |

tT |

1 |

|

50 |

1 |

50 |

1 |

50 |

ns |

3 |

Refresh Period |

tREF |

— |

|

32 |

— |

32 |

— |

32 |

ms |

|

RAS Precharge Time |

tRP |

30 |

|

— |

40 |

— |

50 |

— |

ns |

|

RAS Pulse Width |

tRAS |

50 |

|

10,000 |

60 |

10,000 |

70 |

10,000 |

ns |

|

RAS Pulse Width (Fast Page Mode with EDO) |

tRASP |

50 |

|

100,000 |

60 |

100,000 |

70 |

100,000 |

ns |

|

RAS Hold Time |

tRSH |

7 |

|

— |

10 |

— |

13 |

— |

ns |

|

RAS Hold Time referenced to OE |

tROH |

7 |

|

— |

10 |

— |

13 |

— |

ns |

|

CAS Precharge Time (Fast Page Mode with EDO) |

tCP |

7 |

|

— |

10 |

— |

10 |

— |

ns |

|

CAS Pulse Width |

tCAS |

7 |

|

10,000 |

10 |

10,000 |

13 |

10,000 |

ns |

|

CAS Hold Time |

tCSH |

35 |

|

— |

40 |

— |

45 |

— |

ns |

|

CAS to RAS Precharge Time |

tCRP |

5 |

|

— |

5 |

— |

5 |

— |

ns |

|

RAS Hold Time from CAS Precharge |

tRHCP |

30 |

|

— |

35 |

— |

40 |

— |

ns |

|

OE Hold Time from CAS (DQ Disable) |

tCHO |

5 |

|

— |

5 |

— |

5 |

— |

ns |

|

RAS to CAS Delay Time |

tRCD |

11 |

|

37 |

14 |

45 |

14 |

50 |

ns |

5 |

RAS to Column Address Delay Time |

tRAD |

9 |

|

25 |

12 |

30 |

12 |

35 |

ns |

6 |

Row Address Set-up Time |

tASR |

0 |

|

— |

0 |

— |

0 |

— |

ns |

|

Row Address Hold Time |

tRAH |

7 |

|

— |

10 |

— |

13 |

— |

ns |

|

Column Address Set-up Time |

tASC |

0 |

|

— |

0 |

— |

0 |

— |

ns |

|

Column Address Hold Time |

tCAH |

7 |

|

— |

10 |

— |

13 |

— |

ns |

|

Column Address to RAS Lead Time |

tRAL |

25 |

|

— |

30 |

— |

35 |

— |

ns |

|

6/18

Loading...

Loading...