Fairchild Semiconductor DM74AS286N, DM74AS286MX, DM74AS286M Datasheet

October 1986

Revised April 2000

DM74AS286

9-Bit Parity Generator/Checker with Bus-Driver Parity I/O Port

General Description

These universal, 9-bit parity generators/checkers utilize advanced Schottky high performance circuitry and feature odd/even outputs to facilitate operation of either odd or even parity applications. The word length capability is easily expanded by cascading.

The DM74AS286 can be used to upgrade the performance of most systems utilizing the DM74AS280 parity generator/ checker. Although the DM74AS286 is implemented without expander inputs, the corresponding function is provided by the availability of an input pin XMIT. XMIT is a control line which makes parity error output active and parity an input port when HIGH; when LOW, parity error output is inactive and parity becomes an output port. In addition, parity I/O control circuitry contains a feature to keep the I/O port in the 3-STATE during power UP or DOWN to prevent bus glitches.

Features

■PNP inputs to reduce bus loading

■Generates either odd or even parity for nine data lines

■Inputs are buffered to lower the drive requirements

■Can be used to upgrade existing systems using MSI parity circuits

■Cascadable for n-bits

■Switching specifications at 50 pF

■Switching specifications guaranteed over full temperature and VCC range

■A parity I/O portable to drive bus

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74AS286M |

M14A |

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |

|

|

|

DM74AS286N |

N14A |

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

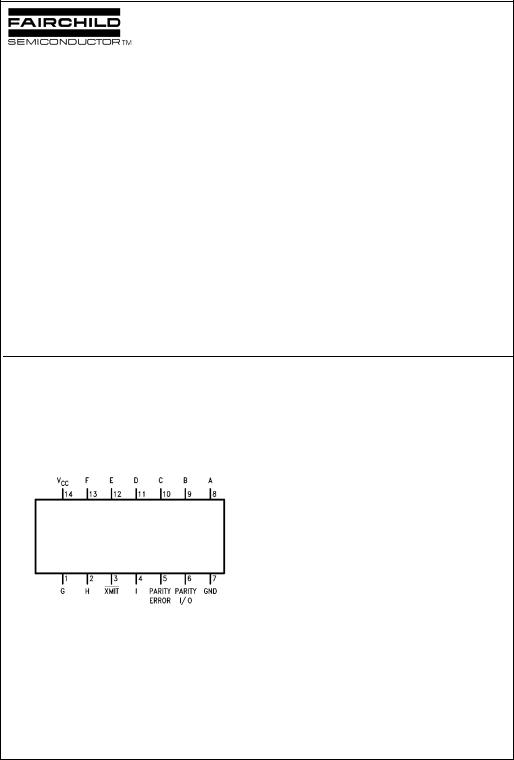

Connection Diagram |

Function Table |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Number of Inputs |

Parity I/O |

|

|

|

Parity |

Mode |

|

|

|

|

|

|

|

|

Error |

|

|

(A thru I) |

|

|

XMIT |

of |

|||

|

that are HIGH |

|

|

|

|

|

|

Operation |

|

Input |

Output |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

0, 2, 4, 6, 8 |

N/A |

H |

|

L |

H |

Parity |

|

|

|

|

|

|

|

|

|

|

|

1, 3, 5, 7, 9 |

N/A |

L |

|

L |

H |

Generator |

|

|

|

|

|

|

|

|

|

|

|

0, 2, 4, 6, 8 |

H |

N/A |

|

H |

H |

Parity |

|

|

|

|

|

|

|

|

Checker |

|

|

0, 2, 4, 6, 8 |

L |

N/A |

|

H |

L |

||

|

|

|

|

|

|

|

|

|

|

1, 3, 5, 7, 9 |

H |

N/A |

|

H |

L |

Parity |

|

|

|

|

|

|

|

|

Checker |

|

|

1, 3, 5, 7, 9 |

L |

N/A |

|

H |

H |

||

|

|

|

|

|

|

|

|

|

|

L = LOW Logic Level |

|

|

|

|

|

|

|

|

H = HIGH Logic Level |

|

|

|

|

|

|

|

|

N/A = Not Applicable |

|

|

|

|

|

|

|

Port I/O Parity Driver-Bus with Generator/Checker Parity Bit-9 DM74AS286

© 2000 Fairchild Semiconductor Corporation |

DS006305 |

www.fairchildsemi.com |

DM74AS286

Absolute Maximum Ratings(Note 1)

Supply Voltage |

7V |

Input Voltage |

7V |

Operating Free Air Temperature Range |

0° C to + 70° C |

Storage Temperature Range |

− 65° C to + 150° C |

Typical θ JA |

|

N Package |

77.0° C/W |

M Package |

108.0° C/W |

Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The “Recommended Operating Conditions” table will define the conditions for actual device operation.

Recommended Operating Conditions

Symbol |

Parameter |

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

VCC |

Supply Voltage |

|

4.5 |

5 |

5.5 |

V |

VIH |

HIGH Level Input Voltage |

|

2 |

|

|

V |

VIL |

LOW Level Input Voltage |

|

|

|

0.8 |

V |

IOH |

HIGH Level Output Current |

Parity I/O |

|

|

− 15 |

mA |

|

|

Parity Error |

|

|

− 2 |

mA |

|

|

|

|

|

|

|

IOL |

LOW Level Output Current |

Parity I/O |

|

|

48 |

mA |

|

|

Parity Error |

|

|

20 |

mA |

|

|

|

|

|

|

|

TA |

Operating Free-Air Temperature |

|

0 |

|

70 |

° C |

Electrical Characteristics

over recommended free-air temperature range. All typical values are measured at VCC = 5V, TA = |

25° C. |

|

|

|

|

||||||||

Symbol |

Parameter |

|

|

|

Conditions |

|

Min |

|

Typ |

Max |

Units |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIK |

Input Clamp Voltage |

|

VCC = |

4.5V, IIN = |

− 18 mA |

|

|

|

|

|

|

− 1.2 |

V |

VOH |

HIGH Level |

IOH = |

Max, VCC = |

4.5V |

|

|

|

2.4 |

|

3.2 |

|

V |

|

|

Output Voltage |

VCC = |

4.5V to 5.5V, IOH = |

− 2 mA |

|

VCC − |

2 |

|

|

V |

|||

VOL |

LOW Level Output Voltage |

VCC = |

4.5V, IOL = |

Max |

|

|

|

|

|

0.35 |

0.5 |

V |

|

II |

Input Current at Maximum |

VCC = |

5.5V, VIH = |

7V |

|

|

|

|

|

|

0.1 |

mA |

|

|

Input Voltage |

(VI = 5.5V for Parity I/O) |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||

IIH |

HIGH Level Input Current |

VCC = |

5.5V |

|

|

Others |

|

|

|

|

20 |

µ A |

|

|

|

VIH = |

2.7V (Note 2) |

|

Parity I/O |

|

|

|

|

50 |

|||

|

|

|

|

|

|

|

|

||||||

IIL |

LOW Level Input Current |

VCC = |

5.5V, VIL = |

0.4V (Note 2) |

|

|

|

|

− 0.5 |

mA |

|||

IO |

Output Drive Current |

VCC = |

5.5V, VOUT = 2.25V |

|

− 30 |

|

|

− 112 |

mA |

||||

ICC |

Supply Current |

|

VCC = |

5.5V, Transmit Mode |

|

|

|

|

43 |

mA |

|||

|

|

XMIT = LOW |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Receive Mode |

|

|

|

|

|

|

|

50 |

mA |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

XMIT = HIGH |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

Note 2: For I/O ports, the parameters IIH and IIL include the OFF-state current, IOZH and IOZL. |

|

|

|

|

|

|

|||||||

www.fairchildsemi.com |

2 |

Switching Characteristics

over recommended supply and temperature range

Symbol |

Parameter |

From |

To |

Min |

Max |

Units |

|||

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay Time |

Any Data Input |

Parity I/O |

3 |

15 |

ns |

|||

|

from LOW-to-HIGH Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPHL |

Propagation Delay Time |

Any Data Input |

Parity I/O |

3 |

14 |

ns |

|||

|

from HIGH-to-LOW Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay Time |

Any Data Input |

Parity Error |

3 |

16.5 |

ns |

|||

|

from LOW-to-HIGH Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPHL |

Propagation Delay Time |

Any Data Input |

Parity Error |

3 |

16.5 |

ns |

|||

|

from HIGH-to-LOW Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay Time |

Parity I/O |

Parity Error |

3 |

9 |

ns |

|||

|

from LOW-to-HIGH Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPHL |

Propagation Delay Time |

Parity I/O |

Parity Error |

3 |

9 |

ns |

|||

|

from HIGH-to-LOW Level Output |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

tPZL |

Output Enable Time to LOW Level |

|

|

|

|

Parity I/O |

3 |

16 |

ns |

|

|

XMIT |

|

||||||

tPLZ |

Output Disable Time from LOW Level |

|

|

|

|

Parity I/O |

3 |

10 |

ns |

|

XMIT |

|

|||||||

tPZH |

Output Disable Time from HIGH Level |

|

|

|

|

Parity I/O |

3 |

13 |

ns |

|

XMIT |

|

|||||||

tPHZ |

Output Enable Time to HIGH Level |

|

|

|

|

Parity I/O |

3 |

11.5 |

ns |

|

XMIT |

|

|||||||

Typical Applications

Number of |

|

Parity |

Inputs that |

|

Result |

are Logic “1” |

|

Output |

|

|

|

0, 2, 4, 6, 8, 10 |

Even |

L |

|

|

|

1, 3, 5, 7, 9 |

Odd |

H |

|

|

|

FIGURE 1. Dedicated 10-Bit Parity Sensing Configuration

DM74AS286

3 |

www.fairchildsemi.com |

Loading...

Loading...