Fairchild Semiconductor DM74AS257SJX, DM74AS257N, DM74AS257MX, DM74AS257M Datasheet

September 1986

Revised March 2000

DM74AS257 • DM74AS258

3-STATE Quad 1 of 2 Line Data Selector/Multiplexers

General Description

These data selectors/multiplexers contain inverters and drivers to supply full on-chip data selection to the four 3- STATE outputs that can interface directly with data lines of bus-organized systems. A 4-bit word selected from one of two sources is routed to the four outputs. The DM74AS257 presents true data whereas the DM74AS258 presents inverted data to minimize propagation delay time.

This 3-STATE output feature means that n-bit (paralleled) data selectors with up to 300 sources can be implemented for data buses. It also permits the use of standard TTL registers for data retention throughout the system.

Features

■Switching specifications at 50 pF

■Switching specifications guaranteed over full temperature and VCC range

■Advanced oxide-isolated, ion-implanted Schottky TTL process

■Functionally and pin for pin compatible with Schottky, low power Schottky, and advanced low power Schottky TTL counterpart

■Improved AC performance over Schottky, low power Schottky, and advanced low power Schottky counterparts

■3-STATE buffer-type output drive bus lines directly

■Expand any data input point

■Multiplex dual data buses

■General four functions of two variables (one variable is common)

■Source programmable counters

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74AS257M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

DM74AS257N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

DM74AS258M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

DM74AS258N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram |

Function Table |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INPUTS |

|

|

OUTPUT Y |

||

|

|

|

|

|

|

|

|

||

|

OUTPUT |

SELECT |

|

A |

B |

AS257 |

AS258 |

||

|

CONTROL |

|

|||||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

H |

X |

|

X |

X |

Z |

Z |

|

|

|

L |

L |

|

L |

X |

L |

H |

|

|

|

L |

L |

|

H |

X |

H |

L |

|

|

|

L |

H |

|

X |

L |

L |

H |

|

|

|

L |

H |

|

X |

H |

H |

L |

|

|

|

|

|

|

|

|

|

||

|

H = HIGH Level |

|

|

|

|

|

|

||

|

L = LOW Level |

|

|

|

|

|

|

||

|

X = Don't Care |

|

|

|

|

|

|

||

|

Z = High Impedance (OFF) |

|

|

|

|

||||

Selector/Multiplexers Data Line 2 of 1 Quad STATE-3 DM74AS258 • DM74AS257

© 2000 Fairchild Semiconductor Corporation |

DS006107 |

www.fairchildsemi.com |

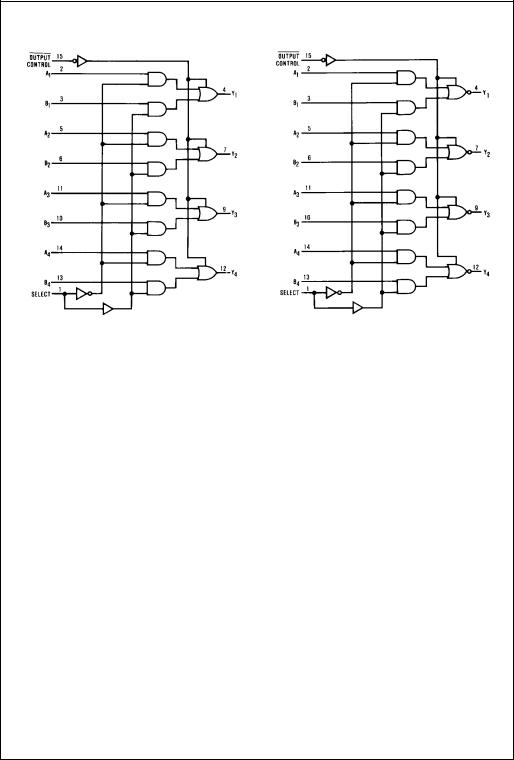

DM74AS257 • DM74AS258

Logic Diagrams

DM74AS257 |

DM74AS258 |

www.fairchildsemi.com |

2 |

Loading...

Loading...