Fairchild Semiconductor DM74ALS874BWMX, DM74ALS874BWM, DM74ALS874BNT Datasheet

April 1984

Revised February 2000

DM74ALS874B

Dual 4-Bit D-Type Edge-Triggered Flip-Flop with 3-STATE Outputs

General Description

This dual 4-bit register features totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The high-impedance state and increased high-logic-level drive provide this register with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. It is particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

The eight flip-flops of the DM74ALS874B are edge-trig- gered D-type flip-flops. On the positive transition of the clock, the Q outputs will be set to the logic states that were set up at the D inputs.

A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high-impedance state. In the high-imped- ance state the outputs neither load nor drive the bus lines significantly.

The output control does not affect the internal operation of the flip-flops. That is, the old data can be retained or new data can be entered even while the outputs are OFF.

Features

■Switching specifications at 50 pF

■Switching specifications guaranteed over full temperature and VCC range

■Advanced oxide-isolated, ion-implanted Schottky TTL process

■3-STATE buffer-type outputs drive bus lines directly

■Space saving 300 mil wide package

■Asynchronous clear

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74ALS874BWM |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

DM74ALS874BNT |

N24C |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

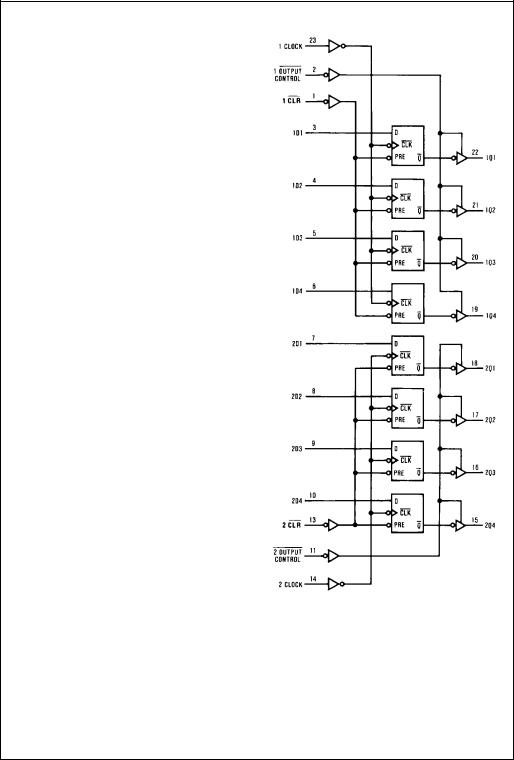

Connection Diagram

Outputs STATE-3 with Flop-Flip Triggered-Edge Type-D Bit-4 Dual DM74ALS874B

© 2000 Fairchild Semiconductor Corporation |

DS006244 |

www.fairchildsemi.com |

DM74ALS874B

Function Table |

|

|

|

Logic Diagram |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inputs |

|

|

Output |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

CLR |

|

D |

|

CLK |

|

OC |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

X |

|

X |

|

H |

|

Z |

|

|

|

L |

|

X |

|

X |

|

L |

|

L |

|

|

|

H |

|

H |

|

− |

|

L |

|

H |

|

|

|

H |

|

L |

|

− |

|

L |

|

L |

|

|

|

H |

|

X |

|

L |

|

L |

|

Q0 |

|

L = LOW State

H = HIGH State

X = Don’t Care

− = Positive Edge Transition

Z = High Impedance State

Q0 = Previous Condition of Q

www.fairchildsemi.com |

2 |

Loading...

Loading...