Mitsubishi MH4V64AXJJ-6, MH4V644AXJJ-6, MH4V644AXJJ-6S, MH4V64AXJJ-5, MH4V64AXJJ-5S Datasheet

...

Preliminary |

MITSUBISHI LSIs |

|

MH4V64/644AXJJ-5,-6,-5S,-6S |

||

Some of contents are subject |

||

to change without notice. |

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

|

|

DESCRIPTION

This is family of 4194304 - word by 64 - bit dynamic RAM module. This consists of four industry standard 4Mx16 dynamic RAMs in TSOP and one industry EEPROM in TSSOP.

The mounting of TSOP on a card edge dual in line package provides any application where high densities and large of quantities memory are required.

This is a socket-type memory module,suitable for easy interchange of addition of modules.

FEATURES

|

RAS |

CAS |

Address |

OE |

Cycle |

|

access |

access |

access |

access |

time |

|

time |

time |

time |

time |

|

|

(max.ns) |

(max.ns) |

(max.ns) |

(max.ns) |

(min.ns) |

MH4V64AXJJ-5,5S |

50 |

13 |

25 |

13 |

90 |

|

|

|

|

|

|

MH4V64AXJJ-6,6S |

60 |

15 |

30 |

15 |

110 |

|

|

|

|

|

|

MH4V644AXJJ-5,5S |

50 |

13 |

25 |

13 |

90 |

|

|

|

|

|

|

MH4V644AXJJ-6,6S |

60 |

15 |

30 |

15 |

110 |

ADDRESS

Part No. |

Row Add. |

Col Add. |

Refresh |

Refresh |

|

|

|

Cycle |

|

MH4V64AXJJ |

A0~A12 |

A0~A8 |

/RAS only Ref,Normal R/W |

8192/64ms |

CBR Ref,Hidden Ref |

4096/64ms |

|||

MH4V644AXJJ |

A0~A11 |

A0~A9 |

/RAS only Ref,Normal R/W |

4096/64ms |

|

|

|

CBR Ref,Hidden Ref |

|

APPLICATION

Main memory unit for computer,Microcomputer memory,Refresh memory for CRT.

*:Applicable to self refresh version(MH4V64/644AXJJ-5S,-6S) only

single 3.3V± 0.3V supply

single 3.3V± 0.3V supply

Low stand-by power dissipation

Low stand-by power dissipation

7.2mW- - - - - - - - - LVCMOS input level  operating power dissipation

operating power dissipation

MH4V64AXJJ-5,5S - - - - - 1584 mW(max.) MH4V64AXJJ-6,6S - - - - - 1440mW(max.) MH4V644AXJJ-5,5S - - - - 2016 mW(max.) MH4V644AXJJ-6,6S - - - - 1872 mW(max.)

Self refresh capability*

Self refresh capability*

Self refresh current - - - - 1600 uA(max.)

All input, output LVTTL compatible and low capacitance

All input, output LVTTL compatible and low capacitance

Utilizes industry standard 4Mx16 RAMs in TSOP and industry standard EEPROM in TSSOP.

Utilizes industry standard 4Mx16 RAMs in TSOP and industry standard EEPROM in TSSOP.

Includes decoupling capacitor(0.22uFx4)

Includes decoupling capacitor(0.22uFx4)

Fast page mode , Read-modify-write,

Fast page mode , Read-modify-write,

CAS before RAS refresh,Hidden refresh capabilities.  Early-write mode,OE to control output buffer

Early-write mode,OE to control output buffer

impedance.

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 1 / 25 )

Preliminary |

|

|

|

|

|

MITSUBISHI LSIs |

||||||||

MH4V64/644AXJJ-5,-6,-5S,-6S |

||||||||||||||

Some of contents are subject |

||||||||||||||

to change without notice. |

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

|||||||||||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

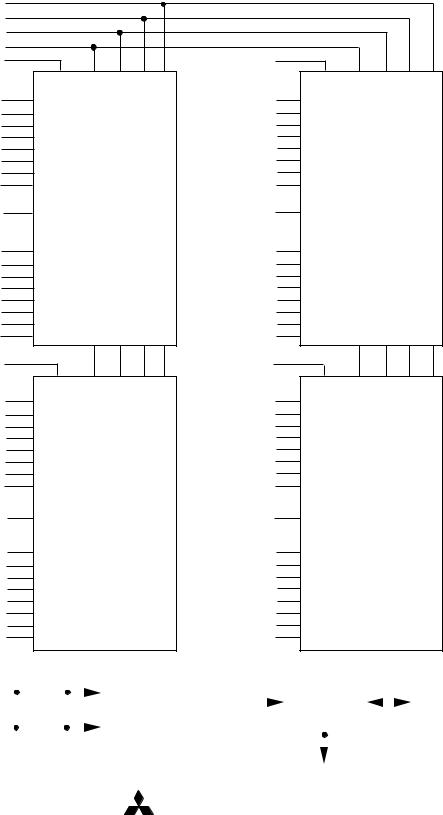

PIN CONFIGURATION |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

PIN |

|

Front side |

PIN |

Back side |

PIN |

Front side |

PIN |

Back side |

|

|||

|

|

Number |

|

Pin Name |

Number |

Pin Name |

Number |

Pin Name |

Number |

Pin Name |

|

|

||

|

1 |

|

Vss |

2 |

Vss |

73 |

/OE |

74 |

RFU |

|

|

|||

|

3 |

|

DQ0 |

4 |

DQ32 |

75 |

Vss |

76 |

Vss |

|

|

|||

|

5 |

|

DQ1 |

6 |

DQ33 |

77 |

Reserved |

78 |

Reserved |

|

|

|||

|

7 |

|

DQ2 |

8 |

DQ34 |

79 |

Reserved |

80 |

Reserved |

|

|

|||

|

9 |

|

DQ3 |

10 |

DQ35 |

81 |

Vcc |

82 |

Vcc |

|

|

|||

|

11 |

|

Vcc |

12 |

Vcc |

83 |

DQ16 |

84 |

DQ48 |

|

|

|||

|

13 |

|

DQ4 |

14 |

DQ36 |

85 |

DQ17 |

86 |

DQ49 |

|

||||

|

15 |

|

DQ5 |

16 |

DQ37 |

87 |

DQ18 |

88 |

DQ50 |

|

||||

|

17 |

|

DQ6 |

18 |

DQ38 |

89 |

DQ19 |

90 |

DQ51 |

|

||||

|

19 |

|

DQ7 |

20 |

DQ39 |

91 |

Vss |

92 |

Vss |

|

||||

|

21 |

|

Vss |

22 |

Vss |

93 |

DQ20 |

94 |

DQ52 |

|

||||

|

23 |

|

/CAS0 |

24 |

/CAS4 |

95 |

DQ21 |

96 |

DQ53 |

|

||||

|

25 |

|

/CAS1 |

26 |

/CAS5 |

97 |

DQ22 |

98 |

DQ54 |

|

||||

|

27 |

|

Vcc |

28 |

Vcc |

99 |

DQ23 |

100 |

DQ55 |

|

||||

|

29 |

|

A0 |

30 |

A3 |

101 |

Vcc |

102 |

Vcc |

|

||||

|

31 |

|

A1 |

32 |

A4 |

103 |

A6 |

104 |

A7 |

|

||||

|

33 |

|

A2 |

34 |

A5 |

105 |

A8 |

106 |

A11 |

|

||||

|

35 |

|

Vss |

36 |

Vss |

107 |

Vss |

108 |

Vss |

|

||||

|

37 |

|

DQ8 |

38 |

DQ40 |

109 |

A9 |

110 |

A12/NC(note) |

|

||||

|

39 |

|

DQ9 |

40 |

DQ41 |

111 |

A10 |

112 |

NC |

|

||||

|

41 |

|

DQ10 |

42 |

DQ42 |

113 |

Vcc |

114 |

Vcc |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

43 |

|

DQ11 |

44 |

DQ43 |

115 |

/CAS2 |

116 |

/CAS6 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

45 |

|

Vcc |

46 |

Vcc |

117 |

/CAS3 |

118 |

/CAS7 |

|

|

||

|

|

47 |

|

DQ12 |

48 |

DQ44 |

119 |

Vss |

120 |

Vss |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

49 |

|

DQ13 |

50 |

DQ45 |

121 |

DQ24 |

122 |

DQ56 |

|

||||

|

51 |

|

DQ14 |

52 |

DQ46 |

123 |

DQ25 |

124 |

DQ57 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

53 |

|

DQ15 |

54 |

DQ47 |

125 |

DQ26 |

126 |

DQ58 |

|

||||

|

55 |

|

Vss |

56 |

Vss |

127 |

DQ27 |

128 |

DQ59 |

|

||||

|

57 |

|

Reserved |

58 |

Reserved |

129 |

Vcc |

130 |

Vcc |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

59 |

|

Reserved |

60 |

Reserved |

131 |

DQ28 |

132 |

DQ60 |

|

||||

|

61 |

|

RFU |

62 |

FRU |

133 |

DQ29 |

134 |

DQ61 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

63 |

|

Vcc |

64 |

Vcc |

135 |

DQ30 |

136 |

DQ62 |

|

||||

|

65 |

|

RFU |

66 |

RFU |

137 |

DQ31 |

138 |

DQ63 |

|

||||

|

67 |

|

/WE |

68 |

RFU |

139 |

Vss |

140 |

Vss |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

69 |

|

/RAS0 |

70 |

RFU |

141 |

SDA |

142 |

SCL |

|

||||

|

71 |

|

NC |

72 |

RFU |

143 |

Vcc |

144 |

Vcc |

|

||||

|

|

|

|

|

|

|

|

RFU:Reserved Future Use |

||||||

|

|

|

|

|

|

|

|

NC,RFU,Reserved: NO CONNECTION |

||||||

|

|

Note:A12 ... MH4V64AXJJ , NC ... MH4V644AXJJ |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIT-DS-0072-0.5 |

|

|

MITSUBISHI |

|

|

26/Feb./1997 |

||||||||

|

|

|

|

|

|

ELECTRIC |

|

|

|

|

|

|

||

( 2 / 25 )

Preliminary |

MITSUBISHI LSIs |

||

MH4V64/644AXJJ-5,-6,-5S,-6S |

|||

Some of contents are subject |

|||

to change without notice. |

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

||

|

|||

|

|

|

|

Block Diagram

Address /OE /WE /RAS0 /CAS0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

/CAS1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

/CAS2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

/CAS3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

/LCAS /RAS /WE /OE

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

/UCAS D0

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

I/O16

/LCAS /RAS /WE /OE

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

/UCAS D1

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

I/O16

/CAS4

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

/CAS5

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

/CAS6

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

/CAS7

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

/LCAS /RAS /WE /OE

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

/UCAS D2

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

I/O16

/LCAS /RAS /WE /OE

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

/UCAS D3

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

I/O16

|

|

|

|

|

|

|

|

|

|

|

|

|

SERIAL PD |

||||||||

|

Vcc |

|

|

|

|

|

|

|

D0 |

to D3 |

|

|

|

|

|

|

|

SDA |

|||

|

Vss |

|

|

|

C1~C4 |

|

|

|

|

SCL |

|

|

A0 A1 |

A2 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

D0 |

to D3 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vss |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIT-DS-0072-0.5 |

|

MITSUBISHI |

|

|

|

|

26/Feb./1997 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

ELECTRIC |

|

|

|

|

|

|

|||||

( 3 / 25 )

Preliminary |

|

|

|

MITSUBISHI LSIs |

||||

MH4V64/644AXJJ-5,-6,-5S,-6S |

||||||||

Some of contents are subject |

||||||||

to change without notice. |

|

|

|

|

|

|

||

|

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

|||||||

|

|

|

|

|

|

|

||

Serial Presence Detece TABLE (MH4V64AXJJ-5,-6) |

|

|

|

|||||

|

|

|

|

|

|

|

||

Bytes |

Function described |

|

|

SPD entry data |

SPD DATA entry(Hex) |

|

||

1 |

Total # bytes of SPD memory device |

|

256 Bytes |

08 |

|

|

||

2 |

Fundamental memory type |

|

|

FPM DRAM |

01 |

|

|

|

3 |

# Row Addresses on this assembly |

|

A0-A12 |

0D |

|

|||

4 |

# Column Addresses on this assembly |

|

A0-A8 |

09 |

|

|

||

5 |

# Module Banks on this assembly |

|

1bank |

01 |

|

|

||

6 |

Data Width of this assembly... |

|

x64 |

40 |

|

|

||

7 |

... Data Width continuation |

|

|

0 |

00 |

|

|

|

8 |

Voltage interface standard of this assembly |

|

3.3V LVTTL |

02 |

|

|

||

9 |

RAS# access time of this assembly |

-5 |

50ns |

32 |

|

|

||

|

|

|

-6 |

60ns |

3C |

|

||

10 |

CAS# access time of this assembly |

-5 |

13ns |

0D |

|

|||

|

|

|

-6 |

15ns |

0F |

|

||

11 |

DIMM Configuration type (Non-parity,Parity,ECC) |

|

non parity |

00 |

|

|

||

12 |

Refresh Rate/Type |

|

|

N/R(15.625uS) |

00 |

|

|

|

13 |

DRAM width,Primary DRAM |

|

|

x16 |

10 |

|

|

|

14 |

Error Checking DRAM data width |

|

N/A |

00 |

|

|

||

15-31 |

Reserved for future offerings |

|

|

open |

00 |

|

|

|

32-61 |

Superset Memory type(may be used in future) |

|

open |

00 |

|

|

||

62 |

SPD Data Revision Code |

|

|

Rev 1 |

01 |

|

|

|

63 |

Checksum for bytes 0-62 |

|

|

Check sum for -5 |

32 |

|

|

|

|

|

|

|

Check sum for -6 |

3E |

|

||

64-71 |

Manufacturers JEDEC ID code per JEP-106 |

|

MITSUBISHI |

1CFFFFFFFFFFFFFF |

|

|||

72 |

Manufacturing location |

|

|

Miyoshi,Japan |

01 |

|

|

|

|

|

|

|

Tajima,Japan |

02 |

|

|

|

|

|

|

|

NC,USA |

03 |

|

|

|

|

|

|

|

Germany |

04 |

|

|

|

73-90 |

Manufacturer's Part Number |

|

MH4V64AXJJ-5 |

4D483456363441584A4A2D352D35202020202020 |

|

|||

|

|

|

|

MH4V64AXJJ-6 |

4D483456363441584A4A2D362D36202020202020 |

|

||

91-92 |

Revision Code |

|

|

PCB revision |

rrrr |

|

||

93-94 |

Manufacturing date |

|

|

year/week code |

yy/ww |

|

||

95-98 |

Assembly Serial Number |

|

|

serial number |

ssssssss |

|

||

99-125 |

Manufacturer Specific Data |

|

|

open |

00 |

|

|

|

126-127 |

Reserved |

|

|

open |

00 |

|

|

|

128-255 |

Open User Free-Form area not defined |

|

open |

00 |

|

|

||

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 4 / 25 )

Preliminary |

|

|

|

|

MITSUBISHI LSIs |

|||||

MH4V64/644AXJJ-5,-6,-5S,-6S |

||||||||||

Some of contents are subject |

||||||||||

to change without notice. |

|

|

|

|

|

|

|

|||

|

|

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

||||||||

|

|

|

|

|

|

|

|

|||

|

Serial Presence Detece TABLE (MH4V64AXJJ-5S,-6S) |

|||||||||

|

|

|

|

|

|

|

|

|

||

|

Bytes |

Function described |

|

|

|

SPD entry data |

SPD DATA entry(Hex) |

|

||

|

1 |

Total # bytes of SPD memory device |

|

256 Bytes |

08 |

|

|

|||

|

2 |

Fundamental memory type |

|

|

|

FPM DRAM |

01 |

|

|

|

|

3 |

# Row Addresses on this assembly |

|

A0-A12 |

0D |

|

||||

|

4 |

# Column Addresses on this assembly |

|

A0-A8 |

09 |

|

|

|||

|

5 |

# Module Banks on this assembly |

|

1bank |

01 |

|

|

|||

|

6 |

Data Width of this assembly... |

|

|

|

x64 |

40 |

|

|

|

|

7 |

... Data Width continuation |

|

|

|

0 |

00 |

|

|

|

|

8 |

Voltage interface standard of this assembly |

|

3.3V LVTTL |

02 |

|

|

|||

|

9 |

RAS# access time of this assembly |

|

-5S |

50ns |

32 |

|

|

||

|

|

|

|

|

-6S |

60ns |

3C |

|

||

|

10 |

CAS# access time of this assembly |

|

-5S |

13ns |

0D |

|

|||

|

|

|

|

|

-6S |

15ns |

0F |

|

||

|

11 |

DIMM Configuration type (Non-parity,Parity,ECC) |

|

non parity |

00 |

|

|

|||

|

12 |

Refresh Rate/Type |

|

|

|

S/R(15.625uS) |

80 |

|

|

|

|

13 |

DRAM width,Primary DRAM |

|

|

|

x16 |

10 |

|

|

|

|

14 |

Error Checking DRAM data width |

|

N/A |

00 |

|

|

|||

|

15-31 |

Reserved for future offerings |

|

|

|

open |

00 |

|

|

|

|

32-61 |

Superset Memory type(may be used in future) |

|

open |

00 |

|

|

|||

|

62 |

SPD Data Revision Code |

|

|

|

Rev 1 |

01 |

|

|

|

|

63 |

Checksum for bytes 0-62 |

|

|

|

Check sum for -5 |

B2 |

|

||

|

|

|

|

|

|

Check sum for -6 |

BE |

|

||

|

64-71 |

Manufacturers JEDEC ID code per JEP-106 |

|

MITSUBISHI |

1CFFFFFFFFFFFFFF |

|

||||

|

72 |

Manufacturing location |

|

|

|

Miyoshi,Japan |

01 |

|

|

|

|

|

|

|

|

|

Tajima,Japan |

02 |

|

|

|

|

|

|

|

|

|

NC,USA |

03 |

|

|

|

|

|

|

|

|

|

Germany |

04 |

|

|

|

|

73-90 |

Manufacturer's Part Number |

|

|

|

MH4V64AXJJ-5S |

4D483456363441584A4A2D355335532020202020 |

|

||

|

|

|

|

|

|

MH4V64AXJJ-6S |

4D483456363441584A4A2D365336532020202020 |

|

||

|

91-92 |

Revision Code |

|

|

|

PCB revision |

rrrr |

|

||

|

93-94 |

Manufacturing date |

|

|

|

year/week code |

yy/ww |

|

||

|

95-98 |

Assembly Serial Number |

|

|

|

serial number |

ssssssss |

|

||

|

99-125 |

Manufacturer Specific Data |

|

|

|

open |

00 |

|

|

|

|

126-127 |

Reserved |

|

|

|

open |

00 |

|

|

|

|

128-255 |

Open User Free-Form area not defined |

|

open |

00 |

|

|

|||

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 5 / 25 )

Preliminary |

|

|

|

MITSUBISHI LSIs |

|||||

MH4V64/644AXJJ-5,-6,-5S,-6S |

|||||||||

Some of contents are subject |

|||||||||

to change without notice. |

|

|

|

|

|

|

|||

|

|

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

|||||||

|

|

|

|

|

|

|

|||

|

Serial Presence Detece TABLE (MH4V644AXJJ-5,-6) |

|

|

|

|||||

|

|

|

|

|

|

|

|

||

|

Bytes |

Function described |

|

|

SPD entry data |

SPD DATA entry(Hex) |

|

||

0 |

Defines # bytes written into serial memory at module mfgr |

128 |

80 |

|

|

||||

1 |

Total # bytes of SPD memory device |

|

256 Bytes |

08 |

|

|

|||

2 |

Fundamental memory type |

|

|

FPM DRAM |

01 |

|

|

||

3 |

# Row Addresses on this assembly |

|

A0-A11 |

0C |

|

||||

4 |

# Column Addresses on this assembly |

|

A0-A9 |

0A |

|

||||

5 |

# Module Banks on this assembly |

|

1bank |

01 |

|

|

|||

6 |

Data Width of this assembly... |

|

x64 |

40 |

|

|

|||

7 |

... Data Width continuation |

|

|

0 |

00 |

|

|

||

8 |

Voltage interface standard of this assembly |

|

3.3V LVTTL |

02 |

|

|

|||

9 |

RAS# access time of this assembly |

-5 |

50ns |

32 |

|

|

|||

|

|

|

|

-6 |

60ns |

3C |

|

||

10 |

CAS# access time of this assembly |

-5 |

13ns |

0D |

|

||||

|

|

|

|

-6 |

15ns |

0F |

|

||

11 |

DIMM Configuration type (Non-parity,Parity,ECC) |

|

non parity |

00 |

|

|

|||

12 |

Refresh Rate/Type |

|

|

N/R(15.625uS) |

00 |

|

|

||

13 |

DRAM width,Primary DRAM |

|

|

x16 |

10 |

|

|

||

14 |

Error Checking DRAM data width |

|

N/A |

00 |

|

|

|||

15-31 |

Reserved for future offerings |

|

|

open |

00 |

|

|

||

32-61 |

Superset Memory type(may be used in future) |

|

open |

00 |

|

|

|||

62 |

SPD Data Revision Code |

|

|

Rev 1 |

01 |

|

|

||

63 |

Checksum for bytes 0-62 |

|

|

Check sum for -5 |

32 |

|

|

||

|

|

|

|

|

Check sum for -6 |

3E |

|

||

64-71 |

Manufacturers JEDEC ID code per JEP-106 |

|

MITSUBISHI |

1CFFFFFFFFFFFFFF |

|

||||

72 |

Manufacturing location |

|

|

Miyoshi,Japan |

01 |

|

|

||

|

|

|

|

|

Tajima,Japan |

02 |

|

|

|

|

|

|

|

|

NC,USA |

03 |

|

|

|

|

|

|

|

|

Germany |

04 |

|

|

|

73-90 |

Manufacturer's Part Number |

|

MH4V644AXJJ-5 |

4D48345636343441584A4A2D352D352020202020 |

|

||||

|

|

|

|

|

MH4V644AXJJ-6 |

4D48345636343441584A4A2D362D362020202020 |

|

||

91-92 |

Revision Code |

|

|

PCB revision |

rrrr |

|

|||

93-94 |

Manufacturing date |

|

|

year/week code |

yy/ww |

|

|||

95-98 |

Assembly Serial Number |

|

|

serial number |

ssssssss |

|

|||

99-125 |

Manufacturer Specific Data |

|

|

open |

00 |

|

|

||

126-127 |

Reserved |

|

|

open |

00 |

|

|

||

128-255 |

Open User Free-Form area not defined |

|

open |

00 |

|

|

|||

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 6 / 25 )

Preliminary |

|

|

|

MITSUBISHI LSIs |

||||

MH4V64/644AXJJ-5,-6,-5S,-6S |

||||||||

Some of contents are subject |

||||||||

to change without notice. |

|

|

|

|

|

|

||

|

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

|||||||

|

|

|

|

|

|

|

||

Serial Presence Detece TABLE (MH4V644AXJJ-5S,-6S) |

|

|

|

|||||

|

|

|

|

|

|

|

||

Bytes |

Function described |

|

|

SPD entry data |

SPD DATA entry(Hex) |

|

||

0 |

Defines # bytes written into serial memory at module mfgr |

128 |

80 |

|

|

|||

1 |

Total # bytes of SPD memory device |

|

256 Bytes |

08 |

|

|

||

2 |

Fundamental memory type |

|

|

FPM DRAM |

01 |

|

|

|

3 |

# Row Addresses on this assembly |

|

A0-A11 |

0C |

|

|||

4 |

# Column Addresses on this assembly |

|

A0-A9 |

0A |

|

|||

5 |

# Module Banks on this assembly |

|

1bank |

01 |

|

|

||

6 |

Data Width of this assembly... |

|

x64 |

40 |

|

|

||

7 |

... Data Width continuation |

|

0 |

00 |

|

|

||

8 |

Voltage interface standard of this assembly |

|

3.3V LVTTL |

02 |

|

|

||

9 |

RAS# access time of this assembly |

-5S |

50ns |

32 |

|

|

||

|

|

|

-6S |

60ns |

3C |

|

||

10 |

CAS# access time of this assembly |

-5S |

13ns |

0D |

|

|||

|

|

|

-6S |

15ns |

0F |

|

||

11 |

DIMM Configuration type (Non-parity,Parity,ECC) |

|

non parity |

00 |

|

|

||

12 |

Refresh Rate/Type |

|

|

S/R(15.625uS) |

80 |

|

|

|

13 |

DRAM width,Primary DRAM |

|

x16 |

10 |

|

|

||

14 |

Error Checking DRAM data width |

|

N/A |

00 |

|

|

||

15-31 |

Reserved for future offerings |

|

open |

00 |

|

|

||

32-61 |

Superset Memory type(may be used in future) |

|

open |

00 |

|

|

||

62 |

SPD Data Revision Code |

|

|

Rev 1 |

01 |

|

|

|

63 |

Checksum for bytes 0-62 |

|

|

Check sum for -5S |

B2 |

|

||

|

|

|

|

Check sum for -6S |

BE |

|

||

64-71 |

Manufacturers JEDEC ID code per JEP-106 |

|

MITSUBISHI |

1CFFFFFFFFFFFFFF |

|

|||

72 |

Manufacturing location |

|

|

Miyoshi,Japan |

01 |

|

|

|

|

|

|

|

Tajima,Japan |

02 |

|

|

|

|

|

|

|

NC,USA |

03 |

|

|

|

|

|

|

|

Germany |

04 |

|

|

|

73-90 |

Manufacturer's Part Number |

|

MH4V644AXJJ-5S |

4D48345636343441584A4A2D3553355320202020 |

|

|||

|

|

|

|

MH4V644AXJJ-6S |

4D48345636343441584A4A2D3653365320202020 |

|

||

91-92 |

Revision Code |

|

|

PCB revision |

rrrr |

|

||

93-94 |

Manufacturing date |

|

|

year/week code |

yy/ww |

|

||

95-98 |

Assembly Serial Number |

|

|

serial number |

ssssssss |

|

||

99-125 |

Manufacturer Specific Data |

|

open |

00 |

|

|

||

126-127 |

Reserved |

|

|

open |

00 |

|

|

|

128-255 |

Open User Free-Form area not defined |

|

open |

00 |

|

|

||

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 7 / 25 )

Preliminary |

MITSUBISHI LSIs |

||

MH4V64/644AXJJ-5,-6,-5S,-6S |

|||

Some of contents are subject |

|||

to change without notice. |

FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

||

|

|||

|

|

|

|

FUNCTION

The MH4V64/644AXJJ provide, in addition to normal read, write, and read-modify-write operations,

a number of other functions, e.g., Fast page mode, /RAS-only refresh, and delayed-write. The input conditions for each are shown in Table 1.

Table 1 Input conditions for each mode

|

Operation |

|

|

Inputs |

|

|

Input/Output |

Refresh |

Remark |

|||

|

/RAS |

/CAS |

/W |

/OE |

Row |

Column |

Input |

Output |

||||

|

|

address |

address |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||

Read |

ACT |

ACT |

NAC |

ACT |

APD |

APD |

OPN |

VLD |

YES |

Fast page |

||

|

|

|

|

|

|

|

|

|

|

|

||

Write (Early write) |

ACT |

ACT |

ACT |

DNC |

APD |

APD |

VLD |

OPN |

YES |

|||

mode |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||

Write (Delayed write) |

ACT |

ACT |

ACT |

DNC |

APD |

APD |

VLD |

IVD |

YES |

|||

identical |

||||||||||||

Read-modify-write |

ACT |

ACT |

ACT |

ACT |

APD |

APD |

VLD |

VLD |

YES |

|||

|

||||||||||||

/RAS-only refresh |

ACT |

NAC |

DNC |

DNC |

APD |

DNC |

DNC |

OPN |

YES |

|

||

Hidden refresh |

ACT |

ACT |

NAC |

ACT |

APD |

DNC |

OPN |

VLD |

YES |

|

||

/CAS before /RAS refresh |

ACT |

ACT |

NAC |

DNC |

DNC |

DNC |

DNC |

OPN |

YES |

|

||

Standby |

NAC |

DNC |

DNC |

DNC |

DNC |

DNC |

DNC |

OPN |

NO |

|

||

Self refresh * |

ACT |

ACT |

NAC |

DNC |

DNC |

DNC |

DNC |

OPN |

YES |

|

||

Note : ACT : active, NAC : nonactive, DNC : don' t care, VLD : valid, IVD : Invalid, APD : applied, OPN : open

*MH4V64/644AXJJ-5S,-6S only

MIT-DS-0072-0.5 |

MITSUBISHI |

26/Feb./1997 |

|

ELECTRIC |

|

( 8 / 25 )

Loading...

Loading...