DYNEX MAS9264T95LD, MAS9264T95LC, MAS9264T95LB, MAS9264T95FS, MAS9264T95FE Datasheet

...

MA9264

MA9264

Radiation Hard 8192x8 Bit Static RAM

Replaces June 1999 version, DS3692-6.0 |

DS3692-7.0 January 2000 |

The MA9264 64k Static RAM is configured as 8192x8 bits and manufactured using CMOS-SOS high performance, radiation hard, 1.5μm technology.

The design uses a 6 transistor cell and has full static operation with no clock or timing strobe required. Address input buffers are deselected when chip select is in the HIGH state.

See Application Note “Overview of the Dynex Semiconductor Radiation Hard 1.5μm CMOS/SOS SRAM Range”.

|

|

|

|

|

|

|

|

|

|

|

|

|

Operation Mode |

|

CS |

CE |

|

OE |

WE |

I/O |

Power |

||||

|

|

|

|

|

|

|

|

|

|

|||

Read |

|

L |

H |

|

L |

|

H |

D OUT |

|

|||

Write |

|

L |

H |

|

X |

|

L |

D IN |

ISB1 |

|||

Output Disable |

|

L |

H |

|

H |

|

H |

High Z |

|

|||

|

|

|

|

|

|

|

|

|

|

|||

Standby |

|

H |

X |

|

X |

|

X |

High Z |

ISB2 |

|||

|

|

X |

L |

|

X |

|

X |

X |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1: Truth Table

FEATURES

■1.5μm CMOS-SOS Technology

■Latch-up Free

■Fast Access Time 70ns Typical

■Total Dose 106 Rad(Si)

■Transient Upset >1011 Rad(Si)/sec

■SEU 4.3 x 10-11 Errors/bitday

■Single 5V Supply

■Three State Output

■Low Standby Current 100μA Typical

■-55°C to +125°C Operation

■All Inputs and Outputs Fully TTL or CMOS Compatible

■Fully Static Operation

A12 |

A |

|

|

|

D |

R |

|

A9 |

D |

O |

|

A8 |

R |

W |

|

E |

|||

|

|

||

A4 |

S |

D |

|

S |

|||

E |

|||

A3 |

|

||

B |

C |

||

|

|||

|

O |

||

A6 |

U |

||

F |

D |

||

A5 |

|||

F |

E |

||

|

|||

A7 |

E |

R |

|

R |

|

CS

CE

WE

OE

A10 A0 A1 A2 A11

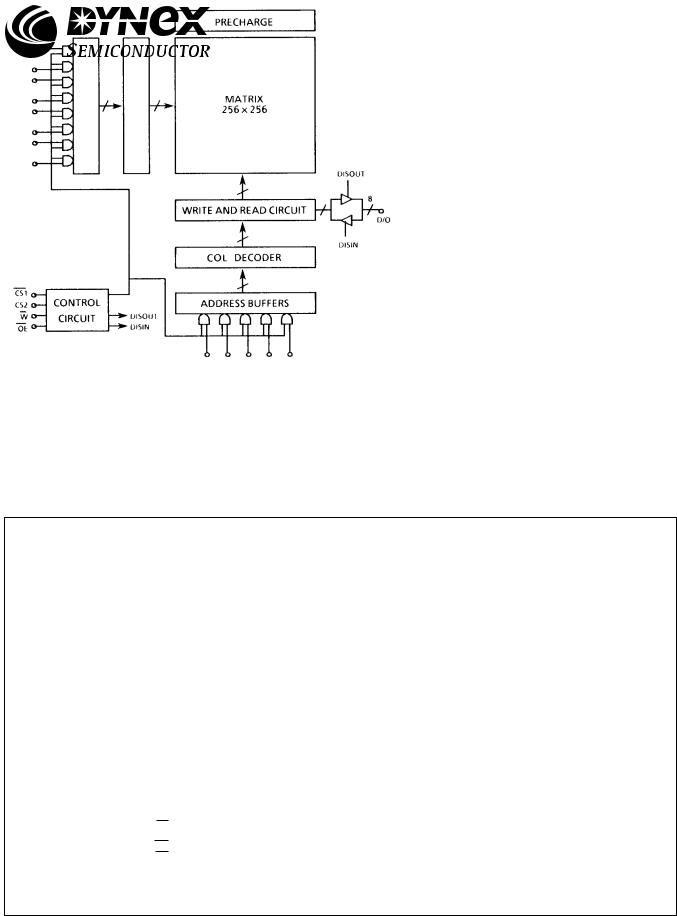

Figure 2: Block Diagram

1/15

MA9264

SIGNAL DEFINITIONS

A0-12

Address input pins which select a particular eight bit word within the memory array.

D0-7

Bidirectional data pins which serve as data outputs during a read operation and as data inputs during a write operation.

CS

Chip Select, which, at low level, activates a read or write operation. When at a high level it defaults the SRAM to a prechargencondition and holds the data output drivers in a high impedance state.

WE

Write Enable which when at a low level enables a write and holds data output drivers in a high impedance state. When at a high level, it enables a read.

OE

Output Enable which when at a high level holds the data output drivers in a high impedance state. When at a low level, data output driver state is defined by CS, WE and CE. If this signal is not used it must be connected to VSS.

CE

Chip Enable which when at a high level allows normal operation. When at a low level it defaults the SRAM to a precharge condition, disables the input circuits on all input pins and holds the data output drivers in a high impedance state. If this signal is not used it must be connected to VDD.

2/15

MA9264

CHARACTERISTICS AND RATINGS

Symbol |

Parameter |

Min. |

Max. |

Units |

|

|

|

|

|

VCC |

Supply Voltage |

-0.5 |

7.0 |

V |

VI |

Input Voltage |

-0.3 |

VDD+0.3 |

V |

|

|

|

|

|

TA |

Operating Temperature |

-55 |

125 |

°C |

|

|

|

|

|

TS |

Storage Temperature |

-65 |

150 |

°C |

Figure 3: Absolute Maximum Ratings

Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functlonal operation of the device at these condltions, or at any other condition above those indicated in the operations section of this specification, is not Implied Exposure to absolute maxlmum rating conditions for extended perlods may affect device reliability.

Notes for Tables 4 and 5:

Characteristics apply to pre radiation at TA = -55°C to +125°C with VDD = 5V ±10% and to post 100k Rad(Si) total dose radiation at TA = 25°C with VDD = 5V ±10% (characteristics at higher radiation levels available on request). GROUP A SUBGROUPS 1, 2, 3.

Symbol |

Parameter |

|

Conditions |

(Option) |

Min. |

Typ. |

Max. |

Units |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

Supply voltage |

|

- |

|

|

|

|

4.5 |

5.0 |

5.5 |

V |

|

VlH |

Logical ‘1’ Input Voltage |

|

- |

|

|

|

(TTL) |

VDD/2 |

- |

VDD |

V |

|

|

|

|

|

|

|

|

|

(CMOS) |

0.8 VDD |

- |

VDD |

V |

VlL |

Logical ‘0’ Input Voltage |

|

- |

|

|

|

(TTL) |

VSS |

- |

0.8 |

V |

|

|

|

|

|

|

|

|

|

(CMOS) |

VSS |

- |

0.2 VDD |

V |

VOH1 |

Logical ‘1’ Output Voltage |

|

IOH1 = -2mA |

|

2.4 |

- |

- |

V |

||||

VOH2 |

Logical ‘1’ Output Voltage |

|

IOH2 = -1mA |

|

VDD -0.5 |

- |

- |

V |

||||

VOL |

Logical ‘0’ Output Voltage |

|

IOL = 4mA |

|

- |

- |

0.4 |

V |

||||

ILI |

Input Leakage Current |

|

VIN = VDD or VSS All inputs |

|

- |

- |

±10 |

μA |

||||

ILO |

Output Leakage Current |

|

Chip disabled, VOUT = VDD or VSS |

- |

- |

±10 |

μA |

|||||

ISB1 |

Selected Static Current (CMOS) |

|

All inputs = VDD -0.2V |

|

- |

0.1 |

10 |

mA |

||||

|

|

|

except |

CS |

= VSS +0.2V |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||

IDD |

Dynamic Operating Current |

|

fRC = 1MHz, all inputs |

|

- |

6 |

18 |

mA |

||||

|

(CMOS) |

|

switching, VIH = VDD -0.2V |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

ISB2 |

Standby Supply Current |

|

|

|

= VDD -0.2V |

|

- |

0.1 |

10 |

mA |

||

|

|

CS |

|

|||||||||

|

|

|

|

CE = VSS +0.2V |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

Figure 4: Electrical Characteristics |

|

|

|

|

||||||

Symbol |

Parameter |

|

Conditions |

(Option) |

|

Min. |

Typ. |

Max. |

Units |

||

|

|

|

|

|

|

|

|

|

|

|

|

VDR |

VCC for Data Retention |

|

|

|

= VDR, CE = VSS |

|

|

2.0 |

- |

- |

V |

|

|

CS |

|

|

|||||||

IDDR |

Data Retention Current |

|

|

|

= VDR, VDR = 2.0V |

|

|

- |

0.05 |

4 |

mA |

|

|

CS |

|

|

|||||||

|

|

|

|

CE = VSS |

|

|

|

|

|

|

|

|

|

Figure 5: Data Retention Characteristics |

|

|

|

|

|||||

3/15

MA9264

AC CHARACTERISTICS

Conditions of Test for Tables 5 and 6:

1.Input pulse = VSS to 3.0V (TTL) and VSS to 4.0V (CMOS).

2.Times measurement reference level = 1.5V.

3.Input Rise and Fall times ≤5ns.

4.Output load 1TTL gate and CL = 60pF.

5.Transition is measured at ±500mV from steady state.

6.This parameter is sampled and not 100% tested.

Notes for Tables 6 and 7:

Characteristics apply to pre-radiation at TA = -55°C to +125°C with VDD = 5V±10% and to post 100k Rad(Si) total dose radiation at TA = 25°C with VDD = 5V ±10%. GROUP A SUBGROUPS 9, 10, 11.

|

|

MAX9264X70 |

MAX9264X95 |

|

||||

Symbol |

Parameter |

Min |

|

Max |

Min |

|

Max |

Units |

|

|

|||||||

|

|

|

|

|

|

|

|

|

TAVAVR |

Read Cycle Time |

70 |

|

- |

95 |

|

- |

ns |

TAVQV |

Address Access Time |

- |

|

65 |

- |

|

90 |

ns |

TEHQV |

Chip Select Access Time |

- |

|

70 |

- |

|

95 |

ns |

TSLQV |

Chip Enable Access Time |

- |

|

70 |

- |

|

95 |

ns |

TEHQX (5,6) |

Chip Selection to Output in Low Z |

15 |

|

- |

15 |

|

- |

ns |

TSLQX (5,6) |

Chip Enable to Output in Low Z |

15 |

|

- |

15 |

|

- |

ns |

TELQZ (5,6) |

Chip Deselection to Output in High Z |

0 |

|

20 |

0 |

|

20 |

ns |

TSHQZ (5,6) |

Chip Disable to Output in High Z |

0 |

|

20 |

0 |

|

20 |

ns |

TAXQX |

Output Hold from Address Change |

30 |

|

- |

40 |

|

- |

ns |

TGLQV |

Output Enable Access Time |

- |

|

25 |

- |

|

30 |

ns |

TGLQX (5,6) |

Output Enable to Output in Low Z |

15 |

|

- |

15 |

|

- |

ns |

TGHQZ (5,6) |

Output Enable to Output in High Z |

0 |

|

20 |

0 |

|

20 |

ns |

|

|

|

|

|

|

|

|

|

|

Figure 6: Read Cycle AC Electrical Characteristics |

|

|

|

|

|

|

|

|

|

MAX9264X70 |

MAX9264X95 |

|

||||

Symbol |

Parameter |

Min |

|

Max |

Min |

|

Max |

Units |

|

|

|||||||

|

|

|

|

|

|

|

|

|

TAVAVW |

Write Cycle Tlme |

55 |

|

- |

60 |

|

- |

ns |

TEHWH |

Chip Selection to End of Write |

50 |

|

- |

60 |

|

- |

ns |

TSLWH |

Chip Enable to End of Write |

50 |

|

- |

60 |

|

- |

ns |

TAVWH |

Address Valid to End of Write |

50 |

|

- |

55 |

|

- |

ns |

TAVWL |

Address Set Up Time |

0 |

|

- |

0 |

|

- |

ns |

TWLWH |

Write Pulse Width |

40 |

|

- |

45 |

|

- |

ns |

TWHAV |

Write Recovery Time |

0 |

|

- |

0 |

|

- |

ns |

TWLQZ (5,6) |

Wnte to Output in High Z |

0 |

|

20 |

0 |

|

20 |

ns |

TDVWH |

Data to Write Time Overlap |

25 |

|

- |

30 |

|

- |

ns |

TWHDX |

Data Hold from Write |

0 |

|

- |

0 |

|

- |

ns |

TWHQX (5,6) |

Output Active from End to Write |

0 |

|

20 |

0 |

|

20 |

ns |

|

|

|

|

|

|

|

|

|

Figure 7: Write Cycle AC Electrical Characteristics

4/15

MA9264

Symbol |

Parameter |

Conditions |

Min. |

Typ. |

Max. |

Units |

|

|

|

|

|

|

|

CIN |

Input Capacitance |

Vl = 0V |

- |

3 |

5 |

pF |

COUT |

Output Capacitance |

VI/O = 0V |

- |

5 |

7 |

pF |

Note: TA = 25°C and f = 1MHz. Data obtained by characterisation or analysis; not routinely measured.

Figure 8: Capacitance

Symbol |

Parameter |

|

Conditions |

|

|

|

|

FT |

Basic Functionality |

|

VDD = 4.5V - 5.5V, FREQ = 1MHz |

|

|

|

VIL = VSS, VIH = VDD, VOL £ 1.5V, VOH ³ 1.5V |

|

|

|

TEMP = -55°C to +125°C, GPS PATTERN SET |

|

|

|

GROUP A SUBGROUPS 7, 8A, 8B |

|

|

|

|

|

|

Figure 9: Functionality |

|

Subgroup |

Definition |

|

|

1 |

Static characteristics specified in Tables 4 and 5 at +25°C |

2 |

Static characteristics specified in Tables 4 and 5 at +125°C |

3 |

Static characteristics specified in Tables 4 and 5 at -55°C |

7 |

Functional characteristics specified in Table 9 at +25°C |

8A |

Functional characteristics specified in Table 9 at +125°C |

8B |

Functional characteristics specified in Table 9 at -55°C |

9 |

Switching characteristics specified in Tables 6 and 7 at +25°C |

10 |

Switching characteristics specified in Tables 6 and 7 at +125°C |

11 |

Switching characteristics specified in Tables 6 and 7 at -55°C |

|

|

Figure 10: Definition of Subgroups

5/15

Loading...

Loading...