DYNEX MAS31753FS, MAS31753FL, MAS31753FE, MAS31753FC, MAS31753FB Datasheet

...

MA31753

1/30

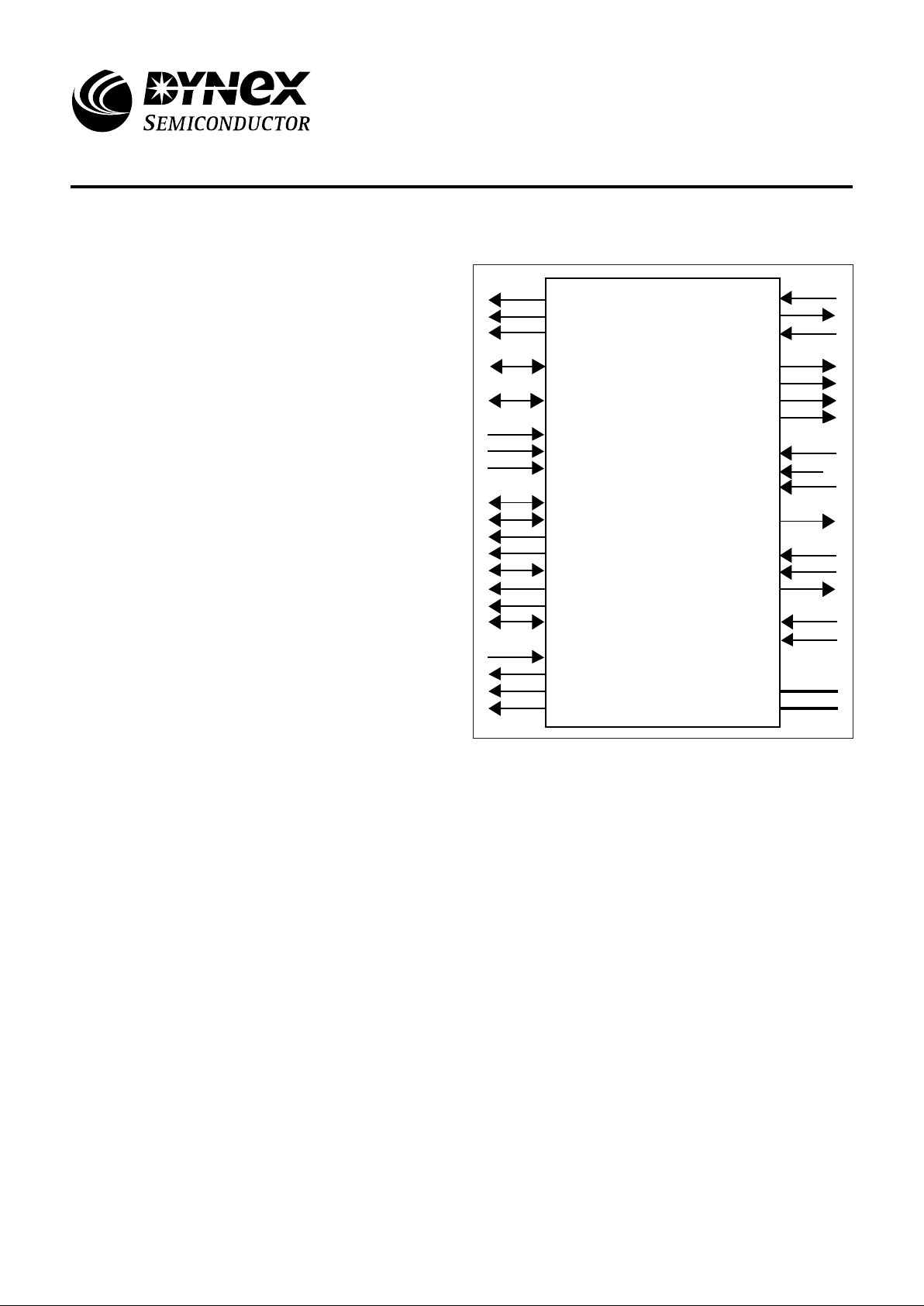

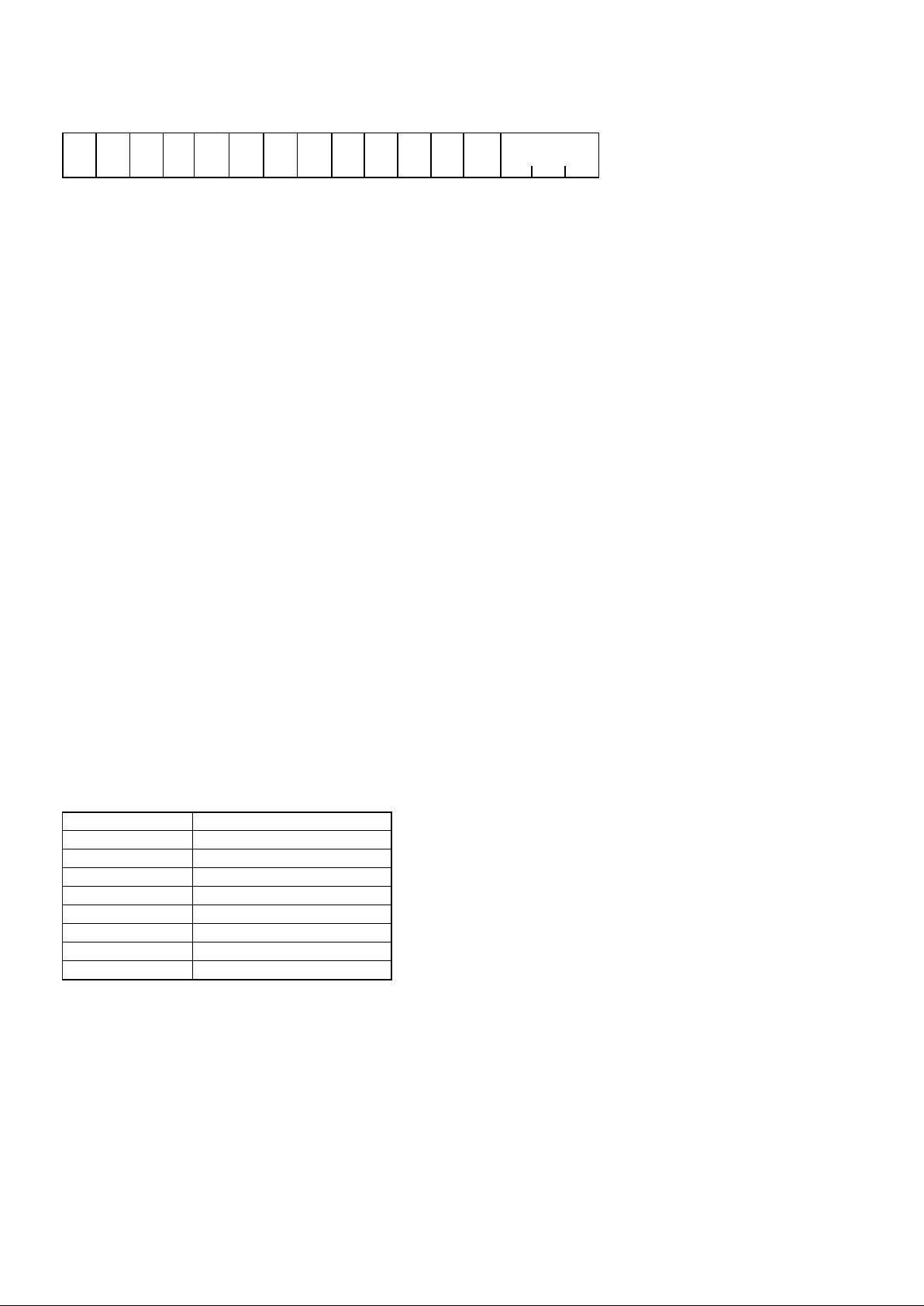

AS[0:3]

PS[0:3]

PB[0:3]

D[0:16]

A[0:15]

CSN

CLK

RESETN

DSN

AS

MION

OIN

RDWN

RDN

WRN

RDYN

GRANTN

REQN

LOCKN

DMAKN

DREQN[0:3]

DACKN[0:3]

DMAE

SEC/FIRSTN

DONEN

AKRDN

AKWRN

EXADEN

PEN

MPROEN

INTRN

REQINN

GEINN

GEOUTN

DPARN

DTON

VDD

VSS

MA31753

DMAC

The MA31753 Direct Memory Access Controller (DMAC) is

a peripheral interface circuit design primarily for use with the

MA31750 microprocessor. Each DMAC provides up to four

independant, prioritised channels each of which can perform

DMA transfers between memory and/or I/O devices using the

MA31750 bus. Each channel has its own programmable

internal priority and can be masked under program control.

Further, individual channels have their own associated status

and control words enabling an individual channel to be re-

programmed without disturbing transfers which may be taking

place on other channels. Three basic transfer modes are

available:

Direct Memory to I/O peripheral transfers,

Direct I/O to Memory transfers,

Memory to Memory transfers,

I/O to I/O transfers.

The MA31753 interfaces directly to the MA31750 bus,

directly supporting on chip parity generation and supporting

expanded memory via an MA31751 MMU with either 1 MWord

(1750A mode) or 16MWords (1750B mode) of logical memory.

The MA31753 uses System memory to hold address and

count information for each transfer. Once this information has

been prepared by the processor the DMAC can conduct a

number of transfers without further processor intervention.

FEATURES

■ Radiation Hard CMOS SOS Technology

■ Four Independant DMA Channels

■ MIL-STD-1750A or B Operation in an MA31750 System

■ Capable of Processor Independant Table Driven

Operation

■ Memory to Memory, I/O to Memory, Memory to I/O and

I/O to I/O Transfers Supported

■ Masking of Individual Channel DMA Requests

■ Simple MA31750 Bus Interface

■ Single Word, Double Word or Multi-Word Transfers for

each of the DMA Channels

■ Cascade Interface Allows for Channel Expansion

■ Programmable Channel Priority

■ Parity Checking Available

Figure 1: Pin Connections - Top View

MA31753

DMA Controller (DMAC) For An MA31750 System

Replaces June 1999 version, DS3825-4.0 DS3825-5.0 January 2000

MA31753

2/30

1.0 GENERAL DESCRIPTION

The MA31753 DMA controller has 4 channels from which

independant transfers can be executed. These channels have

programmable priorities and can be masked. They can also be

enabled and disabled under software control.

The data can be transferred in several modes - single word

mode, double word mode and burst mode. It can be

transferred to and from both incrementing and decrementing

memory and IO addressing space. The single and double word

modes transfer data in 1 or 2 bus cycles when the simple

handshaking mechanism is enabled.

If more than 4 channels are required, several DMA

controllers can be cascaded together to give channel

expansion.

Once a channel has requested a transfer, and the bus

arbiter has granted bus control to the DMA, then the DMA

issues an acknowledge signal to the channel to be serviced. It

also pulses read or write strobes which can be gated with the

channel acknowledge signal to provide read and write strobes

for the requesting hardware.

DMA instructions can be programmed into memory on the

DMA. The transfers defined by these instructions can be

executed in sequence if they are “chained together”. In this

way, DMA transfers can take place continuously with data that

is held in seperate memory areas.

There is software access to all internal registers. These

registers have parity protection. By setting certain bits in

registers, requests can be initiated for area to area transfers on

channels 0 and 1. Interrupts for each channel can also be

issued.

2.0 INITIALISATION

After RESETN has been removed the DMA is

automatically initiated to be disabled with odd parity, the

channel priority order is 0, 1, 2, 3, C (C is the cascaded input)

and all channels are masked. At this point, before the DMA is

used further, the DMA instructions should be programmed into

the DMA internal RAM. Once all the instructions needed are in

place, the common features (ie. features that apply to all

channels) on the DMA can be programmed.These features

should be initialised to the users requirements.

The bus parity may be changed immediately after

RESETN goes inactive when the MA31750 reads the

configuration word ie. When the DMA detects the XIO address

0x8410, it snoops the data bus and latches the parity bit into an

internal copy. This internal copy can later be changed by

writing to the DMA Mode / Status register.

The DMA enable / disable follows the DMAE input - when

this input is high, the DMA device is enabled. When DMAE is

low, the DMA is disabled.

The channel priority and masking can be changed by

writing to the DMA Mode / Status register.

Once the common characteristics of the DMA have been

set up, the DMA individual channels can be programmed.

Each channel has a mode register that should be programmed

with an instruction number as that channel is activated (by

writing the mode word).

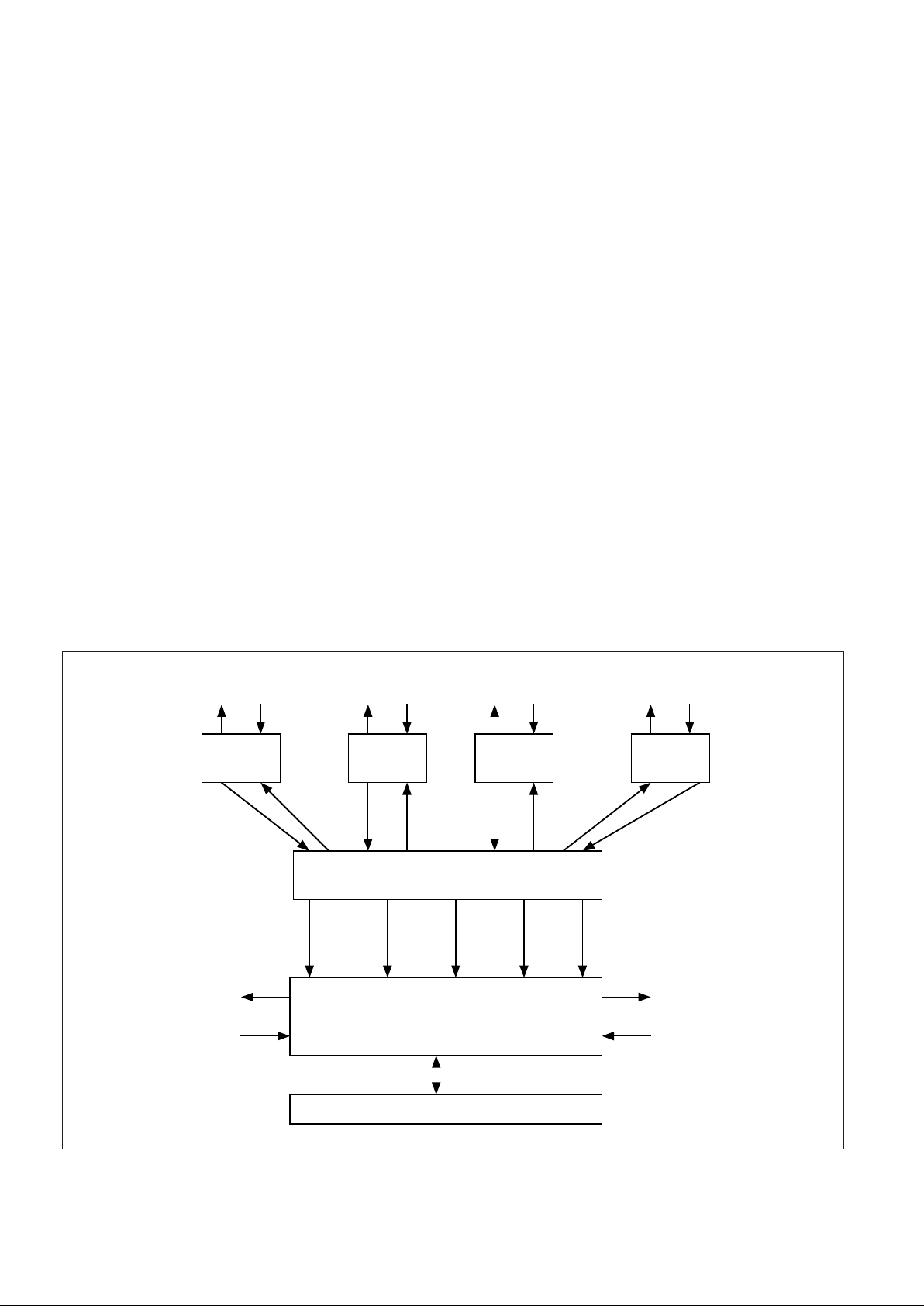

Figure 2: Block Diagram Representing the DMA Controller

Channel 1

Handler

Channel 2

Handler

Channel 3

Handler

Channel 4

Handler

PRIORITIZER

BUS MANAGER

BUS INTERFACE

DMA

req

DMA

ack

DMA

req

DMA

ack

DMA

req

DMA

ack

DMA

req

DMA

ack

DMARQN

A[0:15]

RDWN

Double

RDYN

Cascaded

request

out (REQN)

Bus grantn

(GRANTN)

Grant enable

out (GEOUTN

Cascaded grant

enable in

(GEINN)

MA31753

3/30

3.0 DMA FUNCTIONALITY

Figure 2 shows a block diagram representing the structure

of the DMA controller. This figure also shows how the DMA

interfaces with the rest of the system.

Each DMA channel has 6 possible modes that it can

operate in. These are as follows:

3.1 IDLE MODE

The channel goes into IDLE mode after an active hardware

reset or after resetting the status flags. When in IDLE mode,

the channel goes into PEND_CHAIN mode when activated by

writing the Mode register. No parity check is done on this

register write.

3.2 PEND_CHAIN MODE

Once the channel has been activated, it goes from IDLE to

PEND_CHAIN mode. In this mode, the first instruction is read

(all 8 words). If a parity error is detected, the channel goes to

the ERROR mode. If the read is successful, the channel will

stay in the PEND_CHAIN mode until either an active request is

received or the Channel Request Pending bit is set in the

Channel Status Register. At this time, the channel progresses

to the PEND_REQ mode.

3.3 PEND_REQ MODE

In this mode, the Mode / Link word is checked to make sure

it doesn’t de-activate the channel (sending the device back to

IDLE mode). If the channel remains active, the device sits in

PEND_REQ mode until the system bus arbiter grants the DMA

bus control. Once this occurs, the transfer commences and the

DMA enters TRANSFER mode.

3.4 TRANSFER MODE

If at any time during the transfer an error occurs, the

channel is set into ERROR mode. If the transfers are clean of

errors, then the behaviour of the device is dependant on the

type of transfer mode that was programmed by the currently

executing instruction.

3.4.1 Single/Double Word and External Area to Area Mode

Within these modes, the DMA executes each data transfer

seperately, ie. between each single / double word transfer, the

request is removed. The DMA goes back into PEND_REQ

mode after each transfer and waits for the next request to be

granted.

3.4.2 Burst Area to Area Mode

With this type of transfer, the DMA transfers data whilst the

bus control is granted. The channel request signal remains

active. When control is removed by the arbiter, the device sits

in the PEND_TRANS mode until re-granted. If the burst mode

is area to area with interval timing, then between each transfer,

the channel has to count the interval.

Once a transfer has completed, the channel either sets the

EOT bit and sits waiting for this to be reset before it goes back

into INIT mode, or the instruction is chained and the channel

jumps back to the PEND_CHAIN mode where it can read the

next instruction details for the next transfer. If during any

transfer mode, the channel is de-activated, the channel goes

back to INIT mode. If at any time, an error is detected, the

device goes into ERROR mode.

3.5 ERROR MODE

This mode is entered from the PEND_CHAIN mode if a

parity error is detected during the instruction register reads.

The error mode can also be entered from theTRANSFER

mode. This can happen if PEN, MPROEN or EXADEN are

activated by trying to access one of the data transfer addreses.

An interrupt is generated in this mode. The only way to leave

this mode is to reset all the error flags.

3.6 WORD TRANSFER MODES

It is possible to run each channel in single, double, and

burst mode transfers.

3.6.1 Single Word Transfer

In single word transfer mode, the generation of each

request on a channel causes the DMA controller to issue an

external request that lasts for one bus cycle. The request is de-

activated before the end of the bus cycle to allow other users to

aquire bus control. If the transfer is to or from a device needing

longer than one machine cycle (2 CLK cycles) then the cycle

can be extended using handshaking of the DMA request and

acknowledge lines.

3.6.2 Double Word Transfer

In double word mode, each request on a channel causes

the DMA controller to request bus control for 2 machine cycles

to allow the transfer of 2 16-bit data words. The data is

transferred to consecutive addresses and the bus is locked

between each word transfer to protect the transfer. The most

significant word to be transferred has the lowest address and

is transferred first (following the 1750 standard). The request is

de-activated before the end of the second bus cycle to allow

other bus users to take control. If an extended cycle is needed,

the handshaking mechanism doesn’t word in this mode and

the RDYN signal must be kept high for as long as required.

3.6.3 Burst Mode

In burst mode, one request to the channel causes the DMA

to request bus control for a complete block of data to be

transferred. The DMA de-asserts the request line on the last

transfer cycle to allow other users to take bus control.

Consequently, if the transfers are chained together, the CPU

may be able to get bus control between 2 blocks of data

transfer. If extended bus cycles are needed, the RDYN

mechanism can be used (handshaking does not work in this

mode).

MA31753

4/30

3.6.4 Area to Area Mode

In area to area mode, the transfers can be initiated either

by external requests or internally generated by the DMA

depending on the value in the interval timer (the software

generated requests controlleed by the interval timer can only

be used on channels 0 and 1). Each request makes the DMA

request bus control for 2 machine cycles. The transfers can

take place to and from IO and / or memory depending on how

the instruction programs the channel. The DMA de-asserts the

request during the second cycle unless the instruction has

programmed the channel to do “Continuous Internal Request”.

In this case, the request is only de-asserted on the last cycle of

the block. If extended bus cycles are needed, the RDYN

mechanism must be used as the handshaking does not work in

this mode.

3.6.5 Instruction Chaining

When the first request is received on a channel, it

accesses the DMA instruction number that is programmed in

the mode word. This instruction is read from internal DMA

RAM. This takes 16 CLK cycles (as there are 8 16-bit word in

the instruction). Bus control is not needed during these internal

RAM accesses. At the end of the 16 CLK cycles, the channel

has all the transfer information it needs and can begin to

transfer whenever it is granted bus control. Once the transfer

has completed, the channel checks that it is in chaining mode

and that the instruction is a chained instruction. If so, then as

the first instruction completes, the DMA can access the next

instruction (again taking 16 CLK cycles) and the transfers can

continue as bus control is granted.

3.6.6 Handshaking Mechanism

There is a handshaking mechanism available when using

single-word transfer mode. It works as follows:

For a memory read cycle:

1: The IO port issues a request.

2: The DMA requests and is granted bus control. The DMA

starts a memory read cycle. As well as the usual control

and strobes, the DMA also asserts the DACKN low for the

channel that it is responding to. The DACKN signal acts as

an IO port select.

3: Once valid data is available on the data bus ie. RDYN has

gone low, the DMA asserts AKWRN low. The IO port uses

AKWRN as a write strobe.

4: The IO port acknowledges the completed data read by de-

asserting DREQN.

5: When the DMA sees DREQN has gone high, it de-asserts

DACKN. At this time, the data is still valid and the IO port

may latch the data on AKWRN rising or any time in

between.

6: The DMA completes the cycle by de-asserting strobes etc.

7: The wait state generator finally de-asserts RDYN.

For a memory write cycle:

1: The IO port issues a request.

2: The DMA aquires bus control and starts a memory write

cycle, also asserting DACKN for the relevant channel.

3: The data bus is driven by the IO port. Valid data is

available when the IO port de-asserts DREQN. (DACKN is

still asserted so valid data must still be driven on the bus).

4: When the DMA senses DREQN high, it writes the valid

data from the IO port into memory.

5: The memory write is completed when RDYN goes low.

6: The DMA de-asserts DACKN and hence the IO port stops

driving the data bus.

If DREQN is de-asserted 2 or more CLK cycles before

AKRDN or AKWRN are asserted, then the handshaking

protocol does not apply and the cycle will simply use the RDYN

signal going low to terminate the cycle (both AKRDN and

AKWRN will rise as AS falls at the end of the cycle).

3.7 INTERRUPT GENERATION

The DMA shall generate an interrupt on the occurrance of

any of the following:

- A channel has reached an “End of Transfer” condition and

the EOT bit has been set in the channel status register.

- A channel has been stopped because

a) a bus timeout has occurred. (ie. either DREQN

(handshake mode) or RDYN is asserted for more than

256 CLK cycles)

b) an internal parity error was detected when reading a

DMA register with parity.

c) An odd block length was programmed in double word

mode.

The DMA will stop but will not generate an interrupt if

EXADEN, MPROEN or PEN are active at the end of an

external cycle.

If a parity error is detected whilst writing to the DMA

registers, the erroneous write will not let transfers commence.

The DMA generates interrupts by pulsing INTRN low. If more

than one error occurs simultaneously, INTRN is only pulsed

once. The interrupt can only be generated when the DMA is in

the ERROR mode. The only way to get out of this mode is to

reset all error flags.

3.8 CHANNEL MASKING AND STOPPING

Each channel can be masked individually by setting the

relevant bit in the DMA Mode / Status register. If the channel is

masked, only external requests are gated out - software

requests are still serviced.

Each channel can be stopped by de-activating the channel

by writing the Channel Mode register. This register can only be

written whilst in PEND_CHAIN mode or awaiting bus control.

Once the channel is de-activated, it returns to the IDLE mode.

3.9 PARITY CHECKING

Parity checks are done when DMA registers are being

written and when they are being accessed ie. when the

instructions are being read.

MA31753

5/30

3.10 SOFTWARE PROGRAMMING

DMA requests can be generated in software by writing the

CRQP bit in the Channel Status register. If the channel is

active, the DMA will then request bus control. If the DREQN

signal on that channel is not active, the DMA finishes the cycle

as soon as the memory is ready. There is no handshaking with

the IO port. DACKN is deasserted when the memory is ready.

If DREQN is asserted but is masked, the handshaking is active

and operates normally.

Interrupts can be generated in software by setting either a

channel EOT flag or any error flag. This can only be done

when the DMA is in PEND_CHAIN mode. If an error flag is set,

the device goes straight to ERROR mode. If the EOT flag is

set, the device looks as if it has completed the transfer. It will

then just sit and wait for the EOT flag to be cleared before

entering IDLE mode. If both flags are set simultaneously, the

device remains in PEND_CHAIN mode. Setting an error flag

when EOT is set resets EOT and the device goes to ERROR

mode. Setting EOT when an error flag is set clears the error

and the DMA sits in the finish transfer mode.

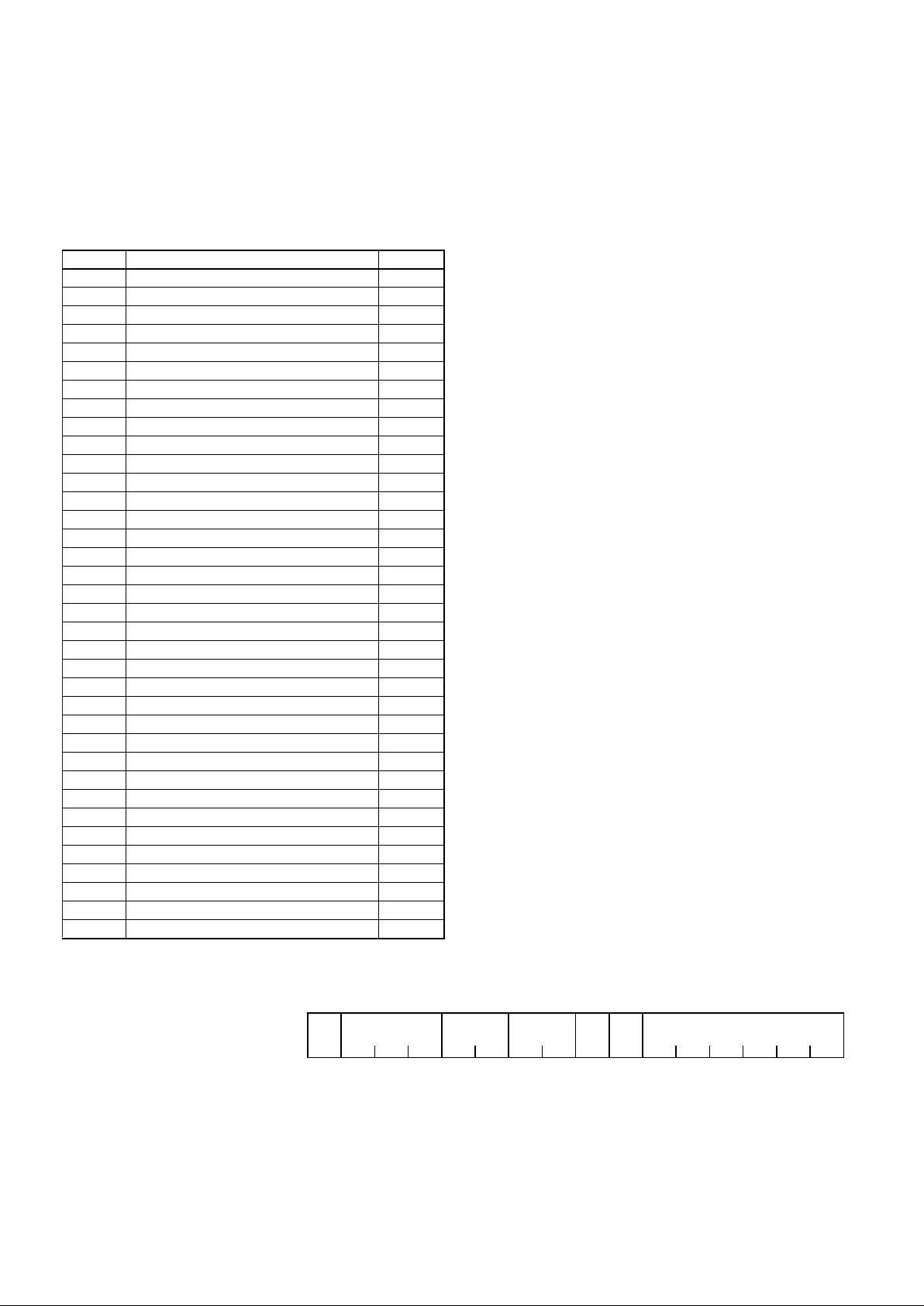

3.11 CASCADING DMA CONTROLLERS

DMA controllers are cascaded in series. For each DMA

added, an extra 4 channels become available. To cascade the

devices, the strobes, control signals and address and data

busses are connected in parallel. Of the bus arbitration

signals, LOCKN and GRANTN should be connected in parallel

and REQINN, GEINN and GEOUTN shoudl be daisy-chained.

INTRN and PEN can either be ORed together with external

glue logic or input to seperate CPU interrupts. Figure 3 shows

the cascade connections.

Figure 3: Cascading DMA Controllers

Bus

Arbiter

DMAC 1 DMAC 2

REQN

REQN

REQINN

GEOUTN

GEINN

DREQN[0:3]

DACKN[0:3]

Bus Interface Signals

DREQN[0:3]

DACKN[0:3]

Bus Interface Signals

GRANTN

44

4

4

MA31753

6/30

4.0 DETAILED REGISTER DESCRIPTION

The internal registers on the DMA controller can be located

in either memory or IO addressing space. 32 words are control

registers and 480 words are the DMA instruction registers.

The address lines A[7:15] are used to decode the registers.

(A[0:6] are decoded to generate CSN low ie. the user can

place the DMA on the address map.)

4.1 MODE REGISTERS

CA read 0: channel not active

write 0: stop channel

read 1: channel active

write 1: start channel

This bit will be set low at an error or EOT condition

Mode 000: Single Word

001: Double Word

010: Burst Mode

011: Not used (channel not started)

100: Area to Area, Memory to Memory

101: Area to Area, Memory to IO

110: Area to Area, IO to Memory

111: Area to Area, IO to IO

A1M Area 1 Mode

For single, double and burst modes

00: Read from memory, incrementing address

01: Read from memory, decrementing address

10: Write to memory, incrementing address

11: Write to memory, decrementing address

Area to area mode

00: Area 1 address constant

01: Area 1 address incrementing

10: Area 1 address decrementing

11: Area 1 address constant

A2M Area 2 Mode (only used in area to area mode)

00: Area 2 address constant

01: Area 2 address incrementing

10: Area 2 address decrementing

11: Area 2 address constant

SEOT 0: Signal ‘End of Transfer’ at end of current block

only of C=0

1: Always signal ‘End of Transfer’ at end of

current block.

C read 0: Perform no chaining

read 1: Perform chaining using the value of “next

Instruction” field as pointer

write 0: Perform no chaining even if defined by current

DMA instruction

write 1: Perform chaining as defined by current

instruction

Next These 6 bits point to one of the 60 DMA instructions ie.

Inst the next instruction to be executed.

If the number is 3C, 3D, 3E or 3F, then the transfer will

stop with the current block (ie. no chaining)

A[7:15] Register Content Parity

0 DM A Instruction Yes

.. .

.. .

1DF DM A Instruction Yes

1E0 Channel 0 M ode No

1E1 Channel 0 R em aining w ords No

1E2 Channel 0 Area 1 current address No

1E3 Channel 0 Area 1 current PB/AS/PS No

1E4 Channel 0 Area 2 current address No

1E5 Channel 0 Area 2 current PB/AS/PS No

1E6 Channel 0 Status No

1E7 DM A M ode / Status 1 No

1E8 Channel 1 M ode No

1E9 Channel 1 R em aining w ords No

1EA Channel 1 Area 1 current address No

1EB Channel 1 Area 1 current PB/AS/PS No

1EC C hannel 1 Area 2 current address No

1ED C hannel 1 Area 2 current PB/AS/PS No

1EE Channel 1 Status No

1EF RESERVED No

1F0 Channel 2 Mode No

1F1 Channel 2 Rem aining w ords No

1F2 Channel 2 Area 1 current address No

1F3 Channel 2 Area 1 current PB/AS/PS No

1F4 Channel 2 Area 2 current address No

1F5 Channel 2 Area 2 current PB/AS/PS No

1F6 Channel 2 Status N o

1F7 RESERVED No

1F8 Channel 3 Mode No

1F9 Channel 3 Rem aining w ords No

1FA Channel 3 Area 1 current address No

1FB Channel 3 Area 1 current PB/AS/PS No

1FC Channel 3 Area 2 current address No

1FD Channel 3 Area 2 current PB/AS/PS No

1FE Channel 3 Status N o

1FF RESER VED No

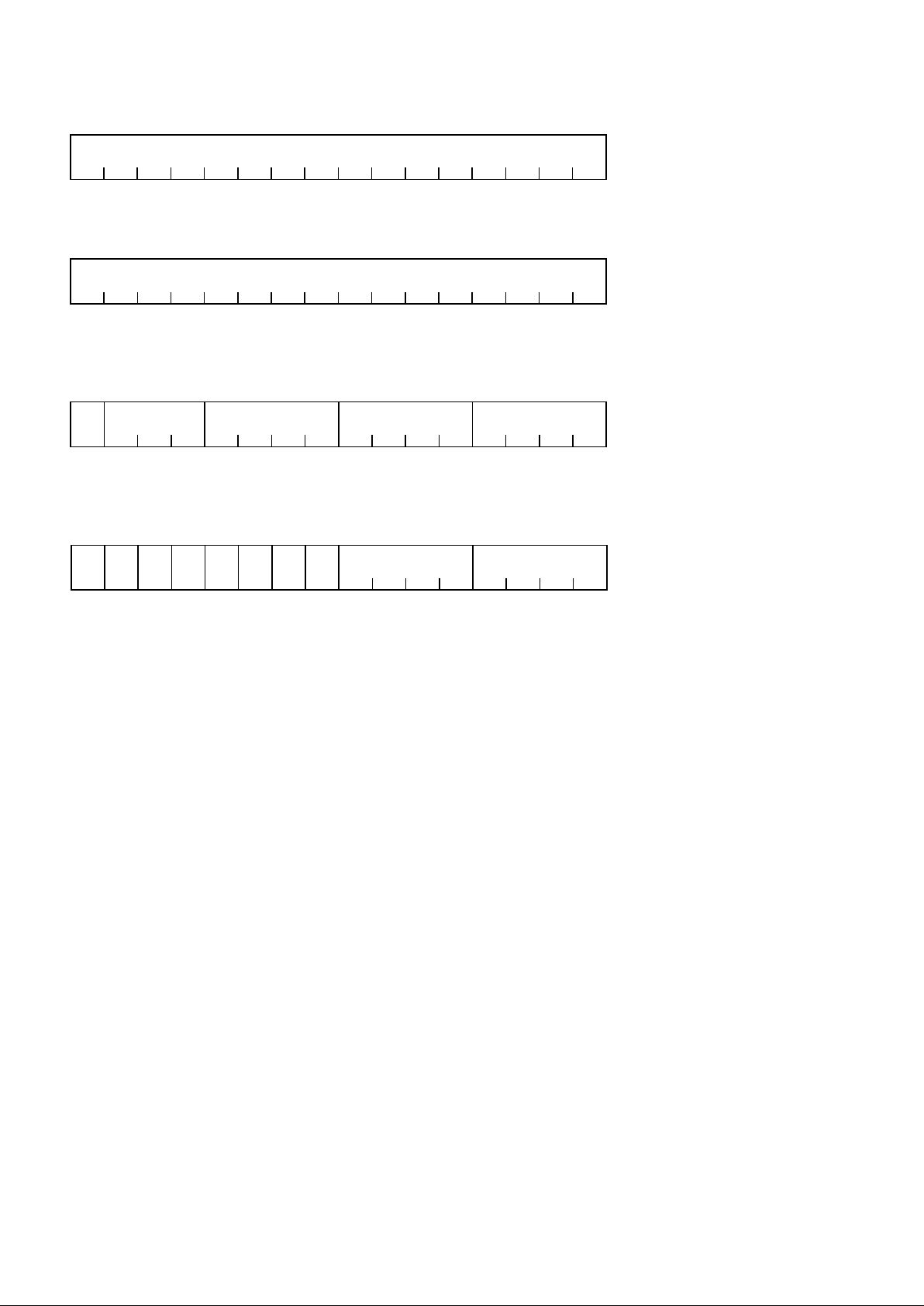

Mode Register

CA Mode A1M A2M SEOT C Next Instruction

D0 D15

MA31753

7/30

4.2 REMAINING WORD REGISTERS

Read access only. These 16-bit registers store the number of words left to be transferred for each area.

4.3 CURRENT ADDRESS REGISTERS

Read access only. These 16-bit registers store the addresses of the current words to be transferred to / from the area

represented by the register.

4.4 CURRENT PB / PS / AS REGISTER

Read access only. These 16-bit registers store the current page bank, address and process state information for each area.

When the areas have been selected within the IO space, PB, PS and AS shall be zero.

4.5 STATUS REGISTERS

CA 0: Channel not active

1: Channel active

This bit is automatically set to zero at an error or EOT condition.

EOT 0: Channel EOT not reached

1: Channel EOT reached.

CRQP 0: No channel DMA request pending.

1: Channel DMA request pending.

It is not possible to reset this bit as long as a DREQN line is asserted.

IPE 0: No internal parity error

1: Internal parity error when reading DMA register with parity.

BLE 0: No error

1: Block length error (odd block length in double word mode)

BIE 0: No error

1: Bus interface timeout error (caused either by not deasserting DREQN in handshake mode or by a bus timeout)

CLE 0: No error

1: CPU latched error (either MPROEN, EXADEN or PEN)

Interval The interval, in CLK cycles, between each DMA request generated during area to area transfers.

Current Block Counter

D0 D15

Current Address

D0 D15

OIN PB0 PB3 PS0 PS3 AS0 AS3

D0 D15

CA EOT CRQP IPE BLE BIE CLE

Interval

D0 D15

MA31753

8/30

4.6 DMA MODE / STATUS 1

Mn 0: Channel n not masked

1: Channel n masked

EOTn 0: Channel n “End of Transfer” not reached

1: Channel n “End of Transfer” reached

Read access only. Value can be changed by writing the channel status register.

ERR 0: No error detected

1: Error detected in one or more of the channels

Read access only. Value can be changed by writing the channel status register.

A / B 0: 1750A mode

1: 1750B mode

BP 0: Even bus parity used

1: Odd bus parity used

DMAE 0: DMA requests disabled

1: DMA requests enabled

Read access only

Pri 000: Channel priority 0, 1, 2, 3, C

001: Channel priority 1, 2, 3, 0, C

010: Channel priority 2, 3, 0, 1, C

011: Channel priority 3, 0, 1, 2, C

100: Channel priority C, 0, 1, 2, 3

101: Channel priority C, 1, 2, 3, 0

110: Channel priority C, 2, 3, 0, 1

111: Channel priority C, 3, 0, 1, 2

5.0 DMA INSTRUCTIONS

60 DMA instructions are present in the memory or IO space between A[7:15] = 0 and A[7:15] = 1DF. Each DMA instruction

comprises of 8 16-bit words. The base address for each instruction is 8*n where n is the instruction number. The instructions are

structured as below:

Words 4, 5 and 6 are used only during area to area mode transfers. Word 6 can only be used for channels 0 and 1.

M3

M2

M1

M0 EOT3 EOT2 EOT1 EOT0 ERR A/B BP DMAE Priority

D0 D15

Word number Content

0 Mode/Link word

1 Block length

2 Area 1 base address

3 Area 1 PB, PS and AS

4 Area 2 base address

5 Area 2 PB, PS and AS

6 Transfer interval

7 Not used

MA31753

9/30

5.1 MODE / LINK WORD

Mode 000: Single word

001: Double word

010: Burst mode

011: not used (channel not started)

100: Area to Area, Memory to Memory

101: Area to Area, Memory to IO

110: Area to Area, IO to Memory

111: Area to Area, IO to IO

A1M Area 1 Mode

For single, double and burst modes

00: Read from memory, incrementing address

01: Read from memory, decrementing address

10: Write to memory, incrementing address

11: Write to memory, decrementing address

Area to area mode

00: Area 1 address constant

01: Area 1 address incrementing

10: Area 1 address decrementing

11: Area 1 address constant

A2M Area 2 Mode (only used in area to area mode)

00: Area 2 address constant

01: Area 2 address incrementing

10: Area 2 address decrementing

11: Area 2 address constant

SEOT 0: Signal ‘End of Transfer’ at end of current block only of C=0

1: Always signal ‘End of Transfer’ at end of current block.

C read 0: Perform no chaining

read 1: Perform chaining using the value of “next Instruction” field as pointer

write 0: Perform no chaining even if defined by current DMA instruction

write 1: Perform chaining as defined by current instruction

Next These 6 bits give the number of the next instruction to be executed. If the number is 3C, 3D, 3E or 3F, then the DMA

Inst transfers will stop with the current block.

5.2 BLOCK LENGTH

This readable and writable 16-bit word gives the number of words to be transferred for the current DMA block.

5.3 AREA 1 AND 2 BASE ADDRESSES

These registers hold the addresses of the first word of memory or IO to be transferred (ie. when the channel is decrementing

the address, this register holds the highest address to be transferred.)

Mode A1M A2M SEOT C Next Instruction

D0 D15

Block Length

D0 D15

Base Address

D0 D15

Loading...

Loading...