DYNEX MAS17502LS, MAS17502LL, MAS17502LE, MAS17502LD, MAS17502LB Datasheet

...

MA17502

Radiation Hard MIL-STD-1750A Control Unit

Replaces June 1999 version, DS3565-4.0 |

DS3565-5.0 January 2000 |

The MA17502 Control Unit is a component of the MAS281 BLOCK DIAGRAM chip set. Other chips in the set include the MA17501 Execution

Unit and the MA17503 Interrupt Unit. Also available is the peripheral MA31751 Memory Management Unit/Block Protection Unit. In conjunction these chips implement the full MIL-STD-1750A Instruction Set Architecture.

The MA17502 consisting of a microsequencer, a microcode storage ROM, and an instruction mapping ROM - controls all chip set operations. Table 1 provides brief signal definitions.

The MA17502 is offered in several speed and screening grades, and in dual in-line, flatpack or leadless chip carrier packaging. Screening options are described in this document. For availability of speed grades, please contact Dynex Semiconductor.

FEATURES

■MIL-STD-1750A Instruction Set Architecture

■Full Performance Over Military Temperature Range

■12-Bit Microsequencer

-Instruction Prefetch

-Pipelined Operation

-Subroutine Capability

■On-Chip ROM

-2K x 40-Bit Microcode Store

-512 x 8-Bit Instruction Map

■MAS281 Integrated Built-In Self Test

■TTL Compatible System Interface

■Low Power CMOS/SOS Technology

1.0 SYSTEM CONSIDERATIONS

The MA17502 Control Unit (CU) is a component of the Dynex Semiconductor MAS281 chip set. The other chips in the set are the MA17501 Execution Unit (EU) and the MA17503 lnterrupt Unit (lU). Also available is the peripheral MA31751 Memory Management Unit/Block Protection Unit (MMU(BPU)). The Control Unit, in conjunction with these chips, implements the full MIL-STD-1750A lnstruction Set Architecture. Figure 1 depicts the relationship between the chip set components.

The CU provides the microprogram storage and sequencing resources for the chip set. The EU provides the MAS281’s system synchronizing and arithmetic/logic computational resources. The lU provides interrupt and fault handling resources, DMA interface control signals, and the three MIL-STD-1750A timers. The MMU/BPU may be configured to provide 1M-word memory management (MMU) and/or 1K-word memory block write protection (BPU) functions.

1/30

MA17502 |

|

|

|

|

|

|

|

|

Status |

8 |

|

|

|

|

|

|

|

Control |

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

Physical Page |

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

Address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock |

1 |

|

|

|

|

|

|

|

|

MA17501 |

|

|

|

|

|

|

|

Control |

|

|

|

|

|

|

|

|

10 |

Execution |

20 |

|

|

|

|

|

|

|

Unit |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Address/Data |

16 |

|

|

|

|

|

|

|

Bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Page |

|

|

|

|

|

|

|

|

RAM |

|

|

|

|

|

|

|

|

512 x 13 |

Control |

1 |

MA17502 |

|

M Bus |

|

|

|

|

|

Control |

|

|

|

|

|

||

|

|

20 |

|

|

|

|

||

|

|

Unit |

|

|

|

|

|

|

|

16 |

|

|

|

|

Data |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

Control |

|

|

|

|

|

|

Address |

|

10 |

|

|

16 |

MA31751 |

9 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Control |

|

|

Faults |

7 |

|

|

7 |

Block |

1 |

|

|

|

|

Protection |

|

|

||||

|

MA17503 |

3 |

|

Protection |

||||

Interrupts |

|

|

& Memory |

|

Data |

|||

|

Interrupt |

|

|

|

RAM |

|||

9 |

|

8 |

Management |

16 |

|

|||

|

Unit |

|

|

128 x 16 |

||||

|

|

|

|

Unit |

|

Address |

||

Timer |

|

|

|

|

|

|

||

4 |

|

3 |

3 |

|

7 |

|

|

|

Controls |

|

|

|

|

||||

|

|

|

|

|

|

Control |

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

4 |

|

1 |

|

|

Power |

4 |

|

|

|

|

|

|

|

|

|

|

MAS281 Chip Set |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1: MAS281 Chip Set With Optional MA17504 and Support RAMs

|

Signature |

l/O |

Definition |

||||||

|

|

|

|

||||||

|

AD00 - AD15 |

I |

External 16-Bit Address/Data Bus |

||||||

|

CC00 - CC11 |

I/O |

12-Bit Microcode Address Bus |

||||||

|

CLKPC |

|

|

I |

Precharge Clock |

||||

|

CLK02 |

|

|

I |

Phase 2 Clock |

||||

|

CS |

I |

Chip Select |

||||||

|

HOLD |

|

|

I |

Hold Request Suspends lnternal Processor Functions |

||||

|

IR |

|

|

|

I |

Interrupt Request |

|||

|

M00 - M19 |

I/O/Z |

20-Bit Microcode Bus |

||||||

|

NC |

- |

No Connection |

||||||

|

PIF |

|

|

I |

Privileged lnstruction Fault |

||||

|

RESET |

I |

Rest Indicates Device Initialization |

||||||

|

ROMONLY |

|

I |

Indicates if Control Unit to be Used as ROM Only |

|||||

|

T1 |

I |

Branch or Jump Control |

||||||

|

VDD |

|

Power (External), 5 Volts |

||||||

|

GND |

|

Ground |

||||||

|

|

|

|

|

|

|

|

|

|

Table 1: Signal Definitions

2/30

As shown in Figure 1, the MAS281 is the minimum processor configuration consisting of an Execution Unit, a Control Unit, and an Interrupt Unit. This configuration is capable of accessing a 64K-word address space. Addition of an MMU configured MA31751 allows access to a 1M-word address space. This can also be configured as a BPU to provide hardware support for 1K-word memory block write protection.

The CU, as with all components of the MAS281 chip set, is fabricated with CMOS/SOS process technology. Input and output buffers associated with signals external to the MAS281 are TTL compatible.

Detailed descriptions of the CU’s companion chips are provided in separate data sheets. Additional discussions on chip set system considerations, interconnection details, and the Digital Avionics lnstruction Set (DAlS) mix benchmarking analysis are provided in separate applications notes.

2.0 ARCHITECTURE

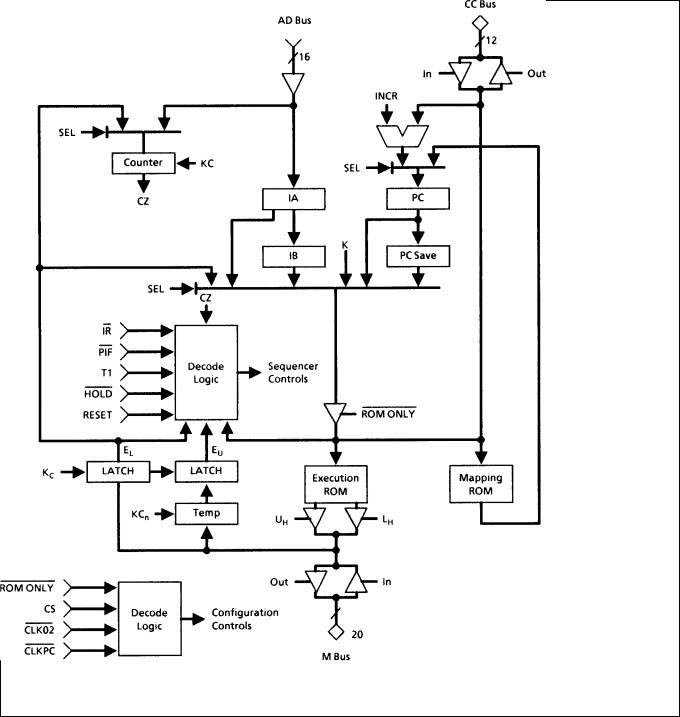

The Control Unit consists of a microsequencer, an instruction mapping ROM, a microcode storage ROM, and various buses. Details of these components are shown in Figure 2 and are discussed below:

2.1MICROSEQUENCER

The CU microsequencer is a 12-bit wide microcode address

generator. Major features of the microsequencer include a microprogram counter (PC), a microprogram counter save register (PC Save), microcode address increment logic, instruction pipeline registers IA and IB, an iteration of loop counter, a next microcode address source multiplexer, and various pipelining latches. These features are represented in Figure 2.

The 12-bit microcode address width allows the microsequencer to access up to 4096 words of microcode. The MIL-STD-1750A instructions are implemented as sequences of microinstructions stored within the lower 2048 locations of this address space. The address for each microinstruction in a sequence is provided by the next microcode address source multiplexer. This multiplexer, under control of the CU control logic, select from one of six next address sources. Sequential, direct jump, conditional jump, and subroutine address generation modes are supported.

Sequential addressing is accomplished by providing a path from the output of the next microcode address multiplexer to an incrementer and back to the PC register input. Direct jumps are supported by routing a portion of the microinstruction to one of the next microcode address source multiplexer inputs. Conditional jumps are determined in the ALU of the Execution Unit which communicates the decision to the CU via the T1 signal. The T1 signal enables a portion of the microcode word to create the new address. Subroutine jumps are accomplished by loading the contents of the incremented PC register into the PC Save register and then performing a direct jump. Upon completion of the subroutine, the contents of the PC Save register are used as the next microcode address.

A new microinstruction sequence begins when an opcode residing in the lA or IB register is selected by the next microcode address source multiplexer and used as an address to simultaneously access both the CU’s Instruction Mapping

MA17502

ROM and the Microcode Storage ROM. The instruction Mapping ROM access provides a pointer which is then used to update the microprogram counter (PC); the Microcode Storage ROM access provides the first microinstruction of the sequence. Remaining microinstructions in a sequence are accessed through the use of the four address generation modes discussed above.

Iterative microprogram operations are achieved through the use of the loop counter. The loop counter may be selectively loaded from either the AD bus or directly from microcode. This counter tracks the number of iterations remaining and, when appropriate, issues a completion signal (CZ). When an iterative operation is called for, the loop counter is loaded and the CU control logic repeats a particular microinstruction sequence, using the four address generation modes discussed above, until the CZ signal is received.

2.2 INSTRUCTION MAPPING ROM

The CU instruction mapping ROM provides 512 8-bit words of microcode instruction vector storage. The address space of this ROM is mapped into a portion of the microcode storage ROM’s address space. Hence, both ROMs are accessed whenever the microcode address falls within this range. The eight bits from the instruction mapping ROM serve as-the lower eight bits of a 12-bit microcode address; the upper four bits are a hardwired constant. The 12-bit microcode address formed from the 4-bit constant and the mapping ROM’s eight bits are loaded into the PC register of the microsequencer and serve as a means to access nonsequential microcode addresses within the address space allocated to both the instruction mapping and microcode storage ROMs.

2.3MICROCODE ROM

The CU microcode ROM provides 2K (2048) 40-bit words of

storage capacity. All of the microcode required to implement the full MIL-STD-1750A lnstruction Set Architecture (lSA) fits in one such ROM.

2.4BUSES

A 16-bit multiplexed Address/Data (AD) bus provides a

communications path between the CU, the other components of the MAS281 chip set, the MA31751 MMU/BPU, and any other devices mapped into the chip set’s address space. The CU receives MIL-STD-1750A instructions, accessed from system memory, over this bus and loads them into its instruction pipeline registers.

A 20-bit multiplexed Microcode (M) bus provides a pathway between the CU chip and the microcode decode logic on all other chips which are under CU microcode control. The 40-bit wide microinstructions from the CU’s microcode ROM are multiplexed on chip as two 20-bit words and presented on the interchip M bus during alternate phases of CLK02N. Microcode bits 39 through 20 are placed on the M bus during the CLK02N low phase and bits 19 through 0 during the high phase of CLK02N. The M bus is bidirectional to permit microcode memory expansion.

A 12-bit microcode address (CC) bus is used to route microcode addresses from the next microcode address source multiplexer to the microcode and instruction mapping ROMs as shown in Figure 2.

3/30

MA17502

3.0 INTERFACE SIGNALS

All signal definitions are shown in Table 1. In addition, each of these functions is provided with Electrostatic Discharge (ESD) protection diodes. All unused inputs must be held to their inactive state via a connection to VDD or GND.

Throughout this data sheet, active low signals are denoted by either a bar over the signal name or by following the name with an “N” suffix. e.g. HOLDN. Referenced signals that are not found on the MA17502 are preceded by the originating chip’s functional acronym in parentheses, e.g. (IU)DMAKN.

A description of each pin function, grouped according to functional interface, follows. The function acronym is presented first, followed by its definition, its type, and its detailed description. Function type is either input, output, high impedance (Hi-Z), or a combination thereof. Timing characteristics of each of the functions described are provided in Section 6.0.

3.1 POWER INTERFACE

The power interface consists of a single 5V VDD connection and two common GND connections.

3.2CLOCKS

The clock interface, discussed below, is the means by

which the synchronous, microcoded operation of the MAS281 is driven.

3.2.1 Precharge Clock (CLKPCN)

Input. The MA17501 Execution Unit (EU), generates the CLKPCN signal for the Control Unit. The Control Unit uses this signal for most of its internal sequencing. During the low phase of CLKPCN, the internal M Bus is precharged to the high state to accelerate its response.

The normal CLKPCN period is defined by five OSC cycles (two cycles low and three cycles high). When a microcode branch is indicated by the EU, the low state of CLKPCN is extended to three OSC cycles. During execution of Interrupt Unit decoded XlO and microcode commands, the high state of CLKPCN is extended to four OSC cycles. Also, during external bus cycles, RDYN may be used to cause the EU to prolong the high state of CLKPCN to greater than three OSC cycles; this allows the MAS281 chip set to interface with slower external memory or input/output devices.

During DMA ((IU)DMAKN is low) or Hold ((EU)HLDAKN is low), CLKPCN will remain low until the CPU takes control again.

3.2.2 Phase 2 Clock (CLK02N)

Input. The MA17501 generates the CLK02N signal for the Control Unit. The CU then uses this signal, in conjunction with CLKPCN, to control the distribution of microcode on the M Bus. CLK02N is used to multiplex the 40-bit microcode instruction into two 20-bit words (μW1 and μW2). The high-to-low edge of CLK02N switches μW1 (bits 39 through 20) off the M Bus while switching μW2 (bits 19 through 0) onto the M Bus.

The normal CLK02N period is defined by five OSC cycles (one cycle low, three cycles high, one cycle low). When a microcode branch is indicated by the EU, the high state of CLK02N is extended to four cycles. During execution of Interrupt Unit decoded XIO and microcode commands, the trailing low state of CLK02N is extended to two OSC cycles.

Also, during external bus cycles, RDYN may be used to cause the EU to prolong the CLK02N trailing low state to greater than one OSC cycle; this allows the MAS281 chip set to interface with slower external memory or inpuVoutput devices.

During DMA ((IU)DMAKN is low) or Hold ((EU)HLDAKN is low), CLKPCN will remain low until the CPU takes control again.

3.3BUSES

The following is a discussion of the communication buses

connecting the three-chip set. The AD Bus and M Bus are mainly operand transfer buses, while the CC Bus is strictly for providing microcode addresses to auxiliary CUs.

3.3.1 Address/Data Bus (AD Bus)

Input. These signals comprise the multiplexed address and data bus. During external bus operations, the AD bus accommodates the transfer of instructions, from memory and l/O ports, to the MA17502. During internal bus operations, the AD bus provides additional data to the Control Unit from the Execution Unit. AD00 is the most significant bit position and AD15 is the least significant bit position of both the 16-bit data and 16-bit address. A high on this bus corresponds to a logic 1 and a low corresponds to a logic 0. lnformation on the AD Bus is clocked into the CU by the high-to-low transition of CLKPCN.

3.3.2 Microcode Bus (M Bus)

Input/Output/Hi-z. The M Bus is the 20-bit multiplexed microcode bus. The 40-bit microcode instruction is multiplexed onto the M Bus as two 20-bit words (μW1 and μW2). The first half of the microcode word, μW1 (bits 39 through 20), is assured valid on the high-to-low transition of CLK02N and μW2 (bits 19 through 0) is assured valid on the high-to-low transition of CLKPCN. M00 corresponds to microcode bit 0 (μW1) or 20 (μW2) while M19 corresponds to microcode bit 19 (μW1) or 39 (μW2). A high level indicates a logic 1 and a low level indicates a logic 0. A high level on CS allows the Control Unit to distribute microcode over this bus, a low level places the bus in the high impedance state.

During DMA or Hold states, CLKPCN is held low, thus holding the internal M bus in the precharged state. Precharging the internal M Bus forces the 20 bits of the external M Bus low.

3.3.3 Microcode Address Bus (CC Bus)

Input/Output/Hi-Z. The CC bus is provided for future expansion and is left unconnected.

3.4 SEQUENCER CONTROL

The following is a discussion of the microsequencer control input signals. These signals support chip set functions that require microcode branching based on the results of operations performed in the Execution or Interrupt Units.

3.4.1 Interrupt Request (IRN)

Input. A low on this input directs the CU to service pending interrupt requests latched by the Interrupt Unit (IU). Upon completion of the currently executing MIL-STD-1750A instruction, the CU checks the IRN input. If IRN is low, then the CU sequencer will branch to the microcoded interrupt service routine; else the next MIL-STD-1750A instruction is mapped to its microcode routine. The microcoded interrupt service routine

4/30

MA17502

Figure 2: MA17502 Control Unit Architecture

5/30

MA17502

stores the processor state, retrieves the highest priority pending interrupt’s service routine processor state, and vectors software execution to the user’s interrupt service routine. IRN originates in the IU.

3.4.2 Privileged Instruction Fault (PIFN)

A low on this signal causes the CU to enable control of the DMA interface (located in the Interrupt Unit), abort the currently executing MIL-STD-1750A instruction and check the IRN input for a pending level 1 interrupt caused by the IU latching a memory protect (MPROEN), memory address (EXADEN), or Bus Time-out fault. PIFN originates in the IU.

3.4.3 Branch or Jump Control (T1)

Input. A high on this input directs the CU microcode address sequencer to branch execution to a nonsequential microcode address. This signal is under the control of the Execution Unit’s ALU and its level is dependent on the outcome of the presently executing microcode instruction, e.g. conditional branch. T1 originates in the EU.

3.5CONFIGURATION CONTROL

The following inputs are provided for control of multiple CU

systems. They allow for expansion of the microcode store to 4K 40-bit words.

3.5.1 ROM-Only (ROMONLYN)

Input. This signal is provided for future microcode expansion and must be pulled up to VDD.

3.5.2 Chip Select (CS)

Input. A high on this signal enables the CU to drive the 20bit external M Bus. This signal is provided for future microcode expansion and must be pulled up to VDD.

3.6 CPU CONTROL

Grouped under this heading are signals that have CPUwide control of normal operation. Each of these has the ability to “freeze” the processor.

3.6.1 Hold Request (HOLDN)

Input. A low on this input will suspend internal processor functions at the end of the currently executing MlL-STD1750A instruction. When this signal becomes active, the CU completes the currently executing MIL-STD-1750A instruction, then branches to the Hold microcode routine and enters the Hold state. The CU will resume normal operation by refilling the instruction pipeline registers (IA and IB) upon release of HOLDN.

3.6.2 System Reset (RESET)

Input. A high on this input for a duration of at least one CLKPCN period will reset the MAS281 chip set by forcing the Control Unit to microcode address zero. The high-to-low transition of this input will cause the CU to begin executing the MAS281 initialisation sequence starting with the first instruction in microcode. Built-in Test (BIT) is performed as part of the initialisation sequence. At the conclusion of initialisation and successful execution of BIT, the MAS281 will be initialised as shown in Table 3.

4.0 OPERATING MODES

The following discussions detail the MAS281 chip set operating modes from the perspective of the Control Unit. MAS281 operating modes involving the MA17502 include: (1) Initialisation, (2) lnstruction Execution, (3) Interrupt Servicing,

(4) DMA Support, and (5) HOLD Support.

4.1INITIALISATION

The MA17502 sequences the MAS281 chip set through the

microcoded initialisation routine in response to a high pulse on the RESET input. This routine clears the chip set registers, disables and masks interrupts’ reads the configuration register, resets the output discrete register (if applicable), initialises the MMU and BPU (if applicable), performs Built-in Test (BIT), raises the StartUp ROM Enable discrete, clears and starts timers A and B, resets the Trigger-Go counter, and loads the instruction pipeline. The initialisation sequence is contained in the first 33 locations of microcode ROM (an additional 14 locations contain the optional MMU and BPU initialisation code). Because the initialisation sequence clears the Execution Unit’s lnstruction Counter and Status Word (also the address and processor state copies stored in the MMU(BPU), if applicable), program execution begins with the instruction located at address zero (page zero). Table 2 provides a detailed breakdown of the initialisation sequence and Table 3 summarises the resulting initialised state.

BIT occupies 332 words of microcode storage ROM, and consists of five subroutines that exercise the internal circuitry of the MAS281, as outlined in Table 4. BIT begins by pulling the Normal Power-UP ((IU)NPU) output low; this is the first time after power-up that the state of NPU is guaranteed. If all five BIT subroutines execute successfully, NPU is raised high.

If any part of BIT fails, an error code identifying the failed subroutine is loaded into the Interrupt Unit Fault Register (via the AD Bus), BlT is aborted, and NPU is left in the low state. Table 4 defines the coding of the BIT results. (NPU is raised high through microcode control of the lU in conjunction with the (EU)lNTREN signal. The BIT error codes are loaded in the lU Fault Register via the AD Bus under microcode control of the lU in conjunction with the (EU)lNTREN signal.)

ln the event of such a failure, the resulting chip set reset state is dependent on where in BIT the error occurred and may not be the same as that shown in Table 3. A BIT failure indication in the fault register sets the level 1 pending interrupt. Since initialisation disables and masks interrupts, the IRN input will remain high; thus the interrupt will not be serviced immediately.

The last action performed by the initialisation routine is to load the instruction pipeline. lnstruction fetches start at memory location zero (page zero) from the Start-Up ROM (if implemented). Whether BlT passes or not, the processor will begin instruction execution at this point.

Note: To complete initialisation and pass BIT, interrupt and fault inputs must be high for the duration of the initialisation routine. Also, the Timers A and B must be clocked for BIT success.

6/30

MA17502

Label |

Cycle |

|

|

MAIN |

B1 |

1. |

Enable Control of DMAE Output signal |

|

P |

2. |

- |

|

B1 |

3. |

Clear MAS281 Execution Unit Status Word (SW) |

|

|

|

Clear Interrupt Mask (MK) (Internal l/O command, SKM, 2000H) |

|

B1 |

4. |

Clear Pending lnterrupt Register (Pl) and Fault Register (FT) (lnternal l/O Command, CLlR, 2001H) |

|

|

|

Clear Instruction Counter (IC) |

|

P |

5. |

- |

|

B1 |

6. |

Disable Interrupts (Internal l/O Command, DSBL, 2003H) |

|

P |

7. |

- |

|

B1 |

8. |

Clear MMU Status Word (lnternal l/O Command, WSW, 200EH) (Note 1) |

|

P |

9. |

- |

|

B1 |

10. |

Disable DMA Access (Internal l/O Command, DMAD, 4007H) |

|

P |

11. |

- |

|

B1 |

12. |

Read Configuration Register (Internal l/O Command, RCW, 8400H, CONFWN Drops low per Figure |

|

|

|

25, Section 5.0) |

|

P |

13. |

- |

|

P |

14. |

- |

|

B2 |

15. |

- (If Output Discrete Register Present, then Continue; Else, Skip to 18) |

|

P |

(16). |

- |

|

I/O |

(17). |

Clear Output Discrete Register (External l/O Command) |

|

B2 |

19. |

- (If BPU present, then Branch to BPU; else, continue) |

|

P |

20. |

- |

|

B2 |

21. |

- (If MMU present, then Branch to MMU; Else, Continue) |

|

P |

22. |

- (Setup Temporary Register to indicate No MMU Present) |

|

B2 |

23. |

- (Branch to MAS281 BIT) |

|

P |

24. |

- |

|

B1 |

25. |

Enable Start-Up ROM (Internal l/O Command, ESUR, 4004H; SURE Raises High per Figure 25, |

|

|

|

Section 5.0) |

|

P |

26. |

- |

|

B1 |

27. |

Clear and Start Timer A (Internal l/O Command, OTA, 400AH) |

|

B1 |

28. |

Reset the Trigger-Go timer (Internal l/O Command, GO, 400BH) |

|

P |

29. |

- |

|

B1 |

30. |

Clear and Start Tlmer B (Internal l/O Command, OTB, 400EH) |

|

B2 |

31. |

- (Branch to Load Instruction Pipeline Routine) |

|

M |

32. |

Load data-ln register (Dl) and instruction Register A (IA) from [IC], Increment IC |

M33. Load Data-ln Register (Dl) and lnstruction Register a (lA) from [lC] ([lA] Moves to lB), lncrement lC Map Instruction Register B (IB) into Microcode Routine

BPU |

P |

(1). |

- |

|

P |

(2). |

- (Set Loop to Clear Memory Protect RAM) |

|

I/O |

(3). |

Clear a Location in MPRAM (Internal l/O Command, LMP, 50XXH), Increment Address; Do 128 Times |

|

|

(4). |

- (Branch Back to 20.) |

MMU |

P |

(1). |

- |

|

P |

(2). |

- |

|

P |

(3). |

- (Setup Loop to Load Instruction Page Registers (IPR) and Operand Page Registers (OPR) wlth |

|

|

|

Sequential Values of 0 to 255) |

|

P |

(4). |

- |

|

P |

(5). |

- |

|

I/O |

(6). |

Load a Location in the IPR with the value of the Locatron Address (Internal l/O Command, WIPR, |

|

|

|

51XYH) |

|

I/O |

(7). |

Load a Location in the OPR Increment Loaded Value with the Value of the Location Address (Internal |

|

|

|

I/O Command, WOPR, 52XYH) |

|

P |

(8). |

- (Increment IPR Address) |

|

P |

(9). |

- (Increment OPR Address - Repeat Loop [4. - 9.] 256 Times) |

|

B2 |

(10). |

- (Setup Temporary Register to Indicate MMU Present; Branch back to 23) |

Notes: 1. This operation Is performed whether or not an MMU is present.

2.“-” indicates internal CPU operation.

3.Sequence numbers in “( )” are performed only under the stated conditions.

4.Each step enumerated above represents a single machine (SYNC) cycle of the type shown in the “Cycle” column. “P” indicates a 5 OSC cycle, 60% duty cycle, machine cycle.

“I/O” and “M” indicate a 5 OSC cycle, 50% duty cycle, machine cycle. “B1” indicates a 6 OSC cycle 50% duty cycle machine cycle.

“B2” indicates a 6 OSC cycle 66% duty cycle machlne cycle.

Table 2: MAS281 Initialisation Sequence

7/30

MA17502

MAS281

Instruction Counter (IC) |

Zeroed |

Status Word (EU and MMU) (SW) |

Zeroed |

Fault (FT) |

Zeroed |

Pending Interrupt (Pl) |

Zeroed |

Mask (MK) |

Zeroed |

General Register File (RO R15) |

Zeroed |

Interrupts |

Disabled |

DMA Access |

Disabled |

TimerA |

Reset and Started |

Timer B |

Reset and Started |

Trigger-Go Timer |

Reset and Started |

|

|

MMU |

|

|

|

Page Registers |

Group Zero Enabled |

AL, W, E, Fields |

Zeroed |

PPA Field |

Logical to Physical |

|

Map |

|

|

BPU |

|

|

|

Write Protect |

Zeroed |

Global Memory Protect |

Enabled |

Table 3: Initialisation State

4.2 INSTRUCTION EXECUTION

The MIL-STD-1750A microcoded instruction subroutines are stored in 1255 locations of microcode storage ROM. The Control Unit receives instructions from memory, via the AD Bus, through the instruction pipeline registers lA and IB. When the previous instruction or special process (Interrupts or Hold) has been completed, the new instruction residing in register IB is selected by the next microcode address source multiplexer. A 4-bit hardwired constant, appended by the instruction opcode, is then used as the first address of a microcode sequence which distributes the required control to execute the instruction. The microsequencer generates the remaining microcode addresses necessary to complete the sequence as described in Section 2.0 of this data sheet entitled, “Architecture”.

Upon completion of the current instruction, the CU will accept the next instruction in the program unless an interrupt, DMA, or Hold request is received. The interrupt and Hold request share a common branch point in microcode. If an interrupt and Hold request are both pending at the conclusion of the MIL-STD-1750A instruction microcode routine, the Hold request has priority and is serviced first. Upon release of the Hold state, the first instruction will execute even if the interrupt is still pending; when this instruction is complete the interrupt will be serviced (assuming the HOLDN input has not been

BIT |

Test |

BIT Fail Codes |

Cycles |

|

Coverage |

(FT13, 14,15) |

|

|

Microcode Sequencer |

|

|

1 |

IB Register Control |

100 |

221 |

|

Barrel Shifter |

|

|

|

Byte Operations and |

|

|

|

Flags |

|

|

|

Temporary Registers |

|

|

|

(T0 - T7) |

|

|

2 |

Microcode Flags |

101 |

166 |

|

Multiply |

|

|

|

Divide |

|

|

|

Interrupt Unit |

|

|

3 |

MK, Pl, FT |

111 |

214 |

|

Enable/Disable |

|

|

|

Interrupts |

|

|

|

Status Word Control |

|

|

4 |

User Flags |

110 |

154 |

|

General Registers |

|

|

|

(R0 - R15) |

|

|

5 |

Timer A |

111 |

763 |

|

Timer B |

|

|

|

BIT Pass/Fail |

- |

26 |

|

Overhead |

|

|

|

|

|

|

Note: BIT pass is indicated by all zeros in FT bits 13, 14 and 15 |

|||

|

Table 4: Built In Test (BIT) Summary |

|

|

driven low during execution of this instruction). Interrupt, DMA, and Hold support are explained in more detail in following sections.

4.3 DIRECT MEMORY ACCESS

Direct Memory Access (DMA) is controlled by the Execution Unit (EU) in concert with the Interrupt Unit DMA interface. The CU supports DMA by suspending processor control upon completion of the current machine cycle. If DMA is enabled ((UI)DMAE signal, high) a DMA request ((IU)DMARN input, low) to the MAS281 causes the lU to acknowledge with DMAKN, low. When the EU receives the DMAKN (DMA Acknowledge) signal from the lU, the CU clocks are suspended (CLKPCN, low; CLK02N, high) halting the MAS281’s microcode sequencing. Microinstruction execution remains suspended until DMARN is removed. When DMARN is removed, microcode execution resumes where DMARN had interrupted it.

4.4 INTERRUPT HANDLING

Interrupts are handled by the interrupt Unit (IU) and communicated to the CU via the lRN input. The CU checks the status of the lRN (lnterrupt Request) signal after the completion of each MlL-STD-1750A microcode instruction sequence. lf the lRN signal is low, the CU initiates interrupt handling, otherwise the CU processes a new instruction.

8/30

IU interrupt handling is controlled by the CU through three microcode bits - M04, M05, and M06. Upon receipt of the IRN signal and after completion of the currently executing instruction, the CU branches to a microcoded interrupt handling routine. The microprogram sequence supplies microcoded control to the lU for reading the highest priority pending interrupt vector code, which also clears this pending interrupt.

Due to the similarity of interrupt and hold request handling by the CU, if a Hold and interrupt request are pending at the end of an instruction sequence the Hold has priority and will be serviced.

4.5HOLD SUPPORT

The CU accepts a Hold request in much the same way as

an interrupt request. After the completion of each MlL-STD- 1750A microcode instruction sequence, the CU checks the status of the HOLDN signal. If the HOLDN signal is low, a microcoded sequence suspends further internal processing functions; otherwise, the CU processes a new instruction or services interrupt requests (Hold requests have priority over interrupt requests).

The Control Unit responds to an active HOLDN signal, upon completion of the currently executing instruction, but branching to a microprogrammed sequence of instructions that suspends all internal operations. This sequence of microinstructions allows the processor to resume instruction execution at the point HOLDN was accepted when the CU regains control of the processor. The MAS281 remains in the Hold state until HOLDN is pulled high (if the Hold state was reached through the hardware interface, HOLDN) or HOLDN is pulsed low (if the Hold state was reached through software, BPT instruction). HOLDN should be synchronised to AS falling.

5.0 SOFTWARE CONSIDERATIONS

The MAS281 chip set implements the full MlL-STD-1750A instruction set. Table 6a gives a brief listing of this instruction set and provides performance data for each instruction. Table 6b provides a summary of the l/O commands implemented in MAS281 and MA31751 MMU/BPU hardware. A complete description of this instruction set is provided in MIL-STD-1705A (Notice 1). The register set available to the software programmer is depicted in Figure 3. A discussion of data types, addressing modes, and benchmarking considerations fol lows.

5.1 DATA TYPES

The MAS281 chip set supports 16-bit fixed-point single precision, 32-bit fixed-point double-precision, 32-bit floatingpoint, and 48-bit extended-precision floatingpoint data types. Figure 4 depicts the formats of these data types.

All numerical data is represented in two’s complement form. Floating-point numbers are represented by a fractional two’s complement mantissa with an 8-bit two’s complement exponent. The MAS281 expects all floating point operands to be normalised. If they are not normalised, the results from an instruction are not defined.

MA17502

Figure 3: Register Set Model

9/30

Loading...

Loading...