ST STM6717, STM6718, STM6719, STM6720, STM6777 User Manual

...

STM6717/6718/6719/6720

STM6777/6778/6779/6780

Dual/triple ultra-low voltage supervisors with push-button reset (with delay option)

Features

■Primary supply (VCC1) monitor.

Fixed (factory-programmed) reset thresholds:

4.63V to 1.58 V

■Secondary supply (VCC2) monitor (STM6717/18/19/20/77/78)

■Fixed (factory-programmed) reset thresholds:

3.08V to 0.79 V

■Tertiary supply monitor (using externally adjustable RSTIN): 0.626 V internal reference

■RST outputs (push-pull or open drain); state guaranteed if VCC1 or VCC2 ≥ 0.8 V

■Reset delay time (trec) on power-up: 13.2 ms, 210 ms, 900 ms (typ)

■Manual reset input (MR)

■Optional delayed manual reset input (MRC) with external capacitor (STM6777/78/79/80)

■Low supply current - 11 µA (typ), VCC1 = VCC2 = 3.6 V

■Operating temperature: –40 °C to 85 °C (industrial grade)

SOT23-5 (WY)

SOT23-6 (WB)

Table 1. |

Device summary |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Monitored voltages |

|

|

|

|

|

|

Reset output |

|

|

|

||||

Part |

Manual reset |

Delayed |

|

|

(RST) |

|

|||||||||

|

|

|

|

MR |

|

|

|

|

|

Package |

|||||

|

|

|

|

|

Active-low |

Active-low |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

number |

VCC1 |

VCC2 |

|

RSTIN |

input (MR) |

pin (MRC) |

|||||||||

|

|

||||||||||||||

|

|

|

|

|

|

|

|

(push-pull) |

(open drain) |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

STM6717 |

|

|

|

|

|

|

|

|

|

|

|

WY |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

STM6718 |

|

|

|

|

|

|

|

|

|

|

|

|

WY |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

STM6719 |

|

|

|

|

|

|

|

|

|

|

|

WB |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

STM6720 |

|

|

|

|

|

|

|

|

|

|

|

|

WB |

||

|

|

|

|

|

|

|

|

|

|

|

|||||

STM6777 |

|

|

|

|

|

|

|

|

|

WB |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

STM6778 |

|

|

|

|

|

|

|

|

|

|

WB |

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

STM6779 |

|

|

|

|

|

|

|

|

|

WB |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

STM6780 |

|

|

|

|

|

|

|

|

|

|

WB |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

August 2011 |

|

|

|

|

Doc ID 11469 Rev 8 |

|

|

|

|

1/30 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

www.st.com

Contents |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|

|

Contents

1 |

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

5 |

|

|

1.1 |

Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

7 |

1.1.1 Active-low, push-pull reset output (RST) - STM6718/20/78/80 . . . . . . . . 7 1.1.2 Active-low, open drain reset output (RST) - STM6717/19/77/79 . . . . . . . 7 1.1.3 Push-button reset input (MR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 1.1.4 Manual reset delay input (MRC) - STM6777/78/79/80) . . . . . . . . . . . . . . 8 1.1.5 Primary supply voltage monitoring input (VCC1) . . . . . . . . . . . . . . . . . . . 8 1.1.6 Secondary supply voltage monitoring input (VCC2) . . . . . . . . . . . . . . . . . 8 1.1.7 Adjustable reset comparator input (RSTIN; STM6719/20/79/80) . . . . . . 8

2 |

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

10 |

|

2.1 Applications information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

10 |

3 |

Typical operating characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

11 |

4 |

Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

17 |

5 |

DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

18 |

6 |

Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

22 |

7 |

Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

26 |

8 |

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

29 |

2/30 |

Doc ID 11469 Rev 8 |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

List of tables |

|

|

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2. Signal names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3. Pin functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table 4. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 5. Operating and AC measurement conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Table 6. DC and AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 7. tMLMH minimum pulse width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table 8. SOT23-5 – 5-lead small outline transistor package mechanical data. . . . . . . . . . . . . . . . . 23

Table 9. SOT23-6 – 6-lead small outline transistor package mechanical data. . . . . . . . . . . . . . . . . 24 Table 10. Carrier tape dimensions for SOT23-5L and SOT23-6L . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 11. Ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 12. Marking description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Table 13. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Doc ID 11469 Rev 8 |

3/30 |

List of figures |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|

|

List of figures

Figure 1. Logic diagram (STM6717/18) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 2. Logic diagram (STM6777/78) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3. Logic diagram (STM6719/20) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4. Logic diagram (STM6779/80) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 5. STM6717/18 SOT23-5 connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6. STM6777/78 SOT23-6 connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 7. STM6719/20 SOT23-6 connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 8. STM6779/80 SOT23-6 connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 9. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10. Hardware hookup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 11. STM67xx interface to processor with bi-directional reset pins . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12. Ensuring RST valid to VCC = 0 (active-low, push-pull outputs). . . . . . . . . . . . . . . . . . . . . . 10

Figure 13. Supply current vs. temperature (VCC1 = 5.5 V; VCC2 = 3.6 V) . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14. Supply current vs. temperature (VCC1 = 3.6 V; VCC2 = 2.75 V) . . . . . . . . . . . . . . . . . . . . . 11 Figure 15. Supply current vs. temperature (VCC1 = 3.0 V; VCC2 = 2.0 V) . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16. Supply current vs. temperature (VCC1 = 2.0 V; VCC2 = 1.0 V) . . . . . . . . . . . . . . . . . . . . . . 12 Figure 17. Normalized VCC reset time-out period vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 18. Maximum VCC transient duration vs. reset threshold overdrive . . . . . . . . . . . . . . . . . . . . . 13

Figure 19. Normalized VRST1 threshold vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 20. Normalized VRST2 threshold vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 21. Reset input threshold vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 22. VCC1-to-reset delay vs. temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 23. Reset input-to-reset output delay vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 24. MR-to-reset output delay vs. temperature (VCC1 = 3.6V) . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 25. AC testing input/output waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 26. MR timing waveform (STM6717/18/19/20) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 27. MR timing waveform (STM6777/78/79/80) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 28. SOT23-5 – 5-lead small outline transistor package mechanical drawing . . . . . . . . . . . . . . 23 Figure 29. SOT23-6 – 6-lead small outline transistor package mechanical drawing . . . . . . . . . . . . . . 24 Figure 30. Carrier tape for SOT23-5L and SOT23-6L . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4/30 |

Doc ID 11469 Rev 8 |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

Description |

|

|

1 Description

The STM6717/18/19/20 and STM6777/78/79/80 supervisors are a family of low-voltage/low- supply current processor (micro or DSP) supervisors, designed to monitor two (or three) system power supply voltages. They are targeted at applications such as set-top boxes (STBs), portable, battery-powered systems, networking, and communication systems.

All device options have a push-button-type manual reset input (MR). The STM6777/78/79/80 also includes an option which enables the user to delay the start of the manual reset process from 6 µs (MRC pin left open) or more with external capacitor. The delay is implemented by connecting the appropriately sized capacitor between the MRC pin and VSS (typical 4 s delay with a 3.3 µF capacitor, see Table 7 on page 21).

Two of the three supplies monitored (VCC1 and VCC2) have fixed (customer-selectable, factory-trimmed) thresholds (VRST1 and VRST2). The third voltage is monitored using an externally adjustable RSTIN threshold (0.626 V internal reference).

If any of the three monitored voltages drop below its factory-trimmed or adjustable thresholds, or if MR is asserted to logic low, a RST is asserted (driven low). Once asserted, RST is maintained at low for a minimum delay period (trec) after ALL supplies rise above

their respective thresholds and MR returns to high. These devices are guaranteed to be in the correct reset output logic state when VCC1 and/or VCC2 is greater than 0.8 V.

These devices are available in standard 5-pin or 6-pin SOT23 packages (see Table 1 on page 1).

Doc ID 11469 Rev 8 |

5/30 |

Description |

|

|

|

|

|

|

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

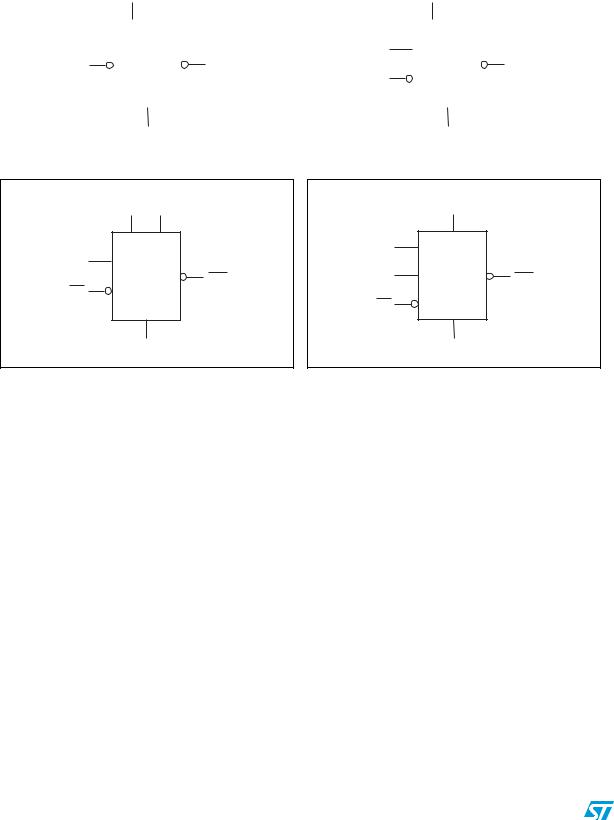

Figure 1. Logic diagram (STM6717/18) |

|

Figure 2. Logic diagram (STM6777/78) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC2 |

VCC1 |

|

|

|

|

|

|

|

VCC2 VCC1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

MRC |

|

|

|

|

|

|

||

|

|

|

STM6717 |

|

|

|

|

STM6777 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

MR |

RST |

RST |

|

|||||||||||||||

STM6718 |

|

|

|

|

STM6778 |

|

||||||||||||

|

|

|

|

|

|

|

MR |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

VSS |

|

|

|

|

|||

|

|

|

|

|

|

|

|

AI10413 |

|

|

|

|

|

|

|

|

AI10415 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 3. Logic diagram (STM6719/20)

VCC2 VCC1

RSTIN

STM6719

STM6720 RST

MR

VSS

AI10414

Figure 4. Logic diagram (STM6779/80)

VCC

RSTIN |

|

|

|

MRC |

STM6779 |

RST |

|

STM6780 |

|||

|

|||

|

|

||

MR |

|

|

|

|

VSS |

|

AI10416

Table 2. |

Signal names |

|||||

|

|

|

|

|

|

Push-button reset input |

|

|

MR |

||||

|

|

|

||||

MRC |

|

Manual reset delay input |

||||

|

|

|

|

|

||

|

|

|

|

|

|

Active-low reset output |

|

RST |

|||||

|

|

|

||||

VCC1 |

|

Primary supply voltage input |

||||

VCC2 |

|

Secondary supply voltage input |

||||

RSTIN |

|

Adjustable reset comparator input |

||||

|

|

|

|

|||

|

VSS |

|

Ground |

|||

6/30 |

Doc ID 11469 Rev 8 |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|

|

|

|

|

|

|

|

|

|

|

|

Description |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Figure 5. STM6717/18 SOT23-5 connections |

Figure 6. |

|

|

|

STM6777/78 SOT23-6 connections |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC1 |

|

|

|

|

|

|

|

1 |

5 |

|

VCC1 |

|

|

|

RST |

|

1 |

6 |

|

|

||||||||

|

RST |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||

|

VSS |

2 |

|

|

|

|

|

|

VSS |

2 |

5 |

|

|

MRC |

|

|||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

4 |

|

VCC2 |

|

|

|

|

|

MR |

|

|

3 |

4 |

|

|

VCC2 |

|

||

|

|

MR |

|

|

3 |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

AI10417 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AI10418 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Figure 7. STM6719/20 SOT23-6 connections |

Figure 8. |

|

|

|

STM6779/80 SOT23-6 connections |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

VCC1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC1 |

|

|

RST |

|

1 |

6 |

|

|

|

RST |

|

1 |

6 |

|

|

|||||||||||||

|

|

|

|

|||||||||||||||||||||||

|

VSS |

2 |

5 |

|

RSTIN |

|

|

|

VSS |

2 |

5 |

|

|

RSTIN |

|

|||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

MR |

|

|

3 |

4 |

|

VCC2 |

|

|

|

|

MR |

|

|

3 |

4 |

|

|

MRC |

|

|||||

|

|

|

|

|

|

|

|

|

|

AI10419 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AI10420 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.1Pin descriptions

1.1.1Active-low, push-pull reset output (RST) - STM6718/20/78/80

The RST pin is driven low and stays low whenever VCC1 or VCC2 or RSTIN falls below its factory-trimmed or adjustable reset threshold or when MR goes to logic low. It remains low

for trec after ALL supply voltages being monitored rise above their reset thresholds and MR goes from low to high. (Push-pull outputs are referenced to VCC1.)

1.1.2Active-low, open drain reset output (RST) - STM6717/19/77/79

The RST pin is driven low and stays low whenever VCC1 or VCC2 or RSTIN falls below its factory-trimmed or adjustable reset threshold or when MR goes to logic low. It remains low

for trec after ALL supply voltages being monitored rise above their reset thresholds and MR goes from low to high. Connect an external pull-up resistor to VCC1. A 10 kΩ pull-up resistor should be sufficient for most applications.

1.1.3Push-button reset input (MR)

When MR goes low the RST output is driven low. RST remains low as long as MR is low and for trec after MR returns to high. This active-low input has an internal 50 kΩ pull-up resistor to

Doc ID 11469 Rev 8 |

7/30 |

Description |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|

|

VCC1. It can be driven from a TTL or CMOS logic line, or with open drain/collector outputs, or connected to VSS through a switch. If unused, leave this pin open or connect it to VCC1.

Connect a normally open momentary switch from MR to VSS; external debounce circuitry is

not required. (If MR is driven from long cables or if the device is used in noisy environments, connecting a 0.1µF capacitor from MR to VSS provides additional noise immunity.

1.1.4Manual reset delay input (MRC) - STM6777/78/79/80)

This pin is either left open or connected to VSS via a capacitor. By selecting the appropriate capacitor, the manual reset process, initiated by pressing the push-button manual reset input, can be delayed by any value from 6 µs or more (see Table 7 on page 21).

1.1.5Primary supply voltage monitoring input (VCC1)

It also is the input for the primary reset threshold monitor. Available fixed (customerselectable, factory-programmed) reset thresholds include 4.63 V to 1.58 V.

1.1.6Secondary supply voltage monitoring input (VCC2)

This function is available on the STM6717/18/19/20/77/78. Fixed (customer-selectable, factory-programmed) reset thresholds include 3.08 V to 0.79 V.

1.1.7Adjustable reset comparator input (RSTIN; STM6719/20/79/80)

This is a high impedance input. RST is driven low when the voltage at the RSTIN pin falls below 0.626 V (internal reference voltage at this comparator). The monitored voltage reset threshold is set with an external resistor-divider network.

Table 3. |

Pin functions |

|

|

|

|

|

|

|

||

|

Pin |

|

|

|

|

|

|

|

||

|

|

|

|

Name |

Function |

|||||

STM6717 |

STM6719 |

STM6777 |

STM6779 |

|||||||

|

|

|

|

|

|

|||||

STM6718 |

STM6720 |

STM6778 |

STM6780 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

Active-low reset output |

|

|

RST |

|||||||||

|

|

|

|

|

|

|

|

|

||

3 |

3 |

3 |

3 |

|

|

|

|

Push-button reset input |

||

|

|

MR |

||||||||

|

|

|

|

|

|

|||||

— |

— |

5 |

4 |

MRC |

Manual reset delay input |

|||||

|

|

|

|

|

|

|||||

5 |

6 |

6 |

6 |

VCC1 |

Primary supply voltage input |

|||||

4 |

4 |

4 |

— |

VCC2 |

Secondary supply voltage input |

|||||

— |

5 |

— |

5 |

RSTIN |

Adjustable reset comparator input |

|||||

|

|

|

|

|

|

|

||||

2 |

2 |

2 |

2 |

|

VSS |

Ground |

||||

8/30 |

Doc ID 11469 Rev 8 |

STM6717/6718/6719/6720/STM6777/6778/6779/6780 |

|

|

|

|

|

|

|

|

|

|

|

Description |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

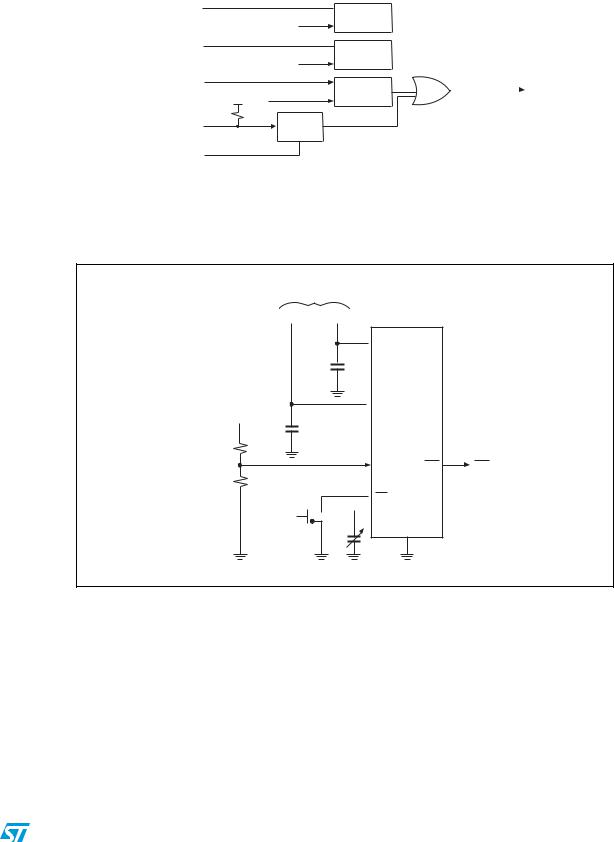

Figure 9. Block diagram |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

VCC1 |

|

VRST1 |

COMPARE |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

(1) |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

VCC2 |

|

VRST2 |

COMPARE |

|

|

|

|

|

|

|

|

|

|

|

|||

|

RSTIN(2) |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

trec |

|

|

|

|

||||

|

VREF/2 = 0.626 |

|

|

|

|

|

|

|

|

|

RST |

|||||||

|

|

|

V |

CC1 |

COMPARE |

Generator |

|

|

|

|

||||||||

|

|

|

|

|

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

MR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MRC(3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AI10421 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.VCC2 input is available on STM6717/18/19/20/77/78.

2.RSTIN available only on STM6719/20/79/80.

3.MRC available only on STM6777/78/79/80.

Figure 10. Hardware hookup

From DC/DC Converter

VCC2(1) VCC1

VCC1

VCC1

VCC3 = (626.5mV)(R1R2+ R2) |

0.1µF |

STM67xx

VCC2

VCC2

VCC3

0.1µF

R1

RSTIN(2) RST |

RST (To Processor Reset) |

R2

MR

MR

Push-button

MRC(3)

MRC(3)

Switch

VSS

C

AI10422

1.VCC2 is available only on STM6717/18/19/20/77/78.

2.RSTIN available only on STM6719/20/79/80.

3.MRC available only on STM6777/78/79/80.

Doc ID 11469 Rev 8 |

9/30 |

Loading...

Loading...