ST TSV622, TSV623, TSV624, TSV625, TSV622A User Manual

...

TSV62x, TSV62xA

Rail-to-rail input/output 29 µA 420 kHz CMOS operational amplifiers

Features

■Rail-to-rail input and output

■Low power consumption: 29 µA typ, 36 µA max

■Low supply voltage: 1.5 – 5.5 V

■Gain bandwidth product: 420 kHz typ

■Unity gain stability

■Low power shutdown mode: 5 nA typ

■Good accuracy: 800 µV max (A version)

■Low input bias current: 1 pA typ

■Micropackages: MiniSO-8, SOT23-8, MiniSO-10, TSSOP14, TSSOP16

■EMI hardened operational amplifiers

■High tolerance to ESD: 4 kV HBM

■Extended temperature range: -40 to +125° C

Applications

■Battery-powered applications

■Portable devices

■Signal conditioning

■Active filtering

■Medical instrumentation

Description

The TSV622, TSV623, TSV624 and TSV625 dual and quad operational amplifiers offer low voltage, low power operation and rail-to-rail input and output.

The TSV62x series features an excellent speed/power consumption ratio, offering a

420 kHz gain bandwidth product while consuming only 29 µA at a 5 V supply voltage. These opamps are unity gain stable for capacitive loads up to 100 pF. They also feature an ultra-low input bias current and low input offset voltage.

SOT23-8

SO-8

MiniSO-8

TSSOP-14

TSSOP-16

TSV623 (dual) and TSV625 (quad) have two shutdown pins in order to reduce power consumption.

These features make the TSV62x family ideal for sensor interfaces, battery-supplied and portable applications, as well as active filtering.

Table 1. |

Device summary |

|

|

||

|

Dual version |

Quad version |

|||

Reference |

|

|

|

|

|

Without |

With |

Without |

With |

||

|

|||||

|

standby |

standby |

standby |

standby |

|

|

|

|

|

|

|

TSV62x |

TSV622 |

TSV623 |

TSV624 |

TSV625 |

|

|

|

|

|

|

|

TSV62xA |

TSV622A |

TSV623A |

TSV624A |

TSV625A |

|

|

|

|

|

|

|

October 2009 |

Doc ID 15689 Rev 4 |

1/25 |

www.st.com

Contents |

TSV62x, TSV62xA |

|

|

Contents

1 |

Package pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 3 |

|

2 |

Absolute maximum ratings and operating conditions . . . . . . . . . . . . . |

4 |

|

3 |

Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

5 |

|

4 |

Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

13 |

|

|

4.1 |

Operating voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

13 |

|

4.2 |

Rail-to-rail input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

13 |

|

4.3 |

Rail-to-rail output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

13 |

|

4.4 |

Optimization of DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . |

14 |

|

4.5 |

Shutdown function (TSV623, TSV625) . . . . . . . . . . . . . . . . . . . . . . . . . . |

14 |

|

4.6 |

Driving resistive and capacitive loads . . . . . . . . . . . . . . . . . . . . . . . . . . . |

15 |

|

4.7 |

PCB layouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

15 |

|

4.8 |

Macromodel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

15 |

5 |

Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

16 |

|

5.1 SOT23-8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 5.2 SO-8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 5.3 MiniSO-8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 5.4 MiniSO-10 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 5.5 TSSOP14 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 5.6 TSSOP16 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

6 |

Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

23 |

7 |

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

24 |

2/25 |

Doc ID 15689 Rev 4 |

TSV62x, TSV62xA |

Package pin connections |

|

|

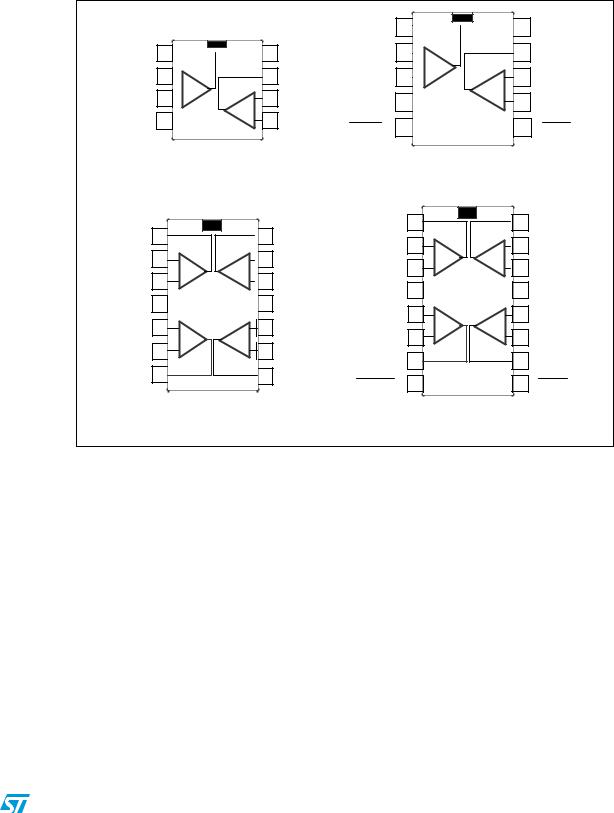

1 Package pin connections

Figure 1. Pin connections for each package (top view)

Out1 |

1 |

|

|

8 |

VCC+ |

In1- |

2 |

_ |

|

7 |

Out2 |

In1+ |

3 |

+ |

_ |

6 |

In2- |

VCC- |

4 |

|

+ |

5 |

In2+ |

|

TSV622IDT/IST/ILT |

|

|||

SO8/Mini-SO8/SOT23-8 |

|||||

Out1 |

1 |

|

|

14 |

Out4 |

In1- |

2 |

_ |

_ |

13 |

In4- |

In1+ |

3 |

+ |

+ |

12 |

In4+ |

VCC+ |

4 |

|

|

11 |

VCC- |

In2+ |

5 |

+ |

+ |

10 |

In3+ |

|

|

|

|

||

In2- |

6 |

_ |

_ |

9 |

In3- |

|

|

||||

Out2 |

7 |

|

|

8 |

Out3 |

TSV624IPT

TSSOP14

Out1 |

1 |

|

|

10 |

VCC+ |

In1- |

2 |

_ |

|

9 |

Out2 |

In1+ |

3 |

+ |

_ |

8 |

In2- |

VCC- |

4 |

|

+ |

7 |

In2+ |

SHDN1 |

5 |

|

|

6 |

SHDN2 |

|

|

TSV623IST |

|

|

|

|

|

MiniSO-10 |

|

|

|

Out1 |

1 |

|

|

16 |

Out4 |

In1- |

2 |

_ |

_ |

15 |

In4- |

In1+ |

3 |

+ |

+ |

14 |

In4+ |

VCC+ |

4 |

|

|

13 |

VCC- |

In2+ |

5 |

+ |

+ |

12 |

In3+ |

|

|

|

|

||

In2- |

6 |

_ |

_ |

11 |

In3- |

|

|

||||

Out2 |

7 |

|

|

10 |

Out3 |

SHDN1/2 |

8 |

|

|

9 |

SHDN3/4 |

|

|

TSV625IPT |

|

|

|

|

|

TSSOP16 |

|

|

|

Doc ID 15689 Rev 4 |

3/25 |

Absolute maximum ratings and operating conditions |

TSV62x, TSV62xA |

|

|

2 Absolute maximum ratings and operating conditions

Table 2. |

Absolute maximum ratings (AMR) |

|

|

|

|

|||

Symbol |

Parameter |

|

|

Value |

Unit |

|||

|

|

|

|

|

|

|

||

|

VCC |

Supply voltage(1) |

|

|

6 |

V |

||

|

Vid |

Differential input voltage (2) |

|

|

±VCC |

V |

||

|

V |

in |

Input voltage (3) |

V |

CC- |

- 0.2 to V + 0.2 |

V |

|

|

|

|

|

CC+ |

|

|||

|

I |

|

|

Input current (4) |

|

|

10 |

mA |

|

in |

|

|

|

|

|

||

|

|

|

|

Shutdown voltage(3) |

VCC- - 0.2 to VCC++ 0.2 |

V |

||

|

SHDN |

|||||||

|

Tstg |

Storage temperature |

|

|

-65 to +150 |

°C |

||

|

|

|

|

Thermal resistance junction to ambient(5)(6) |

|

|

|

|

|

|

|

|

SOT23-8 |

|

|

105 |

|

|

|

|

|

MiniSO-8 |

|

|

190 |

|

|

Rthja |

SO-8 |

|

|

125 |

°C/W |

||

|

|

|

|

Mini-SO10 |

|

|

113 |

|

|

|

|

|

TSSOP14 |

|

|

100 |

|

|

|

|

|

TSSOP16 |

|

|

95 |

|

|

|

|

|

|

|

|

||

|

Tj |

Maximum junction temperature |

|

|

150 |

°C |

||

|

|

|

|

HBM: human body model(7) |

|

|

4 |

kV |

|

ESD |

MM: machine model(8) |

|

|

200 |

V |

||

|

|

|

|

CDM: charged device model(9) |

|

|

1.5 |

kV |

|

|

|

|

Latch-up immunity |

|

|

200 |

mA |

|

|

|

|

|

|

|

|

|

1.All voltage values, except differential voltages are with respect to network ground terminal.

2.Differential voltages are the non-inverting input terminal with respect to the inverting input terminal.

3.VCC-Vin must not exceed 6 V, Vin must not exceed 6V.

4.Input current must be limited by a resistor in series with the inputs.

5.Short-circuits can cause excessive heating and destructive dissipation.

6.Rth are typical values.

7.Human body model: 100 pF discharged through a 1.5 kΩ resistor between two pins of the device, done for all couples of pin combinations with other pins floating.

8.Machine model: a 200 pF capacitor is charged to the specified voltage, then discharged directly between two pins of the device with no external series resistor (internal resistor < 5 Ω), done for all couples of pin combinations with other pins floating.

9.Charged device model: all pins plus package are charged together to the specified voltage and then discharged directly to ground.

Table 3. |

Operating conditions |

|

|

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

VCC |

Supply voltage |

1.5 to 5.5 |

V |

Vicm |

Common mode input voltage range |

VCC- - 0.1 to VCC+ + 0.1 |

V |

Toper |

Operating free air temperature range |

-40 to +125 |

°C |

4/25 |

Doc ID 15689 Rev 4 |

TSV62x, TSV62xA |

Electrical characteristics |

|

|

3 Electrical characteristics

Table 4. Electrical characteristics at VCC+ = +1.8 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25° C, and RL connected to VCC/2 (unless otherwise specified)

Symbol |

Parameter |

|

Conditions |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

|

DC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TSV62x |

|

|

|

4 |

|

|

|

TSV62xA |

|

|

|

0.8 |

mV |

Vio |

Offset voltage |

TSV623AIST - MiniSO10 |

|

|

1 |

|

|

|

|

|

|

|

|

||

TSV62x -Tmin < Top < Tmax |

|

|

6 |

|

|||

|

|

|

|

|

|||

|

|

TSV62xA - Tmin < Top < Tmax |

|

|

2 |

|

|

|

|

TSV623AIST - Tmin < Top < Tmax |

|

|

2.2 |

|

|

DVio |

Input offset voltage drift |

|

|

|

2 |

|

μV/°C |

Iio |

Input offset current |

|

|

|

1 |

10(1) |

pA |

|

|

|

|

|

|

||

(Vout = VCC/2) |

Tmin < Top < Tmax |

|

1 |

100 |

pA |

||

|

|

||||||

Iib |

Input bias current |

|

|

|

1 |

10(1) |

pA |

|

|

|

|

|

|

||

(Vout = VCC/2) |

Tmin < Top < Tmax |

|

1 |

100 |

pA |

||

|

|

||||||

CMR |

Common mode rejection |

0 V to 1.8 V, Vout = 0.9 V |

53 |

74 |

|

dB |

|

ratio 20 log ( Vic/ Vio) |

Tmin < Top < Tmax |

51 |

|

|

dB |

||

|

|

|

|||||

Avd |

Large signal voltage gain |

RL= 10 kΩ, Vout= 0.5 V to 1.3 V |

78 |

95 |

|

dB |

|

Tmin < Top < Tmax |

73 |

|

|

dB |

|||

|

|

|

|

||||

VOH |

High level output voltage |

RL = 10 kΩ |

|

35 |

5 |

|

mV |

Tmin < Top < Tmax |

50 |

|

|

||||

|

|

|

|

|

|||

VOL |

Low level output voltage |

RL = 10 kΩ |

|

|

4 |

35 |

mV |

Tmin < Top < Tmax |

|

|

50 |

||||

|

|

|

|

|

|||

|

Isink |

Vout = 1.8 V |

|

6 |

12 |

|

mA |

Iout |

Tmin < Top < Tmax |

4 |

|

|

|||

|

|

|

|

||||

Isource |

Vout = 0 V |

|

6 |

10 |

|

|

|

|

|

|

|

||||

|

Tmin < Top < Tmax |

4 |

|

|

|

||

|

|

|

|

|

|||

ICC |

Supply current (per operator) |

No load, Vout=VCC/2 |

|

25 |

31 |

µA |

|

Tmin < Top < Tmax |

|

|

33 |

µA |

|||

|

|

|

|

||||

AC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GBP |

Gain bandwidth product |

RL = 10 kΩ, CL = 100 pF, f = 100 kHz |

275 |

340 |

|

kHz |

|

Fu |

Unity gain frequency |

RL = 10 kΩ, CL = 100 pF, |

|

280 |

|

kHz |

|

φm |

Phase margin |

RL = 10 kΩ, |

CL = 100 pF |

|

41 |

|

Degrees |

Gm |

Gain margin |

RL = 10 kΩ, |

CL = 100 pF |

|

8 |

|

dB |

SR |

Slew rate |

RL = 10 kΩ, CL = 100 pF, Av=1 |

0.1 |

0.155 |

|

V/μs |

|

1. Guaranteed by design.

Doc ID 15689 Rev 4 |

5/25 |

Electrical characteristics |

|

|

|

|

|

|

TSV62x, TSV62xA |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 5. |

Shutdown characteristics VCC = 1.8 V (TSV623, TSV625) |

|

|

|

|

|

|||||||

Symbol |

|

|

Parameter |

|

|

|

Conditions |

|

Min. |

Typ. |

|

Max. |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

||

DC performance |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SHDN |

|

= VCC- |

|

|

2.5 |

|

50 |

nA |

|

|

Supply current in shutdown |

|

|

|

|

|

|

|

|

|

|

|

ICC |

|

|

Tmin < Top < 85° C |

|

|

|

|

200 |

nA |

||||

|

mode (all operators) |

|

|

|

|

|

|||||||

|

|

|

|

|

Tmin < Top < 125° C |

|

|

|

|

1.5 |

µA |

||

ton |

|

Amplifier turn-on time |

|

RL = 5 k, Vout = VCC- to VCC- + 0.2 V |

|

|

200 |

|

|

ns |

|||

toff |

|

Amplifier turn-off time |

|

RL = 2 k, Vout = VCC+ - 0.5 V to |

|

|

20 |

|

|

ns |

|||

|

|

VCC+ - 0.7 V |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||

VIH |

|

|

logic high |

|

|

|

|

|

1.35 |

|

|

|

V |

SHDN |

|

|

|

|

|

|

|||||||

VIL |

|

|

logic low |

|

|

|

|

|

|

|

|

0.6 |

V |

SHDN |

|

|

|

|

|

|

|||||||

IIH |

|

|

current high |

|

|

|

= VCC+ |

|

|

10 |

|

|

pA |

SHDN |

SHDN |

|

|

||||||||||

IIL |

|

|

current low |

|

|

|

= VCC- |

|

|

10 |

|

|

pA |

SHDN |

SHDN |

|

|

||||||||||

|

|

|

|

|

|

|

= VCC- |

|

|

50 |

|

|

pA |

IOLeak |

|

Output leakage in shutdown |

|

SHDN |

|

|

|||||||

|

mode |

|

Tmin < Top < 125° C |

|

|

1 |

|

|

nA |

||||

|

|

|

|

|

|

|

|

|

|||||

6/25 |

Doc ID 15689 Rev 4 |

TSV62x, TSV62xA |

|

|

|

Electrical characteristics |

||||

|

|

|

|

|

|

|

||

Table 6. |

VCC+ = +3.3 V, VCC- = 0 V, Vicm = VCC/2, Tamb = 25° C, RL connected to VCC/2 |

|

||||||

|

(unless otherwise specified) |

|

|

|

|

|

|

|

Symbol |

Parameter |

|

|

Conditions |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

|

|

DC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TSV62x |

|

|

|

|

4 |

|

|

|

TSV62xA |

|

|

|

|

0.8 |

|

Vio |

Offset voltage |

TSV623AIST - MiniSO10 |

|

|

1 |

mV |

||

|

|

|

|

|

|

|||

TSV62x -Tmin < Top < Tmax |

|

|

6 |

|||||

|

|

|

|

|

||||

|

|

TSV62xA - Tmin < Top < Tmax |

|

|

2 |

|

||

|

|

TSV623AIST - Tmin < Top < Tmax |

|

|

2.2 |

|

||

DVio |

Input offset voltage drift |

|

|

|

|

2 |

|

μV/°C |

Iio |

Input offset current |

|

|

|

|

1 |

10(1) |

pA |

|

Tmin < Top < Tmax |

|

1 |

100 |

pA |

|||

|

|

|

||||||

Iib |

Input bias current |

|

|

|

|

1 |

10(1) |

pA |

Tmin < Top < Tmax |

|

1 |

100 |

pA |

||||

|

|

|

||||||

CMR |

Common mode rejection |

0 V to 3.3 V, Vout = 1.65 V |

57 |

79 |

|

dB |

||

ratio 20 log ( Vic/ Vio) |

Tmin < Top < Tmax |

53 |

|

|

dB |

|||

|

|

|

||||||

|

|

R =10 kΩ, V |

= 0.5 V to 2.8 V |

81 |

98 |

|

dB |

|

Avd |

Large signal voltage gain |

L |

out |

|

|

|

|

|

Tmin < Top < Tmax |

76 |

|

|

dB |

||||

|

|

|

|

|||||

VOH |

High level output voltage |

RL = 10 kΩ |

|

|

35 |

5 |

|

mV |

Tmin < Top < Tmax |

50 |

|

|

|||||

|

|

|

|

|

||||

VOL |

Low level output voltage |

RL = 10 kΩ |

|

|

|

4 |

35 |

mV |

Tmin < Top < Tmax |

|

|

50 |

|||||

|

|

|

|

|

||||

|

Isink |

Vo = 5 V |

|

|

23 |

45 |

|

mA |

Iout |

Tmin < Top < Tmax |

20 |

|

|

||||

|

|

|

|

|||||

Isource |

Vo = 0 V |

|

|

23 |

38 |

|

mA |

|

|

|

|

|

|||||

|

Tmin < Top < Tmax |

20 |

|

|

||||

|

|

|

|

|

||||

ICC |

Supply current (per operator) |

No load, Vout= 2.5 V |

|

26 |

33 |

µA |

||

Tmin < Top < Tmax |

|

|

35 |

µA |

||||

|

|

|

|

|||||

AC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

GBP |

Gain bandwidth product |

RL = 10 kΩ, CL = 100 pF, f = 100 kHz |

310 |

380 |

|

kHz |

||

Fu |

Unity gain frequency |

RL = 10 kΩ, |

|

CL = 100 pF |

|

310 |

|

kHz |

φm |

Phase margin |

RL = 10 kΩ, |

|

CL = 100 pF |

|

41 |

|

Degrees |

Gm |

Gain margin |

RL = 10 kΩ, |

|

CL = 100 pF |

|

8 |

|

dB |

SR |

Slew rate |

RL = 10 kΩ, CL = 100 pF, AV = 1 |

0.11 |

0.175 |

|

V/μs |

||

1. Guaranteed by design.

Doc ID 15689 Rev 4 |

7/25 |

Electrical characteristics |

|

|

|

|

|

TSV62x, TSV62xA |

|

|||

|

|

|

|

|

|

|

|

|||

Table 7. |

VCC+ = +5 V, VCC- = 0 V, Vicm = VCC/2, Tamb = 25° C, RL connected to VCC/2 |

|

|

|||||||

|

(unless otherwise specified) |

|

|

|

|

|

|

|||

Symbol |

Parameter |

|

|

|

Conditions |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

DC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

TSV62x |

|

|

|

4 |

|

|

||

|

|

TSV62xA |

|

|

|

0.8 |

|

|

||

Vio |

Offset voltage |

TSV623AIST - MiniSO10 |

|

|

1 |

mV |

|

|||

|

|

|

|

|

|

|

|

|||

TSV62x - Tmin < Top < Tmax |

|

|

6 |

|

||||||

|

|

|

|

|

|

|||||

|

|

TSV62xA - Tmin < Top < Tmax |

|

|

2 |

|

|

|||

|

|

TSV62xA - Tmin < Top < Tmax |

|

|

2.2 |

|

|

|||

DVio |

Input offset voltage drift |

|

|

|

|

|

2 |

|

μV/°C |

|

Iio |

Input offset current |

|

|

|

|

|

1 |

10(1) |

pA |

|

Tmin < Top < Tmax |

|

1 |

100 |

pA |

|

|||||

|

|

|

|

|||||||

Iib |

Input bias current |

|

|

|

|

|

1 |

10(1) |

pA |

|

Tmin < Top < Tmax |

|

1 |

100 |

pA |

|

|||||

|

|

|

|

|||||||

CMR |

Common mode rejection |

0 V to 5 V, Vout = 2.5 V |

60 |

80 |

|

dB |

|

|||

ratio 20 log ( Vic/ Vio) |

Tmin < Top < Tmax |

55 |

|

|

|

|

||||

|

|

|

|

|

||||||

Avd |

Large signal voltage gain |

RL=10 kΩ, Vout = 0.5 V to 4.5 V |

85 |

98 |

|

dB |

|

|||

Tmin < Top < Tmax |

80 |

|

|

|

|

|||||

|

|

|

|

|

|

|||||

SVR |

Supply voltage rejection ratio |

VCC = 1.8 to 5 V |

75 |

102 |

|

dB |

|

|||

20 log ( VCC/ Vio) |

Tmin < Top < Tmax |

73 |

|

|

|

|

||||

|

|

|

|

|

||||||

|

|

VRF = 100 mVrms, f = 400 MHz |

|

61 |

|

|

|

|||

EMIRR |

EMI rejection ratio |

VRF = 100 mVrms, f = 900 MHz |

|

85 |

|

dB |

|

|||

EMIRR = -20 log (VRFpeak/ Vio) |

V |

RF |

= 100 mV , f = 1800 MHz |

|

92 |

|

|

|||

|

|

|

|

|

||||||

|

|

|

|

rms |

|

|

|

|

|

|

|

|

VRF = 100 mVrms, f = 2400 MHz |

|

83 |

|

|

|

|||

VOH |

High level output voltage |

RL = 10 kΩ |

|

35 |

7 |

|

mV |

|

||

Tmin < Top < Tmax |

50 |

|

|

|

||||||

|

|

|

|

|

|

|||||

VOL |

Low level output voltage |

RL = 10 kΩ |

|

|

6 |

35 |

mV |

|

||

Tmin < Top < Tmax |

|

|

50 |

|

||||||

|

|

|

|

|

|

|||||

|

Isink |

Vo = 5 V |

|

40 |

69 |

|

mA |

|

||

Iout |

Tmin < Top < Tmax |

35 |

|

|

|

|||||

|

|

|

|

|

||||||

Isource |

Vo = 0 V |

|

40 |

74 |

|

mA |

|

|||

|

|

|

|

|||||||

|

Tmin < Top < Tmax |

35 |

|

|

|

|||||

|

|

|

|

|

|

|||||

ICC |

Supply current (per operator) |

No load, Vout = 2.5 V |

|

29 |

36 |

µA |

|

|||

Tmin < Top < Tmax |

|

|

38 |

µA |

|

|||||

|

|

|

|

|

||||||

AC performance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

GBP |

Gain bandwidth product |

RL = 10 kΩ, CL = 100 pF, f = 100 kHz |

350 |

420 |

|

kHz |

|

|||

Fu |

Unity gain frequency |

RL = 10 kΩ, |

CL = 100 pF |

|

360 |

|

kHz |

|

||

8/25 |

Doc ID 15689 Rev 4 |

Loading...

Loading...