Philips NE591N, NE590N Datasheet

Philips Semiconductors Linear Products |

Product specification |

|

|

|

|

Addressable peripheral drivers |

NE590/591 |

|

|

|

|

DESCRIPTION

The NE590/591 addressable peripheral drivers are high current latched drivers, similar in function to the 9334 address decoder. The device has eight Darlington power outputs, each capable of 250mA load current. The outputs are turned on or off by respectively loading a logic high or logic low into the device data input. The required output is defined by a 3-bit address. The device must be enabled by a CE input line. A common clear input, CLR, turns all outputs off when a logic low is applied.

The NE590 has eight open-collector Darlington outputs which sink current to ground. The device is packaged in a 16-pin plastic or

Cerdip package.

The NE591 has eight open-emitter Darlington outputs which source current to an external load from a common collector line, VS. This VS line need not necessarily be the same as the 5V VCC supply. The device is packaged in an 18-pin plastic or Cerdip package.

FEATURES

•8 high current outputs

•Low-loading bus compatible inputs

•Power-on clear ensures safe operation

•NE590 will operate in addressable or demultiplex mode

•Allows random (addressed) data entry

•Easily expandable

•NE590 is pin compatible with 54/74LS259

APPLICATIONS

•Relay driver

•Indicator lamp driver

•Triac trigger

•LED display digit driver

•Stepper motor driver

ORDERING INFORMATION

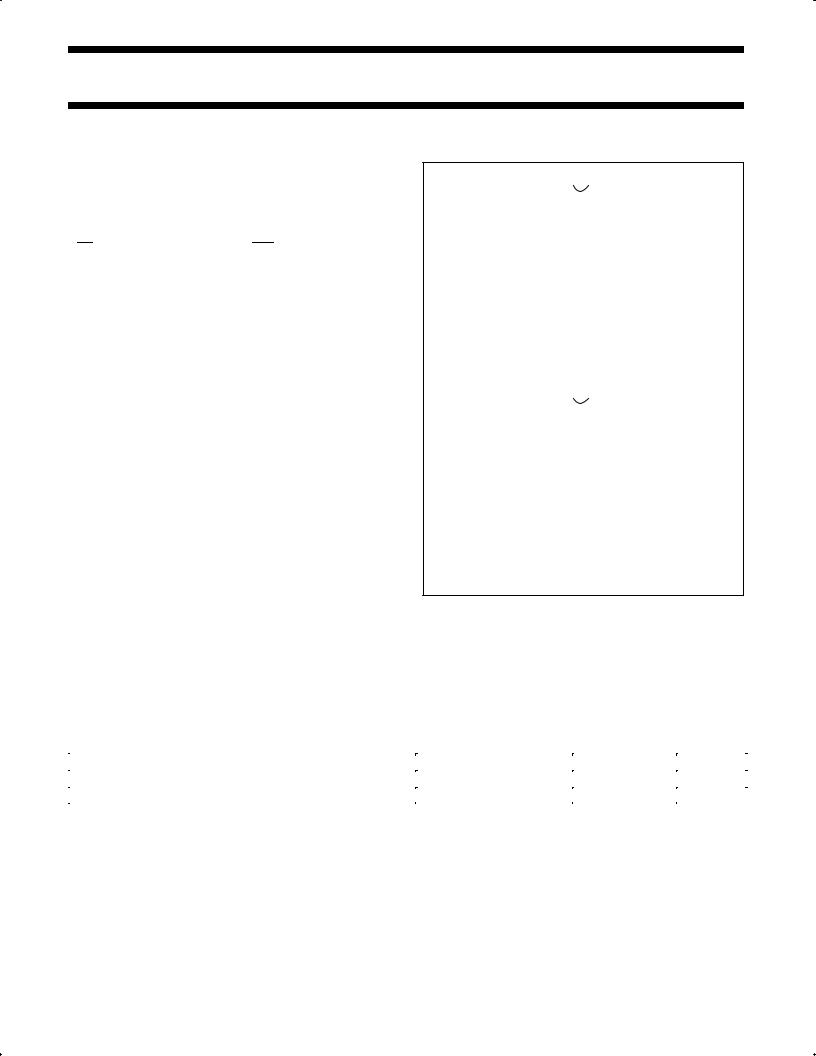

PIN CONFIGURATIONS

N Package

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

1 |

|

|

|

16 |

VCC |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

2 |

|

|

|

15 |

|

CLR |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

A2 |

3 |

|

|

|

14 |

|

CE |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

4 |

|

|

|

13 |

D |

|||||

|

|

|

|

|

|

|

|

|

|||

Q1 |

5 |

|

|

|

12 |

Q7 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

6 |

|

|

|

11 |

Q6 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

7 |

|

|

|

10 |

Q5 |

|||||

|

|

|

|

|

|||||||

GND |

8 |

|

|

|

9 |

Q4 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|||

|

|

|

|

NE590 |

|

|

|

|

|||

|

|

|

|

N Package |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

1 |

|

|

|

18 |

VCC |

|||

|

|

|

|

|

|

|

|

||||

A0 |

2 |

|

|

|

17 |

|

|

|

|

||

|

|

|

CLR |

||||||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

A1 |

3 |

|

|

|

16 |

|

|

|

|

||

|

|

|

CE |

||||||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

A2 |

4 |

|

|

|

15 |

D |

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||

Q0 |

5 |

|

|

|

14 |

Q7 |

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

Q1 |

6 |

|

|

|

13 |

Q6 |

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

Q2 |

7 |

|

|

|

12 |

Q5 |

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

Q3 |

8 |

|

|

|

11 |

Q4 |

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

GND |

9 |

|

|

|

10 |

VS |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW

NE591

DESCRIPTION |

TEMPERATURE RANGE |

ORDER CODE |

DWG # |

|

|

|

|

16-Pin Plastic Dual In-Line Package (DIP) |

0 to +70°C |

NE590N |

0406C |

|

|

|

|

18-Pin Plastic Dual In-Line Package (DIP) |

0 to +70°C |

NE591N |

0406C |

August 31, 1994 |

518 |

853-0951 13721 |

Philips Semiconductors Linear Products |

Product specification |

|

|

|

|

Addressable peripheral drivers |

NE590/591 |

|

|

|

|

PIN DESIGNATION

590 |

591 |

SYMBOL |

|

|

NAME & FUNCTION |

||||||||

PIN NO. |

PIN NO. |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1-3 |

2-4 |

A0-A2 |

A 3-bit binary address on these pins defines which of the 8 output latches is to receive the data. |

||||||||||

4-7, |

5-8, |

Q0-Q7 |

The 8 device outputs. The NE590 has open-collector Darlington outputs. The NE591 has open emit- |

||||||||||

9-12 |

11-14 |

|

|

|

|

|

ter-follower outputs. |

||||||

13 |

15 |

|

|

D |

The data input. When the chip is enabled, this data bit is transferred to the defined output such that: |

||||||||

|

|

|

|

|

|

|

ª1º turns output switch ªONº |

||||||

|

|

|

|

|

|

|

ª0º turns output switch ªOFFº |

||||||

|

|

|

|

|

|

|

Thus in logic terms, the NE590 inverts data to the relevant output. The NE591 retains true data at the |

||||||

|

|

|

|

|

|

|

output. |

||||||

14 |

16 |

|

|

|

|

|

The chip enable. When this input is low, the output latches will accept data. When |

|

|

goes high, all |

|||

|

|

CE |

CE |

||||||||||

|

|

|

|

|

|

|

outputs will retain their existing state regardless of address or data input conditions. |

||||||

15 |

17 |

|

|

|

The clear input. When |

|

goes low all output switches are turned ªOFFº. On the NE590, a high |

||||||

CLR |

CLR |

||||||||||||

|

|

|

|

|

|

|

data input will override the clear function on the addressed latch. On the NE591, |

|

low will over- |

||||

|

|

|

|

|

|

|

CLR |

||||||

|

|

|

|

|

|

|

ride any other condition. |

||||||

- |

1 |

|

|

|

|

The chip select input provides for an additional level of address decoding. |

|||||||

|

|

CS |

|||||||||||

- |

10 |

|

|

VS |

The VS line provides the power to all 8 output devices. It is connected to the collectors of all 8 output |

||||||||

|

|

|

|

|

|

|

transistors. This pin may be connected to the VCC or another supply. |

||||||

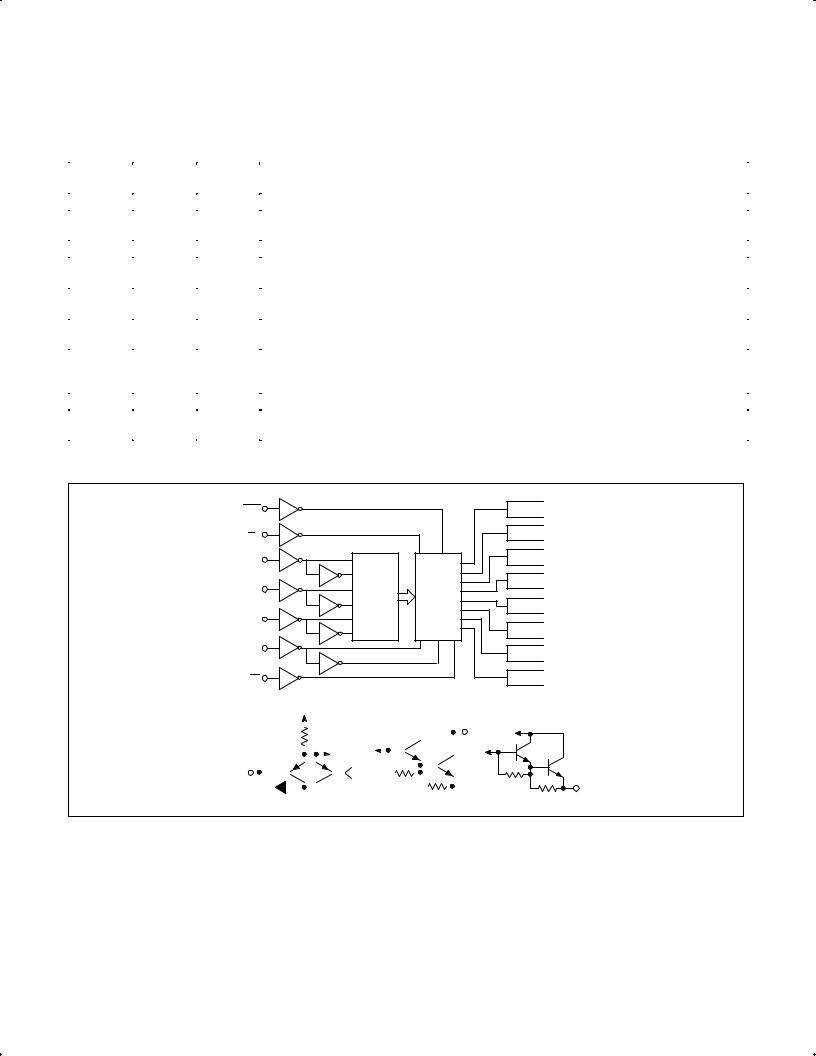

BLOCK DIAGRAM

CLR |

|

|

CE |

|

|

A0 |

|

|

A1 |

1±OF±8 |

COMTROL |

|

DECODER |

GATE |

A2 |

|

|

D |

|

|

cs |

|

|

(NE51 ONLY) INPUT STAGE

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

NE590 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LATCH  Q0

Q0

LATCH  Q1

Q1

LATCH  Q2

Q2

LATCH  Q3

Q3

LATCH  Q4

Q4

LATCH  Q5

Q5

LATCH  Q6

Q6

LATCH  Q7

Q7

OUTPUT STAGE

NE591

August 31, 1994 |

519 |

Philips Semiconductors Linear Products |

Product specification |

|

|

|

|

Addressable peripheral drivers |

NE590/591 |

|

|

|

|

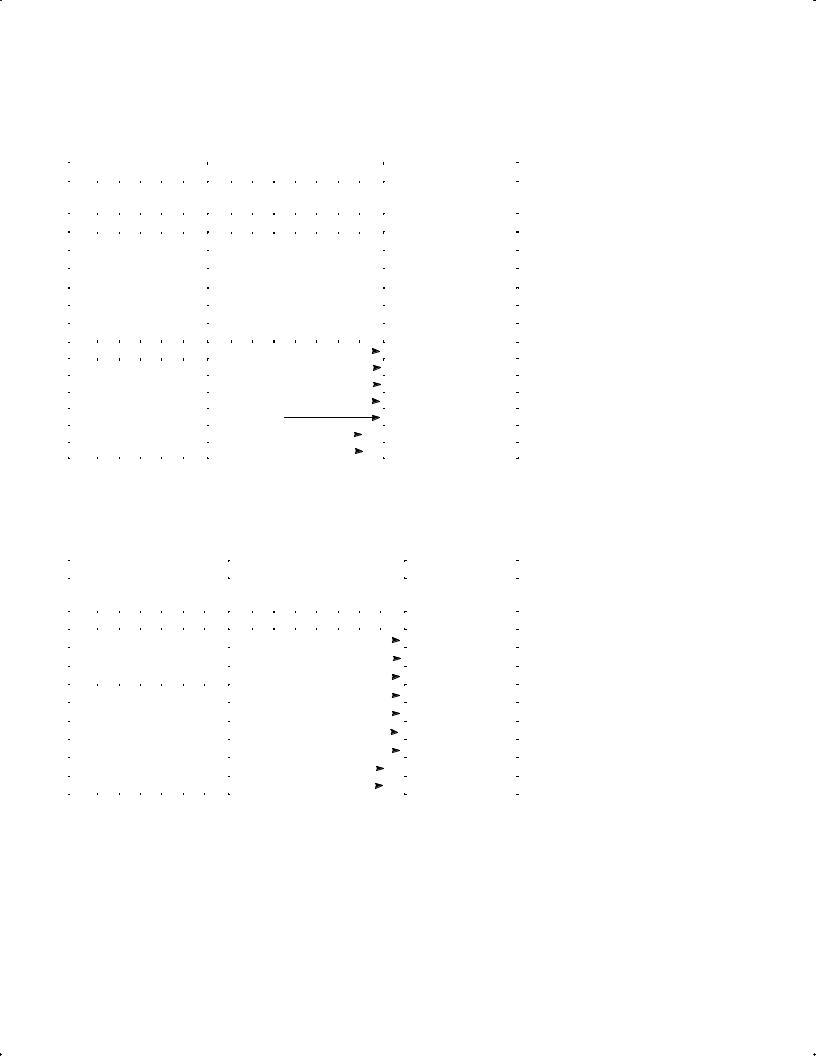

TRUTH TABLE (NE590)

|

|

|

|

|

|

|

|

INPUTS |

|

|

|

|

|

|

|

|

OUTPUTS |

|

|

|

|

|

MODE |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

D A A A2 |

Q Q Q Q Q Q Q Q |

|

||||||||||||||||

CL |

C |

|

||||||||||||||||||||||||

|

|

R |

|

|

E |

|

|

0 |

1 |

|

0 |

1 |

|

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|||||

|

|

L |

|

H |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

|

H |

Clear |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

L L L L L L |

H |

H H H H H H H |

|

|||||||||||||||||||||

|

|

L L H L |

L L |

L |

H H H H H H H |

|

||||||||||||||||||||

|

|

L |

|

|

L |

L |

H |

L |

L |

H |

H |

H |

H |

H |

H |

H |

|

H |

Demultiplex |

|||||||

|

|

L L H |

H L L |

H L H H H H H H |

|

|||||||||||||||||||||

|

|

L L L |

H H H |

H H H H H H H H |

|

|||||||||||||||||||||

|

|

L L H H H H |

H H H H H H H L |

|

||||||||||||||||||||||

|

|

H |

|

H |

X |

X |

X |

X |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

H L L L L L |

H QN-1 |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

H L H L |

L L |

L QN-1 |

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

H |

|

|

L |

L |

H |

L |

L |

QN-1 |

|

|

H QN-1 |

|

|

|

|

|

|

|

Addressable Latch |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

H L H |

H L L |

QN-1 L QN-1 |

|

|

|

|

|

|

|

|||||||||||||||

|

|

H L L |

H H H |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

H |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

H L H H H H |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

L |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

NOTES:

X=Don't care condition

QN-1=Previous output state

L=Low voltage level/ªOFFº output state

H=High voltage level/ªONº output state

TRUTH TABLE (NE591)

|

|

|

|

|

|

|

|

|

|

INPUTS |

|

|

|

|

|

|

|

|

|

OUTPUTS |

|

|

|

|

|

MODE |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

D A A A2 |

Q Q Q Q Q Q Q Q |

|

|||||||||||||||||

CL |

C |

C |

|

||||||||||||||||||||||||||||

|

|

R |

|

|

|

E |

|

|

S |

|

|

0 |

1 |

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

||||||

|

|

L |

|

X |

|

|

X |

X |

X |

X |

X |

L |

L |

L |

L |

L |

L |

L |

L |

Clear |

|||||||||||

|

|

H H H |

X X X X |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

H |

|

H |

|

|

L |

X |

X |

X |

X |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

H L H X X X X |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

H L L L L L L |

L QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

H L L H L |

L L |

H QN-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

H |

|

|

L |

|

|

L |

L |

H |

L |

L |

QN-1 L |

|

QN-1 |

|

|

|

|

|

|

|

|

Addressable Latch |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

H L L H H L L |

QN-1 H QN-1 |

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

H L L L H H H |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

L |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

H L L H H H H |

QN-1 |

|

|

|

|

|

|

|

|

|

|

|

H |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

NOTES:

X=Don't care condition

QN-1=Previous output state

L=Low voltage level/ªOFFº output state

H=High voltage level/ªONº output state

August 31, 1994 |

520 |

Loading...

Loading...