Philips N74F374DB, N74F374D, N74F373DB, N74F373D, N74F374N Datasheet

...

FAST PRODUCTS

74F373

Octal transparent latch (3-State)

74F374

Octal D flip-flop (3-State)

Product specification |

1994 Dec 05 |

IC15 Data Handbook

Philips Semiconductors

Philips Semiconductors |

Product specification |

|

|

|

|

|

|

|

Latch/flip-flop |

74F373/74F374 |

|

74F373 Octal transparent latch (3-State) 74F374 Octal D-type flip-flop (3-State)

FEATURES

•8-bit transparent latch Ð 74F373

•8-bit positive edge triggered register Ð 74F374

•3-State outputs glitch free during power-up and power-down

•Common 3-State output register

•Independent register and 3-State buffer operation

•SSOP Type II Package

DESCRIPTION

The 74F373 is an octal transparent latch coupled to eight 3-State output devices. The two sections of the device are controlled

The 74F374 is an 8-bit edge triggered register coupled to eight 3-State output buffers. The two sections of the device are controlled independently by clock (CP) and output enable (OE) control gates.

The register is fully edge triggered. The state of the D input, one setup time before the low-to-high clock transition is transferred to the corresponding flip-flop's Q output.

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors.

The active low output enable (OE) controls all eight 3-State buffers independent of the register operation. When OE is low, the data in the register appears at the outputs. When OE is high, the outputs

are in high impedance ªoffº state, which means they will neither drive nor load the bus.

independently by enable (E) and output enable (OE) control gates.

The data on the D inputs is transferred to the latch outputs when the enable (E) input is high. The latch remains transparent to the data input while E is high, and stores the data that is present one setup time before the high-to-low enable transition.

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors.

The active low output enable (OE) controls all eight 3-State buffers independent of the latch operation. When OE is low, latched or transparent data appears at the output.

When OE is high, the outputs are in high impedance ªoffº state, which means they will neither drive nor load the bus.

ORDERING INFORMATION

|

|

TYPICAL |

TYPICAL SUPPLY |

|

TYPE |

PROPAGATION |

CURRENT |

||

|

|

DELAY |

(TOTAL) |

|

|

|

|

|

|

74F373 |

4.5ns |

35mA |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TYPICAL SUPPLY |

TYPE |

|

TYPICAL fmax |

|

CURRENT |

|

|

|

|

(TOTAL) |

|

|

|

|

|

74F374 |

|

165MHz |

|

55mA |

|

|

|

|

|

|

ORDER CODE |

|

|

|

|

DESCRIPTION |

COMMERCIAL RANGE |

PKG DWG # |

|

VCC = 5V ±10%, Tamb = 0°C to +70°C |

|

20-pin plastic DIP |

N74F373N, N74F374N |

SOT146-1 |

|

|

|

20-pin plastic SOL |

N74F373D, N74F374D |

SOT163-1 |

|

|

|

20-pin plastic SSOP type II |

N74F373DB, N74374DB |

SOT399-1 |

|

|

|

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS |

DESCRIPTION |

74F (U.L.) |

LOAD VALUE |

|||

HIGH/LOW |

HIGH/LOW |

|||||

|

|

|

|

|||

|

|

|

|

|

|

|

D0 - D7 |

Data inputs |

1.0/1.0 |

20μA/0.6mA |

|||

|

|

|

|

|

|

|

E (74F373) |

Enable input (active high) |

1.0/1.0 |

20μA/0.6mA |

|||

|

|

|

|

|

|

|

|

|

|

Output enable inputs (active low) |

1.0/1.0 |

20μA/0.6mA |

|

|

OE |

|||||

|

|

|

|

|||

CP (74F374) |

Clock pulse input (active rising edge) |

1.0/1.0 |

20μA/0.6mA |

|||

|

|

|

|

|||

Q0 - Q7 |

3-State outputs |

150/40 |

3.0mA/24mA |

|||

|

|

|

|

|

|

|

NOTE: One (1.0) FAST unit load is defined as: 20μA in the high state and 0.6mA in the low state.

December 5, 1994 |

2 |

853-0369 14383 |

Philips Semiconductors |

Product specification |

|

|

|

|

Latch/flip-flop |

74F373/74F374 |

|

|

|

|

PIN CONFIGURATION ± 74F373 |

|

|

PIN CONFIGURATION ± 74F374 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

OE |

1 |

20 |

|||

OE |

1 |

20 |

VCC |

|

|

Q0 |

Q7 |

|||||

|

|

|

|

|||||||||

|

Q0 |

2 |

19 |

Q7 |

|

|

2 |

19 |

||||

|

|

|

D0 |

|

|

D7 |

||||||

|

D0 |

3 |

18 |

D7 |

|

|

3 |

18 |

||||

|

|

|

D1 |

|

|

D6 |

||||||

|

D1 |

4 |

17 |

D6 |

|

|

4 |

17 |

||||

|

|

|

Q1 |

|

|

Q6 |

||||||

|

Q1 |

5 |

16 |

Q6 |

|

|

5 |

16 |

||||

|

|

|

Q2 |

|

|

Q5 |

||||||

|

Q2 |

6 |

15 |

Q5 |

|

|

6 |

15 |

||||

|

|

|

D2 |

|

|

D5 |

||||||

|

D2 |

7 |

14 |

D5 |

|

|

7 |

14 |

||||

|

|

|

D3 |

|

|

D4 |

||||||

|

D3 |

8 |

13 |

D4 |

|

|

8 |

13 |

||||

|

|

|

Q3 |

|

|

Q4 |

||||||

|

Q3 |

9 |

12 |

Q4 |

|

|

9 |

12 |

||||

|

|

GND |

|

|

CP |

|||||||

GND 10 |

11 |

E |

|

10 |

11 |

|||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

SF00250 |

|

|

|

|

|

SF00253 |

|

LOGIC SYMBOL ± 74F373

3 4 7 8 13 14 17 18

D0 D1 D2 D3 D4 D5 D6 D7

11 |

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

5 |

6 |

9 |

12 |

15 |

16 |

19 |

|||||||||

VCC = Pin 20

GND = Pin 10

SF00251

IEC/IEE SYMBOL ± 74F374

3 4 7 8 13 14 17 18

D0 D1 D2 D3 D4 D5 D6 D7

11 |

|

|

CP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

5 |

6 |

9 |

12 |

15 |

16 |

19 |

|||||||||

VCC = Pin 20

GND = Pin 10

SF00254

IEC/IEEE SYMBOL ± 74F373

1 |

EN1 |

||

|

|||

11 |

EN2 |

||

|

|||

|

|

|

|

3 |

2D |

1 |

2 |

|

|

||

4 |

|

|

5 |

7 |

|

|

6 |

8 |

|

|

9 |

13 |

|

|

12 |

|

|

||

14 |

|

|

15 |

|

|

||

17 |

|

|

16 |

18 |

|

|

19 |

|

|

|

SF00252 |

|

|

|

IEC/IEEE SYMBOL ± 74F374

1 |

EN1 |

||

|

|||

11 |

C2 |

||

|

|||

|

|

|

|

3 |

2D |

1 |

2 |

|

|

||

4 |

|

|

5 |

7 |

|

|

6 |

8 |

|

|

9 |

13 |

|

|

12 |

|

|

||

14 |

|

|

15 |

|

|

||

17 |

|

|

16 |

18 |

|

|

19 |

|

|

|

SF00255 |

|

|

|

December 5, 1994 |

3 |

Philips Semiconductors |

Product specification |

|

|

|

|

Latch/flip-flop |

74F373/74F374 |

|

|

|

|

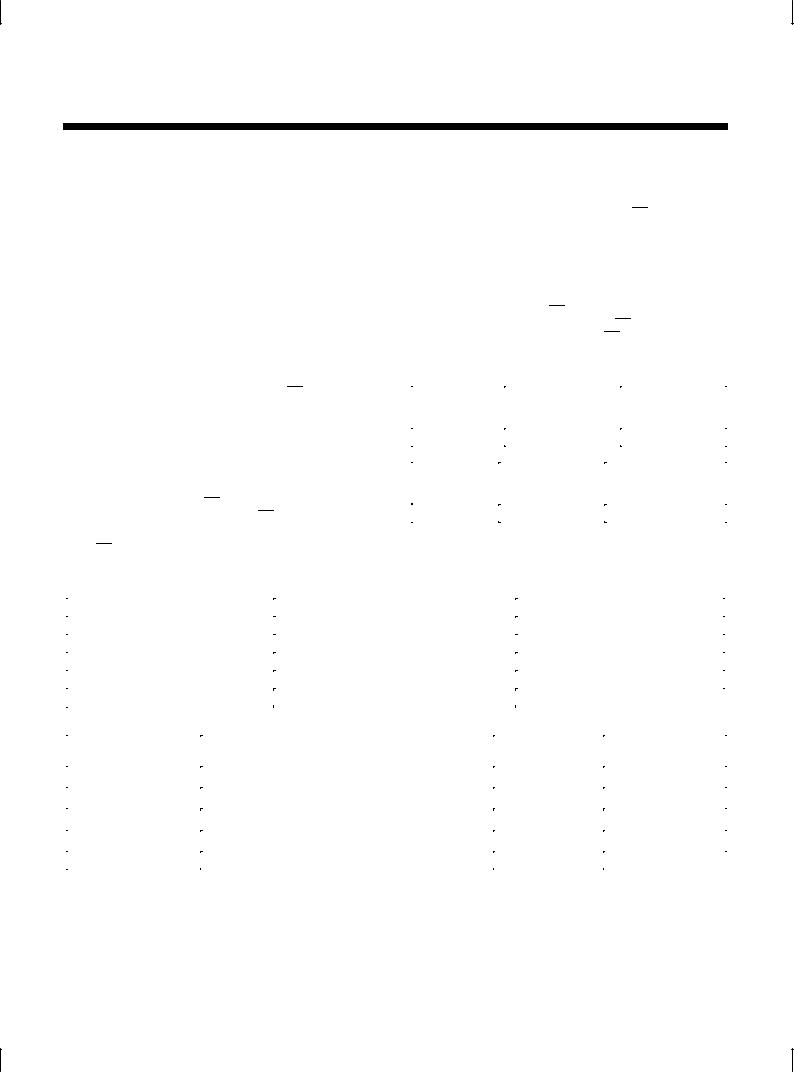

LOGIC DIAGRAM FOR 74F373

|

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

|

3 |

4 |

7 |

8 |

13 |

14 |

17 |

18 |

|

|

D |

D |

D |

D |

D |

D |

D |

|

D |

|

E Q |

E Q |

E Q |

E Q |

E Q |

E Q |

E Q |

|

E Q |

E |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE 1 |

|

|

|

|

|

|

|

|

|

|

|

2 |

5 |

6 |

9 |

12 |

15 |

16 |

19 |

VCC = Pin 20 |

|

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

GND = Pin 10 |

|

|

|

|

|

|

|

|

SF00256 |

|

|

|

|

|

|

|

|

|

|

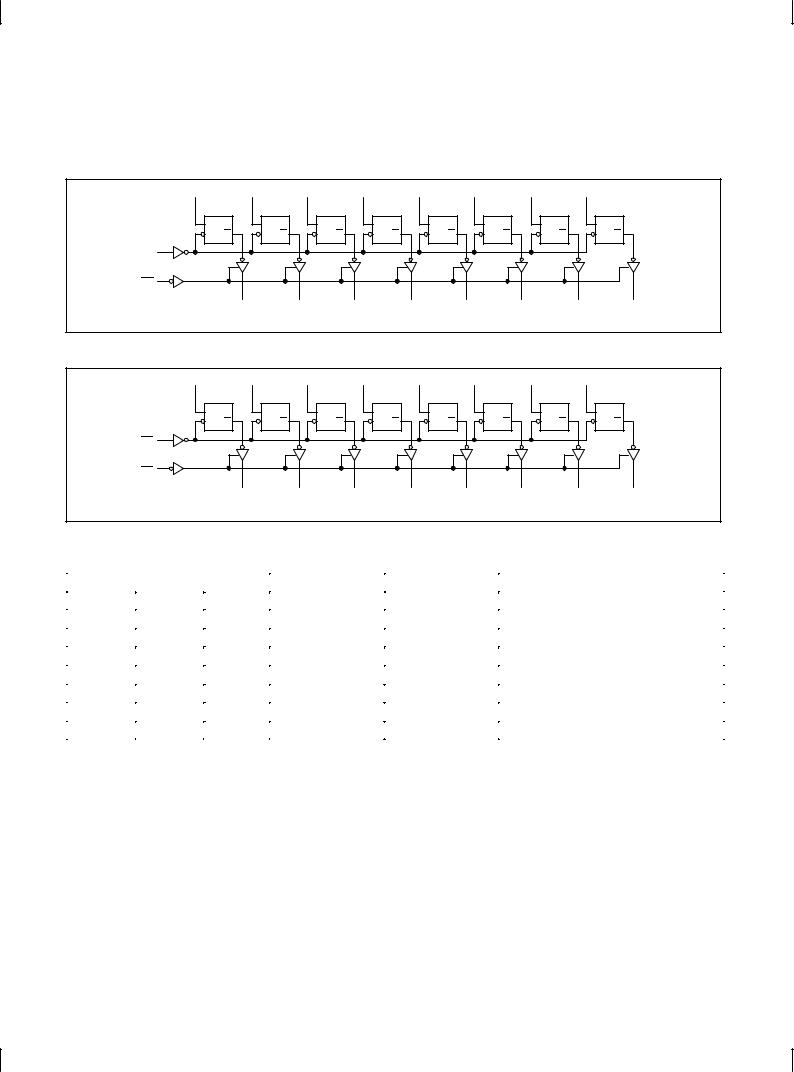

LOGIC DIAGRAM FOR 74F374

|

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

|

3 |

4 |

7 |

8 |

13 |

14 |

17 |

18 |

|

|

D |

D |

D |

D |

D |

D |

D |

|

D |

|

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

|

CP Q |

CP |

11 |

|

|

|

|

|

|

|

|

OE |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = Pin 20 |

|

2 |

5 |

6 |

9 |

12 |

15 |

16 |

19 |

|

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

|

GND = Pin 10 |

|

||||||||

|

|

|

|

|

|

|

|

|

SF00257 |

FUNCTION TABLE FOR 74F373

|

|

|

|

|

INPUTS |

|

INTERNAL |

OUTPUTS |

OPERATING MODE |

|

|

|

OE |

|

|

E |

Dn |

REGISTER |

Q0 - Q7 |

|

|

|

|

L |

|

|

|

H |

L |

L |

L |

Enable and read register |

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

H |

H |

H |

H |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

↓ |

l |

L |

L |

Latch and read register |

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

↓ |

h |

H |

H |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

L |

X |

NC |

NC |

Hold |

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

L |

X |

NC |

Z |

Disable outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

H |

Dn |

Dn |

Z |

|

|

|

|

|

|

|

|||||

NOTES: |

|

|

|

|

|

|||||

H |

= |

|

High-voltage level |

|

|

|

|

|||

h |

= |

|

High state must be present one setup time before the high-to-low enable transition |

|

||||||

L |

= |

|

Low-voltage level |

|

|

|

|

|||

l |

= |

|

Low state must be present one setup time before the high-to-low enable transition |

|

||||||

NC= |

No change |

|

|

|

|

|

||||

X |

= |

|

Don't care |

|

|

|

|

|

||

Z |

= |

|

High impedance ªoffº state |

|

|

|

||||

↓ |

= |

|

High-to-low enable transition |

|

|

|

||||

December 5, 1994 |

4 |

Loading...

Loading...