Philips N74ALS651D, N74ALS651N, N74ALS652-1D, N74ALS652-1N, N74ALS652D Datasheet

...

INTEGRATED CIRCUITS

74ALS651/74ALS651±1

74ALS652/74ALS652±1

Transceiver/register

Product specification |

1991 Feb 08 |

IC05 Data Handbook |

|

m n r

Philips Semiconductors Product specification

Transceiver/register |

74ALS651/74ALS651-1 |

||

74ALS652/74ALS652-1 |

|||

|

|

||

|

|

|

|

|

|

|

|

74ALS651/651-1 |

Octal transceiver/register, inverting (3-State) |

|

|

74ALS652/652-1 |

Octal transceiver/register, non-inverting (3-State) |

||

FEATURES

•Independent registers for A and B buses

•Multiplexed real-time and stored data

•Choice of non-inverting and inverting data paths

•3-State outputs

•The -1 versions sinks 48mA IOL within the ±5% VCC range

DESCRIPTION

The 74LAS651 and 74ALS652 transceivers/registers consist of bus transceiver circuits with 3-State outputs, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes High. Output enable (OEAB, OEBA) and select (SAB, SBA) pins are provided for bus management. The 74LAS651-1 and 74ALS652-1 will sink 48mA if the VCC is limited to 5.0V ± 0.25V.

|

TYPICAL |

TYPICAL |

|

TYPE |

SUPPLY CURRENT |

||

fMAX |

|||

|

(TOTAL) |

||

74ALS651/74ALS651-1 |

140MHz |

40mA |

|

|

|

|

|

74ALS652/74ALS652-1 |

140MHz |

46mA |

|

|

|

|

ORDERING INFORMATION

|

ORDER CODE |

|

|

|

|

DRAWING |

|

|

COMMERCIAL RANGE |

||

DESCRIPTION |

VCC = 5V ±10%, |

NUMBER |

|

|

Tamb = 0°C to +70°C |

|

|

24-pin plastic DIP |

74ALS651N, 74ALS651-1N, |

SOT222-1 |

|

74ALS652N, 74ALS652-1N |

|||

|

|

||

|

|

|

|

24-pin plastic SOL |

74ALS651D, 74ALS651-1D, |

SOT137-1 |

|

74ALS652D, 74ALS652-1D |

|||

|

|

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

|

PINS |

DESCRIPTION |

74ALS (U.L.) |

LOAD VALUE |

|

|

HIGH/LOW |

HIGH/LOW |

|||

|

|

|

|

||

|

|

|

|

|

|

A0 ± A7 |

A inputs |

1.0/1.0 |

70μA/0.1mA |

||

|

|

|

|

|

|

B0 ± B7 |

B inputs |

1.0/1.0 |

70μA/0.1mA |

||

|

|

|

|

|

|

|

CPAB |

A-to-B clock input |

1.0/1.0 |

20μA/0.1mA |

|

|

|

|

|

|

|

|

CPBA |

B-to-A clock input |

1.0/1.0 |

20μA/0.1mA |

|

|

|

|

|

|

|

|

SAB |

A-to-B select input |

1.0/1.0 |

20μA/0.1mA |

|

|

|

|

|

|

|

|

SBA |

B-to-A select input |

1.0/1.0 |

20μA/0.1mA |

|

|

|

|

|

|

|

|

OEAB |

A-to-B output enable input |

1.0/1.0 |

20μA/0.1mA |

|

|

|

|

|

|

|

|

|

|

B-to-A output enable input |

1.0/1.0 |

20μA/0.1mA |

|

OEBA |

||||

|

|

|

|

||

A0 ± A7, B0 ± B7 |

A, B outputs |

750/240 |

15mA/24mA |

||

|

|

|

|

||

A0 ± A7, B0 ± B7 |

A, B outputs (-1 version) |

750/480 |

15mA/48mA |

||

NOTE: One (1.0) ALS unit load is defined as: 20μA in the High state and 0.1mA in the Low state.

1991 Feb 08 |

2 |

853±1407 01670 |

Philips Semiconductors Product specification

Transceiver/register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74ALS651/74ALS651-1 |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74ALS652/74ALS652-1 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

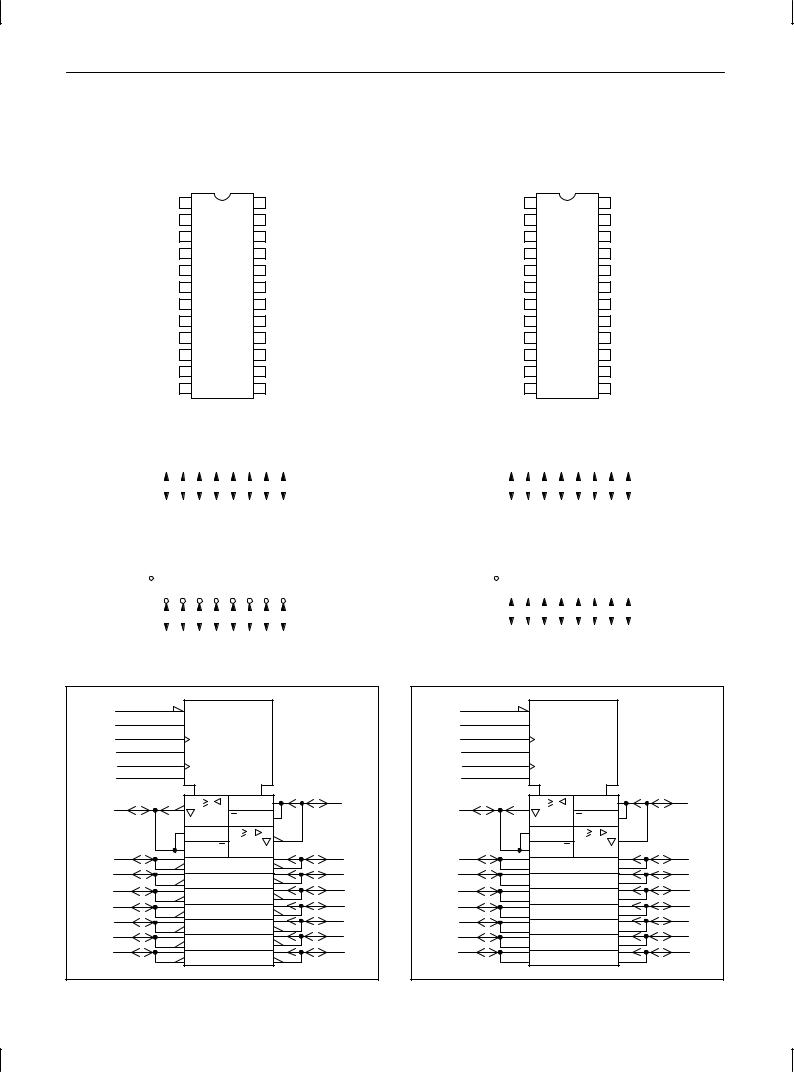

PIN CONFIGURATION ± 74ALS651/651-1 |

|

PIN CONFIGURATION ± 74ALS652/652-1 |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

CPAB |

1 |

|

|

|

|

|

|

|

|

24 |

|

VCC |

|

|

|

|

CPAB |

1 |

|

|

|

|

|

|

|

|

24 |

VCC |

|||||||||||||

|

|

|

SAB |

2 |

|

|

|

|

|

|

|

|

23 |

|

CPBA |

|

|

|

|

SAB |

2 |

|

|

|

|

|

|

|

|

23 |

|

CPBA |

||||||||||||

|

|

|

OEAB |

3 |

|

|

|

|

|

|

|

|

22 |

|

SBA |

|

|

|

|

OEAB |

3 |

|

|

|

|

|

|

|

|

22 |

|

SBA |

||||||||||||

|

|

|

A0 |

4 |

|

|

|

|

|

|

|

|

21 |

|

|

|

|

|

|

|

|

|

A0 |

4 |

|

|

|

|

|

|

|

|

21 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

OEBA |

|

|

|

|

|

|

|

|

|

|

|

OEBA |

||||||||||||||||||||||

|

|

|

A1 |

5 |

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

A1 |

5 |

|

|

|

|

|

|

|

|

20 |

|

B0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B0 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A2 |

6 |

|

|

|

|

|

|

|

|

19 |

|

|

|

|

|

|

|

|

|

A2 |

6 |

|

|

|

|

|

|

|

|

19 |

|

B1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B1 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A3 |

7 |

|

|

|

|

|

|

|

|

18 |

|

|

|

|

|

|

|

|

|

A3 |

7 |

|

|

|

|

|

|

|

|

18 |

|

B2 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B2 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A4 |

8 |

|

|

|

|

|

|

|

|

17 |

|

|

|

|

|

|

|

|

|

A4 |

8 |

|

|

|

|

|

|

|

|

17 |

|

B3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B3 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A5 |

9 |

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

A5 |

9 |

|

|

|

|

|

|

|

|

16 |

|

B4 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B4 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A6 |

10 |

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

A6 |

10 |

|

|

|

|

|

|

|

|

15 |

|

B5 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B5 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

A7 |

11 |

|

|

|

|

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

A7 |

11 |

|

|

|

|

|

|

|

|

14 |

|

B6 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B6 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

GND |

12 |

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

GND |

12 |

|

|

|

|

|

|

|

|

13 |

|

B7 |

|||||||||

|

|

|

|

|

|

|

|

|

|

B7 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC00127 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC00128 |

LOGIC SYMBOL ± 74ALS651/651-1 |

|

LOGIC SYMBOL ± 74ALS652/652-1 |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

|

|

|

|

|

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

|

|

|

|

|

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

|

||||||||||||||||||||

1 |

|

|

CPAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

CPAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

2 |

|

|

SAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

SAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

3 |

|

|

OEAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

OEAB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

23 |

|

|

CPBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

CPBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

22 |

|

|

SBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

SBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

21 |

|

|

OEBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

|

|

OEBA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

B0 |

B1 |

B2 |

B3 |

B4 |

B5 |

B6 |

B7 |

|

|

|

|

|

B0 |

B1 |

B2 |

B3 |

B4 |

B5 |

B6 |

B7 |

|

||||||||||||||||||||

VCC = Pin 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = Pin 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

|

|

|

|

|

||||||||||||||||||||||||||||||||

GND = Pin 12 |

|

SC00129 |

|

GND = Pin 12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC00130 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEC/IEEE SYMBOL ± 74ALS651/651-1

21 |

EN1 [BA] |

|

||

3 |

|

|||

EN1 [AB] |

|

|||

23 |

|

|||

G3 |

|

|

||

22 |

|

|

||

G5 |

|

|

||

1 |

|

|

||

C6 |

|

|

||

2 |

|

|

||

G7 |

|

|

||

|

|

|

||

4 |

1 |

5 |

20 |

|

4D |

||||

|

1 |

5 |

1 |

|

|

|

|

||

|

6D |

7 |

1 |

|

|

1 |

7 |

2 |

|

5 |

19 |

|||

|

||||

|

|

|||

6 |

|

|

18 |

|

7 |

|

|

17 |

|

8 |

|

|

16 |

|

9 |

|

|

15 |

|

10 |

|

|

14 |

|

11 |

|

|

13 |

|

SC00131

IEC/IEEE SYMBOL ± 74ALS652/652-1

21 |

EN1 [BA] |

|

||

3 |

|

|||

EN1 [AB] |

|

|||

23 |

|

|||

G3 |

|

|

||

22 |

|

|

||

G5 |

|

|

||

1 |

|

|

||

C6 |

|

|

||

2 |

|

|

||

G7 |

|

|

||

|

|

|

||

4 |

1 |

5 |

20 |

|

4D |

||||

|

1 |

5 |

1 |

|

|

|

|

||

|

6D |

7 |

1 |

|

|

1 |

7 |

2 |

|

5 |

19 |

|||

|

||||

|

|

|||

6 |

|

|

18 |

|

7 |

|

|

17 |

|

8 |

|

|

16 |

|

9 |

|

|

15 |

|

10 |

|

|

14 |

|

11 |

|

|

13 |

|

SC00132

1991 Feb 08 |

3 |

Philips Semiconductors Product specification

Transceiver/register |

|

|

74ALS651/74ALS651-1 |

|

|

|

74ALS652/74ALS652-1 |

||

|

|

|

||

|

|

|

|

|

BUS MANAGEMENT FUNCTIONS |

|

|

|

|

The following examples demonstrate the four fundamental |

|

|

|

|

bus-management functions that can be performed with the |

|

|

|

|

74ALS651/74ALS651-1 and 74ALS652/74ALS652-1. The select |

|

|

|

|

pins determine whether data is stored or transferred through the |

|

|

|

|

device in real time. The output enable pins determine the direction of |

|

|

|

|

the data flow. |

|

|

|

|

|

|

|

|

|

REAL TIME BUS TRANSFER |

REAL TIME BUS TRANSFER |

STORAGE FROM |

TRANSFER STORED DATA |

|

BUS B TO BUS A |

BUS A TO BUS B |

A, B, OR A AND B |

TO A AND/OR B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUS A |

|

|

|

|

BUS B |

BUS A |

|

|

|

|

|

BUS B |

BUS A |

|

|

BUS B |

BUS A |

|

|

|

|

|

|

|

BUS B |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OEABOEBA CPAB CPBA SAB |

SBA |

OEABOEBA CPAB CPBA SAB |

SBA |

|

|

CPAB CPBA SAB |

SBA |

|

|

|

SBA |

||||||||||

OEABOEBA |

OEABOEBA CPAB CPBA SAB |

||||||||||||||||||||

L |

L |

X |

X |

X |

L |

H |

H |

X |

X |

L |

X |

X |

X |

↑ |

X |

X |

X |

H |

L H or L H or L H |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

X |

X |

↑ |

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

X |

↑ |

↑ |

X |

X |

|

|

|

|

SC00133

1991 Feb 08 |

4 |

Loading...

Loading...