Philips N74ALS253N, N74ALS253DB, N74ALS253D Datasheet

INTEGRATED CIRCUITS

74ALS253

Dual 4±input multiplexer (3±State)

Product specification |

1991 Feb 08 |

IC05 Data Handbook |

|

m n r

Philips Semiconductors |

Product specification |

|

|

|

|

|

|

|

Dual 4-input multiplexer (3-State) |

74ALS253 |

|

|

|

|

|

|

|

FEATURES

•3-State outputs for bus interface and multiplex operation

•Common select inputs

•Separate output enable inputs

DESCRIPTION

The 74ALS253 has two identical 4-input multiplexers with 3-State outputs which select 2 bits from four sources by using common

select input (S0, S1). When the individual output enable (OEa, OEb) inputs of the 4-input multiplexers are High, the outputs are forced to a High impedance (Z) state.

The 74ALS253 is the logic implementation of 2-pole, 4-position switch being determined by the logic levels supplied to the common select inputs.

To avoid exceeding the maximum current ratings when the outputs of the 3-State devices are tied together, all but one device must be in the High impedance state. Therefore, only one output enable must be achieved at a time.

|

TYPICAL |

TYPICAL |

|

TYPE |

SUPPLY CURRENT |

||

PROPAGATION DELAY |

|||

|

(TOTAL) |

||

|

|

||

|

|

|

|

74ALS253 |

7.0ns |

8mA |

PIN CONFIGURATION

|

|

|

|

|

|

|

|

|

|

|

|

OEa |

1 |

|

|

|

16 |

VCC |

|||

|

S1 |

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

15 |

|

OEb |

|||

|

I3a |

|

|

|

|

|

S0 |

|||

|

3 |

|

|

|

14 |

|||||

|

I2a |

|

|

|

|

|

I3b |

|||

|

4 |

|

|

|

13 |

|||||

|

I1a |

|

|

|

|

|

I2b |

|||

|

5 |

|

|

|

12 |

|||||

|

I0a |

|

|

|

|

|

I1b |

|||

|

6 |

|

|

|

11 |

|||||

|

Ya |

|

|

|

|

|

I0b |

|||

|

7 |

|

|

|

10 |

|||||

GND |

|

|

|

|

|

Yb |

||||

8 |

|

|

|

9 |

||||||

|

|

|

|

|

|

|

|

|

|

|

SF00798

ORDERING INFORMATION

|

ORDER CODE |

|

|

|

|

DRAWING |

|

DESCRIPTION |

COMMERCIAL RANGE |

||

NUMBER |

|||

|

VCC = 5V ±10%, |

||

|

Tamb = 0°C to +70°C |

|

|

16-pin plastic DIP |

74ALS253N |

SOT38-4 |

|

|

|

|

|

16-pin plastic SO |

74ALS253D |

SOT109-1 |

|

|

|

|

|

16-pin plastic SSOP |

74ALS253DB |

SOT338-1 |

|

Type II |

|||

|

|

||

|

|

|

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DESCRIPTION |

|

|

|

74ALS (U.L.) |

|

|

|

|

LOAD VALUE |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH/LOW |

|

|

|

|

HIGH/LOW |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

I0a ± I3a |

|

|

|

Port A data inputs |

|

|

|

|

|

|

|

|

|

|

1.0/1.0 |

|

|

|

|

|

|

20μA/0.1mA |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

I0b ± I3b |

|

|

|

Port B data inputs |

|

|

|

|

|

|

|

|

|

|

1.0/1.0 |

|

|

|

|

|

|

20μA/0.1mA |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

S0, S1 |

|

|

|

Common select inputs |

|

|

|

|

|

|

|

|

1.0/1.0 |

|

|

|

|

|

|

20μA/0.1mA |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

Port A Output Enable input (active-Low) |

|

|

|

|

1.0/1.0 |

|

|

|

|

|

|

20μA/0.1mA |

|||||||||||||||||

|

OEa |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

Port B Output Enable input (active-Low) |

|

|

|

|

1.0/1.0 |

|

|

|

|

|

|

20μA/0.1mA |

|||||||||||||||||

|

OEb |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Ya ± Yb |

|

|

|

3-State outputs |

|

|

|

|

|

|

|

|

|

|

130/240 |

|

|

|

|

|

2.6mA/24mA |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

NOTE: One (1.0) ALS unit load is defined as: 20μA in the High state and 0.1mA in the Low state. |

|

|

|

|

|

|||||||||||||||||||||||||||||||

LOGIC SYMBOL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEC/IEEE SYMBOL |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

5 |

4 |

3 |

10 |

11 |

12 |

13 |

|

|

14 |

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

0 |

|

|

G |

0 |

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

2 |

|

|

|

3 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I0a |

I1a |

I2a |

|

I3a |

|

I0b |

I1b |

I2b |

I3b |

|

|

|

1 |

|

EN |

|

MUX |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|||||||||||||||||||||

14 |

|

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

7 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

2 |

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

1 |

|

|

OEa |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

||||||||

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

OEb |

|

|

|

|

Ya |

Yb |

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

9 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

||

VCC = Pin 16 |

|

|

|

|

|

|

7 |

|

9 |

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

||||||||

GND = Pin 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SF00799 |

|

|

|

|

|

|

|

|

|

|

|

|

|

SC00073 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1991 Feb 08 |

2 |

853±1378 01670 |

Philips Semiconductors |

Product specification |

|

|

|

|

Dual 4-input multiplexer (3-State) |

74ALS253 |

|

|

|

|

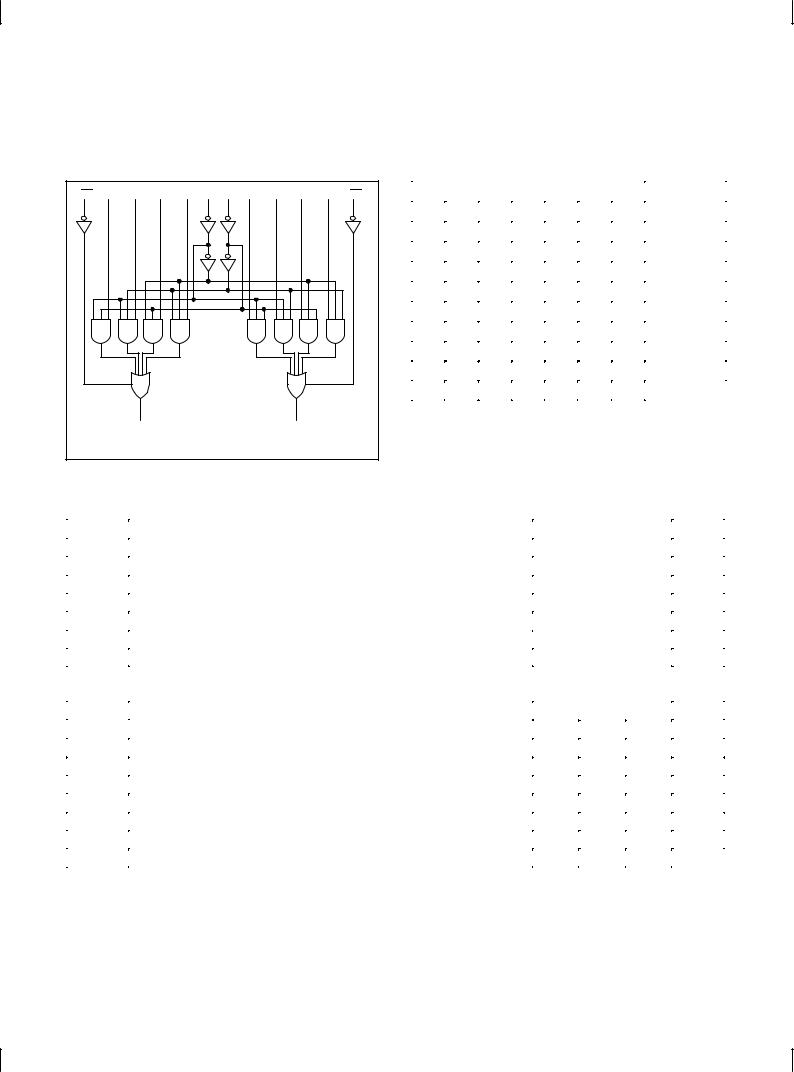

LOGIC DIAGRAM

OEa |

I0a |

I1a |

I2a |

I3a |

S1 |

S0 |

I0b |

I1b |

I2b |

I3b |

OEb |

1 |

6 |

5 |

4 |

3 |

2 |

14 |

10 |

11 |

12 |

13 |

15 |

7 |

9 |

Ya |

Yb |

VCC = Pin 16 |

|

GND = Pin 8 |

SC00074 |

|

FUNCTION TABLE

|

|

|

|

|

|

INPUTS |

|

|

|

|

|

OUTPUTS |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S0 |

|

S1 |

|

I0 |

|

I1 |

|

I2 |

I3 |

|

|

|

Yn |

|

|

|

|

|

OEn |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

X |

|

X |

|

X |

|

X |

X |

|

H |

Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

L |

|

X |

|

X |

X |

|

L |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

H |

|

X |

|

X |

X |

|

L |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

|

X |

|

L |

|

X |

X |

|

L |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

|

X |

|

H |

|

X |

X |

|

L |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

H |

|

X |

|

X |

|

L |

X |

|

L |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

H |

|

X |

|

X |

|

H |

X |

|

L |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

H |

|

X |

|

X |

|

X |

L |

|

L |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

H |

|

X |

|

X |

|

X |

H |

|

L |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

H |

= |

High voltage level |

|

|

|

|

|

|

||||||

L |

= |

Low voltage level |

|

|

|

|

|

|

||||||

X |

= |

Don't care |

|

|

|

|

|

|

|

|

|

|

||

Z |

= |

High impedance ªoffº state |

|

|

|

|

|

|||||||

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limit set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free air temperature range.)

SYMBOL |

PARAMETER |

RATING |

UNIT |

|

|

|

|

VCC |

Supply voltage |

±0.5 to +7.0 |

V |

VIN |

Input voltage |

±0.5 to +7.0 |

V |

IIN |

Input current |

±30 to +5 |

mA |

VOUT |

Voltage applied to output in High output state |

±0.5 to VCC |

V |

IOUT |

Current applied to output in Low output state |

48 |

mA |

Tamb |

Operating free-air temperature range |

0 to +70 |

°C |

Tstg |

Storage temperature range |

±65 to +150 |

°C |

RECOMMENDED OPERATING CONDITIONS

SYMBOL |

PARAMETER |

|

LIMITS |

|

UNIT |

|

|

|

|

||||

MIN |

NOM |

MAX |

||||

|

|

|

||||

|

|

|

|

|

|

|

VCC |

Supply voltage |

4.5 |

5.0 |

5.5 |

V |

|

VIH |

High-level input voltage |

2.0 |

|

|

V |

|

VIL |

Low-level input voltage |

|

|

0.8 |

V |

|

IIK |

Input clamp current |

|

|

±18 |

mA |

|

IOH |

High-level output current |

|

|

±2.6 |

mA |

|

IOL |

Low-level output current |

|

|

24 |

mA |

|

Tamb |

Operating free-air temperature range |

0 |

|

+70 |

°C |

1991 Feb 08 |

3 |

Loading...

Loading...