Philips NE630D, NE630N, SA630D, SA630N Datasheet

RF COMMUNICATIONS PRODUCTS

OUTPUT/INPUT

INPUT/OUTPUT

OUTPUT/INPUT

ENCH1

SA630

Single pole double throw (SPDT) switch

Product Specification

1997 Nov 07

Replaces data of October 10, 1991 IC17 Data Handbook

Philips Semiconductors

Philips Semiconductors |

Product specification |

|

|

|

|

|

|

|

Single pole double throw (SPDT) switch |

SA630 |

|

|

|

|

|

|

|

DESCRIPTION

The SA630 is a wideband RF switch fabricated in BiCMOS technology and incorporating on-chip CMOS/TTL compatible drivers. Its primary function is to switch signals in the frequency range DC - 1GHz from one 50Ω channel to another. The switch is activated by a CMOS/TTL compatible signal applied to the enable channel 1 pin (ENCH1).

The extremely low current consumption makes the SA630 ideal for portable applications. The excellent isolation and low loss makes this a suitable replacement for PIN diodes.

The SA630 is available in an 8-pin dual in-line plastic package and an 8-pin SO (surface mounted miniature) package.

FEATURES

•Wideband (DC - 1GHz)

•Low through loss (1dB typical at 200MHz)

•Unused input is terminated internally in 50Ω

•Excellent overload capability (1dB gain compression point +18dBm at 300MHz)

•Low DC power (170μA from 5V supply)

•Fast switching (20ns typical)

•Good isolation (off channel isolation 60dB at 100MHz)

PIN CONFIGURATION

D and N Packages

VDD |

1 |

|

8 |

OUT1 |

|

|

|

|

|

GND |

2 |

|

7 |

AC GND |

|

|

|

|

|

INPUT |

3 |

|

6 |

GND |

|

|

|

|

|

|

|

|

|

|

ENCH1 |

4 |

|

5 |

OUT2 |

SR00578

Figure 1. Pin Configuration

•Low distortion (IP3 intercept +33dBm)

•Good 50Ω match (return loss 18dB at 400MHz)

•Full ESD protection

•Bidirectional operation

APPLICATIONS

•Digital transceiver front-end switch

•Antenna switch

•Filter selection

•Video switch

•FSK transmitter

ORDERING INFORMATION

DESCRIPTION |

TEMPERATURE RANGE |

ORDER CODE |

DWG # |

|

|

|

|

8-Pin Plastic Dual In-Line Package (DIP) |

-40 to +85°C |

SA630N |

SOT97-1 |

|

|

|

|

8-Pin Plastic Small Outline (SO) package (Surface-mount) |

-40 to +85°C |

SA630D |

SOT96-1 |

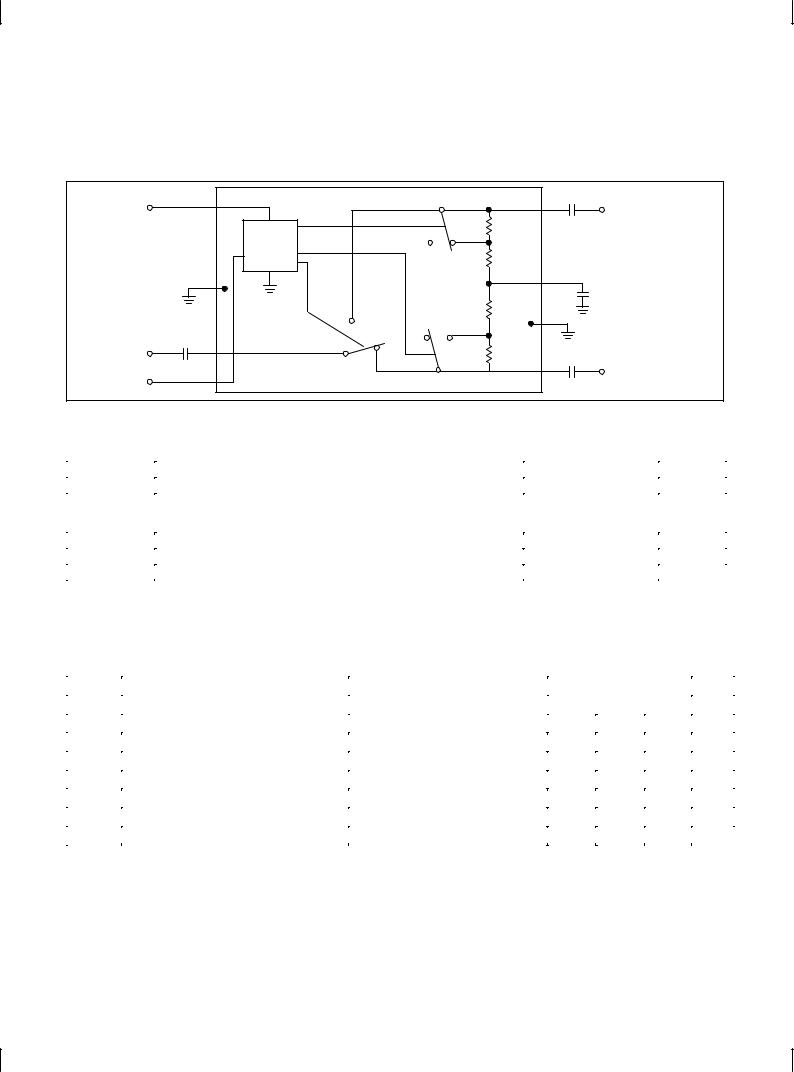

BLOCK DIAGRAM

|

INPUT/OUTPUT |

|

|

|

|

|

OUTPUT/INPUT |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

OUTPUT/INPUT |

|

|

ENCH1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SR00579 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 2. Block Diagram |

|

|||||

RECOMMENDED OPERATING CONDITIONS |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

SYMBOL |

PARAMETER |

|

|

|

|

|

RATING |

UNITS |

|

|

|

|

|

|

|

|

|

|

|

VDD |

Supply voltage |

|

|

|

|

|

3.0 to 5.5V |

V |

|

TA |

Operating ambient temperature range |

|

|

|

|

|

-40 to +85 |

°C |

|

SA Grade |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

TJ |

Operating junction temperature range |

|

|

|

|

|

-40 to +105 |

°C |

|

SA Grade |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

1997 Nov 07 |

2 |

853-1577 18666 |

Philips Semiconductors |

Product specification |

|

|

|

|

Single pole double throw (SPDT) switch |

SA630 |

|

|

|

|

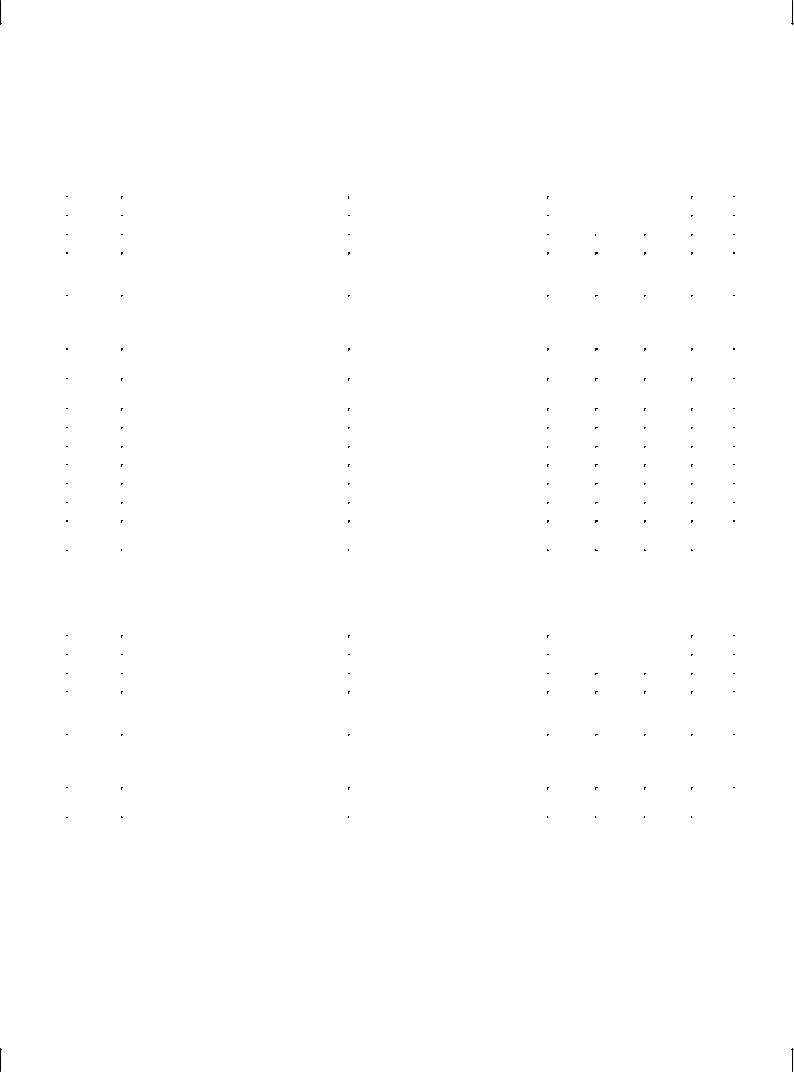

EQUIVALENT CIRCUIT |

|

|

|

VDD |

1 |

8 |

|

+5V |

|||

|

OUT1 |

||

|

|

||

|

|

20kΩ |

|

|

|

CONTROL |

|

|

|

LOGIC |

|

|

|

50Ω |

|

|

|

7 |

|

|

2 |

AC BYPASS |

|

|

|

||

|

|

50Ω |

|

|

|

6 |

|

INPUT |

3 |

20kΩ |

|

|

|||

|

4 |

OUT2 |

|

ENCH1 |

5 |

||

|

|

||

|

|

SR00580 |

Figure 3. Equivalent Circuit

ABSOLUTE MAXIMUM RATINGS

SYMBOL |

PARAMETER |

RATING |

UNITS |

|

|

|

|

VDD |

Supply voltage |

-0.5 to +5.5 |

V |

|

Power dissipation, T = 25oC (still air)1 |

|

|

|

A |

|

|

PD |

8-Pin Plastic DIP |

1160 |

mW |

|

8-Pin Plastic SO |

780 |

mW |

|

|

|

|

TJMAX |

Maximum operating junction temperature |

150 |

°C |

PMAX |

Maximum power input/output |

+20 |

dBm |

TSTG |

Storage temperature range |

-65 to +150 |

°C |

NOTES:

1. Maximum dissipation is determined by the operating ambient temperature and the thermal resistance, θJA: 8-Pin DIP: θJA = 108°C/W

8-Pin SO: θJA = 158°C/W

DC ELECTRICAL CHARACTERISTICS

VDD = +5V, TA = 25°C; unless otherwise stated.

|

|

|

|

LIMITS |

|

|

|

|

|

|

|

|

|

SYMBOL |

PARAMETER |

TEST CONDITIONS |

|

SA630 |

|

UNITS |

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

IDD |

Supply current |

|

40 |

170 |

300 |

μA |

V |

TTL/CMOS logic threshold voltage1 |

|

1.1 |

1.25 |

1.4 |

V |

T |

|

|

|

|

|

|

VIH |

Logic 1 level |

Enable channel 1 |

2.0 |

|

VDD |

V |

VIL |

Logic 0 level |

Enable channel 2 |

-0.3 |

|

0.8 |

V |

IIL |

ENCH1 input current |

ENCH1 = 0.4V |

-1 |

0 |

1 |

μA |

IIH |

ENCH1 input current |

ENCH1 = 2.4V |

-1 |

0 |

1 |

μA |

NOTE:

1. The ENCH1 input must be connected to a valid Logic Level for proper operation of the SA630.

1997 Nov 07 |

3 |

Philips Semiconductors |

Product specification |

|

|

|

|

Single pole double throw (SPDT) switch |

SA630 |

|

|

|

|

AC ELECTRICAL CHARACTERISTICS1 - D PACKAGE

VDD = +5V, |

TA = 25°C; unless otherwise stated. |

|

|

|

|

|

||

|

|

|

|

|

|

LIMITS |

|

|

|

|

|

|

|

|

|

||

SYMBOL |

PARAMETER |

TEST CONDITIONS |

|

SA630 |

|

UNITS |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DC - 100MHz |

|

1 |

|

|

S21, S12 |

Insertion loss (ON channel) |

500MHz |

|

1.4 |

2.8 |

dB |

||

|

|

|

|

900MHz |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10MHz |

70 |

80 |

|

|

S |

, S |

12 |

Isolation (OFF channel)2 |

100MHz |

|

60 |

|

dB |

21 |

|

|

500MHz |

24 |

50 |

|

|

|

|

|

|

|

900MHz |

30 |

|

|

|

|

|

|

|

|

|

|

|

|

S11, S22 |

Return loss (ON channel) |

DC - 400MHz |

|

20 |

|

dB |

||

900MHz |

|

12 |

|

|||||

S11, S22 |

Return loss (OFF channel) |

DC - 400MHz |

|

17 |

|

dB |

||

900MHz |

|

13 |

|

|||||

tD |

|

Switching speed (on-off delay) |

50% TTL to 90/10% RF |

|

20 |

|

ns |

|

tr, tf |

|

Switching speeds (on-off rise/fall time) |

90%/10% to 10%/90% RF |

|

5 |

|

ns |

|

|

|

|

Switching transients |

|

|

165 |

|

mVP-P |

P-1dB |

1dB gain compression |

DC - 1GHz |

|

+18 |

|

dBm |

||

IP3 |

|

Third-order intermodulation intercept |

100MHz |

|

+33 |

|

dBm |

|

IP2 |

|

Second-order intermodulation intercept |

100MHz |

|

+52 |

|

dBm |

|

NF |

|

Noise figure (ZO = 50Ω ) |

100MHz |

|

1.0 |

|

dB |

|

|

900MHz |

|

2.0 |

|

||||

|

|

|

|

|

|

|

|

|

NOTE:

1.All measurements include the effects of the D package SA630 Evaluation Board (see Figure 4B). Measurement system impedance is 50Ω.

2.The placement of the AC bypass capacitor is critical to achieve these specifications. See the applications section for more details.

AC ELECTRICAL CHARACTERISTICS1 - N PACKAGE

VDD = +5V, TA = 25°C; all other characteristics similar to the D-Package, unless otherwise stated.

|

|

|

|

LIMITS |

|

|

|

|

|

|

|

|

|

SYMBOL |

PARAMETER |

TEST CONDITIONS |

|

SA630 |

|

UNITS |

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

|

|

DC - 100MHz |

|

1 |

|

|

S21, S12 |

Insertion loss (ON channel) |

500MHz |

|

1.4 |

|

dB |

|

|

900MHz |

|

2.5 |

|

|

|

|

|

|

|

|

|

|

|

10MHz |

|

68 |

|

|

S21, S12 |

Isolation (OFF channel) |

100MHz |

58 |

50 |

|

dB |

500MHz |

37 |

|

||||

|

|

900MHz |

|

15 |

|

|

|

|

|

|

|

|

|

NF |

Noise figure (ZO = 50Ω ) |

100MHz |

|

1.0 |

|

dB |

900MHz |

|

2.5 |

|

|||

|

|

|

|

|

|

|

NOTE:

1. All measurements include the effects of the N package SA630 Evaluation Board (see Figure 4C). Measurement system impedance is 50Ω.

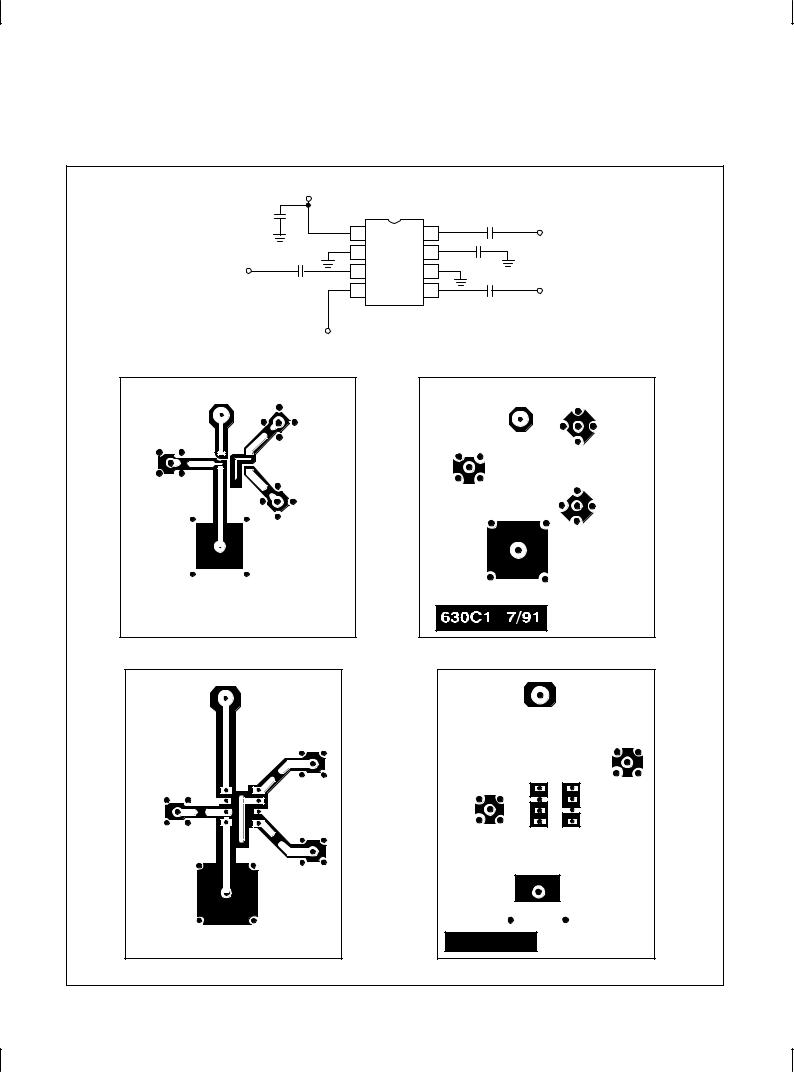

APPLICATIONS

The typical applications schematic and printed circuit board layout of the SA630 evaluation board is shown in Figure 4. The layout of the board is simple, but a few cautions need to be observed. The input and output traces should be 50Ω. The placement of the AC bypass capacitor is extremely critical if a symmetric isolation between the two channels is desired. The trace from Pin 7 should be drawn back towards the package and then be routed downwards. The capacitor

should be placed straight down as close to the device as practical. For better isolation between the two channels at higher frequencies, it is also advisable to run the two output/input traces at an angle. This also minimizes any inductive coupling between the two traces. The power supply bypass capacitor should be placed close to the device. Figure 10 shows the frequency response of the SA630. The loss matching between the two channels is excellent to 1.2GHz as shown in Figure 13.

1997 Nov 07 |

4 |

Philips Semiconductors |

Product specification |

|

|

|

|

Single pole double throw (SPDT) switch |

SA630 |

|

|

|

|

|

VDD |

|

|

|

|

|

+5V |

|

|

|

|

|

D and N Packages |

|

|

|

|

|

0.1μF |

|

|

0.01μF |

|

|

|

|

|

||

|

1 |

8 |

|

|

OUT1 |

|

GND |

7 |

AC GND |

0.01μF |

|

|

2 |

|

|

|

|

INPUT |

3 |

6 |

GND |

|

|

|

|

|

|||

|

0.01μF |

5 |

|

|

|

|

4 |

|

|

OUT2 |

|

|

|

|

|

|

|

|

ENCH1 |

|

|

0.01μF |

|

|

|

|

|

|

|

|

a. Evaluation Board Schematic |

|

|

||

|

b. 630 D-Package Board Layout |

|

|

||

|

|

|

630N1 |

7/91 |

|

|

c. 630 N-Package Board Layout |

|

SR00581 |

||

|

|

|

|

|

|

Figure 4. Board and Package Graphics

1997 Nov 07 |

5 |

Loading...

Loading...