Philips NE56632-31D, NE56632-43D, NE56632-45D, NE56632-46D, NE56632-30D Datasheet

...

INTEGRATED CIRCUITS

NE56632-XX

Active-LOW system reset with adjustable delay time

Product data |

2002 Mar 25 |

P s

on o s

Philips Semiconductors |

Product data |

|

|

|

|

|

|

|

Active-LOW system reset with adjustable delay time |

NE56632-XX |

|

|

|

|

|

|

|

DESCRIPTION

The NE56632-XX is a family of Active-LOW, power-on reset that offers precision threshold voltage detection within ±1.5% and super low operating supply current of typically 3.0 μA. It includes a reset delay that is user adjustable with an external capacitor.

Several detection threshold voltages are available at 1.9V , 2.0 V,

2.7 V, 2.8 V, 2.9 V, 3.0 V, 3.1 V, 4.2 V, 4.3 V, 4.4 V, 4.5 V, and 4.6 V.

Other thresholds are offered upon request at 100 mV steps from 1.9 V to 4.6 V.

With its ultra low supply current and high precision voltage threshold detection capability, the NE56632-XX is well suited for various battery powered applications such as reset circuits for logic and microprocessors, voltage check, and level detecting. It is available in the SOT23-5 package.

FEATURES |

|

|

|

|

|

|

|

|

|

|

|

|

APPLICATIONS |

||||||||

•High precision threshold detection voltage: VS ±1.5% |

•Reset for microprocessor and logic circuits |

||||||||||||||||||||

•Super low operating supply current: 3 μA typ. |

•Voltage level detection circuit |

||||||||||||||||||||

•Built-in hysteresis voltage: |

50 mV typ. |

•Battery voltage check circuit |

|||||||||||||||||||

•Detection threshold voltage: |

|

|

1.9 V, 2.0 V, 2.7 V, 2.8 V, 2.9 V, |

•Detection circuit for battery back-up |

|||||||||||||||||

3.0 V, 3.1 V, 4.2 V, 4.3 V, 4.4 V, 4.5 V, and 4.6 V. |

|

||||||||||||||||||||

•Reset Output: Active-LOW, open collector |

|

||||||||||||||||||||

•Other detection threshold voltages available upon request at |

|

||||||||||||||||||||

100 mV steps from 1.9 V to 4.6 V. |

|

|

|

|

|

|

|||||||||||||||

•Large low reset output current: 30 mA typ. |

|

||||||||||||||||||||

•Power-on reset delay time adjustable with external capacitor: |

|

||||||||||||||||||||

200 μs to 200 ms |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

•Reset assertion with VCC down to 0.65 V |

|

||||||||||||||||||||

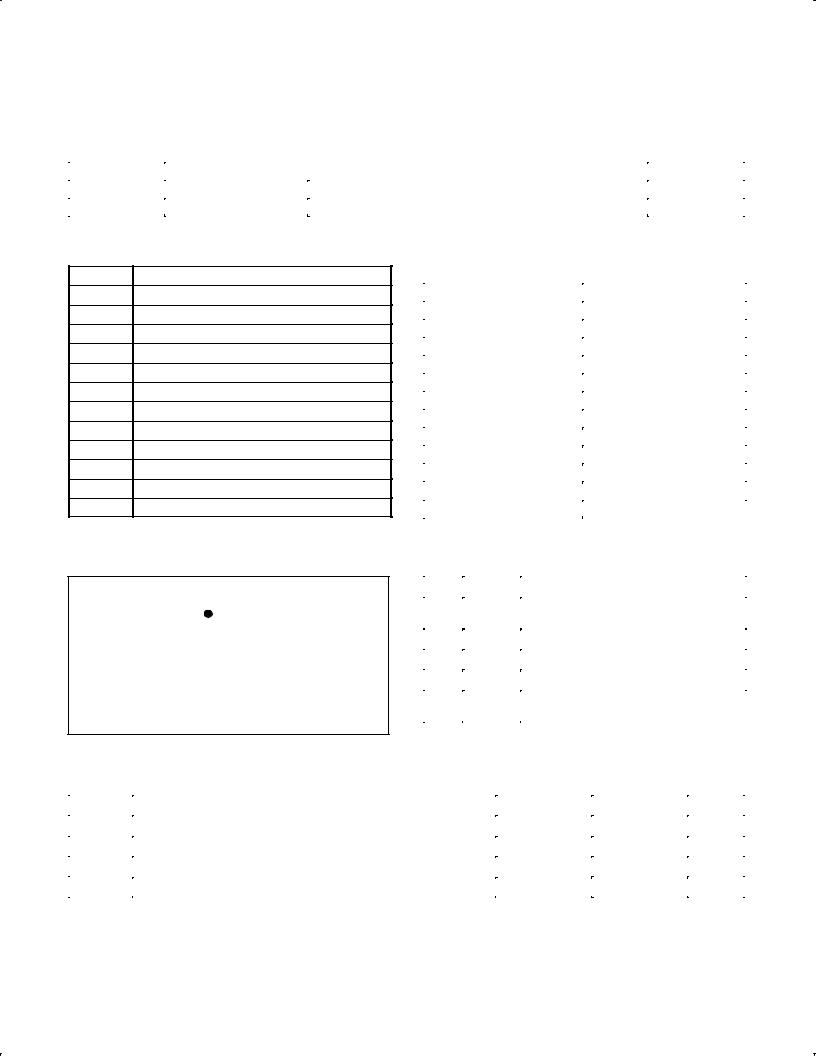

SIMPLIFIED SYSTEM DIAGRAM |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TO VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TO RESET |

|

||

|

|

|

|

|

|

|

|

|

RPU |

|

|

|

|

TERMINAL |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OF CPU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

5 |

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NE56632-XX |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

2 |

|

|

|

|

3 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SL01605

Figure 1. Simplified system diagram.

2002 Mar 25 |

2 |

853±2329 27919 |

Philips Semiconductors |

Product data |

|

|

|

|

Active-LOW system reset with adjustable delay time |

NE56632-XX |

|

|

|

|

ORDERING INFORMATION

TYPE NUMBER |

PACKAGE |

|

TEMPERATURE |

|

NAME |

DESCRIPTION |

RANGE |

||

|

||||

|

|

|||

|

|

|

|

|

NE56632-XXD |

SOT23-5 / SOT25 (SO5) |

plastic small outline package; 5 leads (see dimensional drawing) |

±20 to +75 °C |

NOTE:

The device has 12 voltage output options, indicated by the XX on the `Type number'.

XX |

VOLTAGE (Typical) |

191.9 V

202.0 V

272.7 V

282.8 V

292.9 V

303.0 V

313.1 V

424.2 V

434.3 V

444.4 V

454.5 V

464.6 V

PIN CONFIGURATION

|

|

|

|

|

TC |

1 |

|

5 |

VCC |

|

|

NE56632-XX |

|

|

SUB |

2 |

|

|

|

GND |

|

|

|

VOUT |

3 |

|

4 |

||

|

|

|

|

|

SL01604

Figure 2. Pin configuration.

MAXIMUM RATINGS

Part number marking

The package is marked with a four letter code. The first three letters designate the product. The fourth letter, represented by `x', is a date tracking code.

Part Number |

Marking |

|

|

NE56632-19D |

AKZx |

|

|

NE56632-20D |

ALAx |

|

|

NE56632-27D |

ALBx |

|

|

NE56632-28D |

ALCx |

|

|

NE56632-29D |

ALDx |

|

|

NE56632-30D |

ALEx |

|

|

NE56632-31D |

ALFx |

|

|

NE56632-42D |

ALGx |

|

|

NE56632-43D |

ALHx |

|

|

NE56632-44D |

ALJx |

|

|

NE56632-45D |

ALKx |

|

|

NE56632-46D |

ALLx |

PIN DESCRIPTION

PIN |

SYMBOL |

DESCRIPTION |

|

|

|

1 |

TC |

Delay time control; set with external |

|

|

capacitor. |

|

|

|

2 |

SUB |

Substrate. Connect to ground (GND). |

|

|

|

3 |

GND |

Ground. Negative supply. |

|

|

|

4 |

VOUT |

Reset output voltage. Active-LOW. |

5 |

VCC |

Positive supply voltage; detection threshold |

|

|

voltage input. |

SYMBOL |

PARAMETER |

MIN. |

MAX. |

UNIT |

|

|

|

|

|

VCC |

Supply voltage |

±0.3 |

+10 |

V |

Tamb |

Ambient operating temperature |

±20 |

+75 |

°C |

Tstg |

Storage temperature |

±40 |

+125 |

°C |

P |

Power dissipation |

± |

150 |

mW |

|

|

|

|

|

2002 Mar 25 |

3 |

Philips Semiconductors |

Product data |

|

|

|

|

Active-LOW system reset with adjustable delay time |

NE56632-XX |

|

|

|

|

ELECTRICAL CHARACTERISTICS

Tamb = 25 °C, unless otherwise specified.

SYMBOL |

PARAMETER |

CONDITIONS |

|

|

-XX |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

|

|

|

|

VS |

Detection threshold |

VCC = HIGH-to-LOW; RL = 4.7 kΩ; S1=ON; |

|

46 |

4.531 |

4.600 |

4.669 |

V |

|

|

|

VOL ≤ 0.4 V; |

|

|

|

|

|

|

|

|

|

|

|

45 |

4.432 |

4.500 |

4.568 |

V |

|

|

|

Test Circuit 1 (Figure 27) |

|

||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

44 |

4.334 |

4.400 |

4.466 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

4.235 |

4.300 |

4.365 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

4.137 |

4.200 |

4.263 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

3.053 |

3.100 |

3.147 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

2.955 |

3.000 |

3.045 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

2.856 |

2.900 |

2.944 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

2.758 |

2.800 |

2.842 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

2.659 |

2.700 |

2.741 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

1.970 |

2.000 |

2.030 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

1.871 |

1.900 |

1.929 |

V |

|

|

|

|

|

|

|

|

||

Vhys |

Hysteresis voltage |

RL = 4.7 kΩ; VCC = LOW-to-HIGH-to-LOW; S1 = ON; Test |

25 |

50 |

100 |

mV |

|||

|

|

Circuit 1 (Figure 27) |

|

|

|

|

|

||

VS/ T |

Detection threshold voltage |

RL = 4.7 kΩ; Tamb = ±20 °C to +75 °C; S1 = ON; |

± |

±0.01 |

± |

%/°C |

|||

|

temperature coefficient |

Test Circuit 1 (Figure 27) |

|

|

|

|

|

||

VOL |

LOW-level output voltage |

VCC1 = VS(min) ± 0.05 V; RL = 4.7 kΩ; S1 = ON; |

± |

0.2 |

0.4 |

V |

|||

|

|

Test Circuit 1 (Figure 27) |

|

|

|

|

|

||

ILO |

Output leakage current |

VCC1 = VCC2 = 10 V; S2 = ON; Test Circuit 1 (Figure 27) |

± |

± |

±0.1 |

μA |

|||

ICCL |

Supply current (ON time) |

VCC1 = VS(min) ± 0.05 V; RL = ∞ ; Test Circuit 1 (Figure 27) |

± |

5.0 |

9.0 |

μA |

|||

ICCH |

Supply current (OFF time) |

VCC1 = VS(typ)/0.85; RL = ∞ ; Test Circuit 1 (Figure 27) |

± |

3.0 |

5.0 |

μA |

|||

tPLH |

LOW-to-HIGH delay time |

CL = 100 pF; RL = 4.7 kΩ; CD = 10 nF (Note 1) |

± |

(Note 3) |

± |

ms |

|||

tPHL |

HIGH-to-LOW delay time |

CL = 100 pF; RL = 4.7 kΩ; CD = 10 nF (Note 2) |

± |

(Note 3) |

± |

μs |

|||

VOPL |

Minimum operating |

RL = 4.7 kΩ; VOL ≤ 0.4 V; S1 = ON; |

|

± |

0.65 |

0.80 |

V |

||

|

threshold voltage |

Test Circuit 1 (Figure 27) |

|

|

|

|

|

||

IOL1 |

Output current (ON Time 1) |

VO = 0.4 V; RL = 0; VCC1 = VS(min) ± 0.05 V; |

|

5 |

± |

± |

mA |

||

|

|

VCC2 = 0.4 V; S2 = ON; Test Circuit 1 (Figure 27) |

|

|

|

|

|||

IOL2 |

Output current (ON Time 2) |

VO = 0.4 V; RL = 0; VCC1 |

= VS(min) ± 0.05 V; |

|

3 |

± |

± |

mA |

|

|

|

Tamb = ±20 °C to +75 |

°C; S2 = ON; |

|

|

|

|

|

|

|

|

Test Circuit 1 (Figure 27) |

|

|

|

|

|

||

NOTES:

1.tPLH: VCC = (VS(typ) ± 0.4 V) to (VS(typ) + 0.4 V); tPLH is release delay time (Test Circuit 2, Figure 28).

2.tPHL: VCC = (VS(typ) + 0.4 V) to (VS(typ) ± 0.4 V); tPHL is assertion delay time (Test Circuit 2, Figure 28).

3.See Table 1.

Table 1. NE56632-XX series typical delay time

±XX |

tPLH |

tPHL |

46 |

195 ms |

140 μs |

|

|

|

45 |

190 ms |

140 μs |

|

|

|

44 |

185 ms |

140 μs |

|

|

|

43 |

180 ms |

140 μs |

|

|

|

42 |

175 ms |

140 μs |

|

|

|

31 |

120 ms |

120 μs |

|

|

|

30 |

115 ms |

120 μs |

|

|

|

29 |

110 ms |

120 μs |

|

|

|

28 |

105 ms |

100 μs |

|

|

|

27 |

100 ms |

100 μs |

|

|

|

20 |

65 ms |

100 μs |

|

|

|

19 |

60 ms |

100 μs |

2002 Mar 25 |

4 |

Philips Semiconductors |

Product data |

|

|

|

|

Active-LOW system reset with adjustable delay time |

NE56632-XX |

|

|

|

|

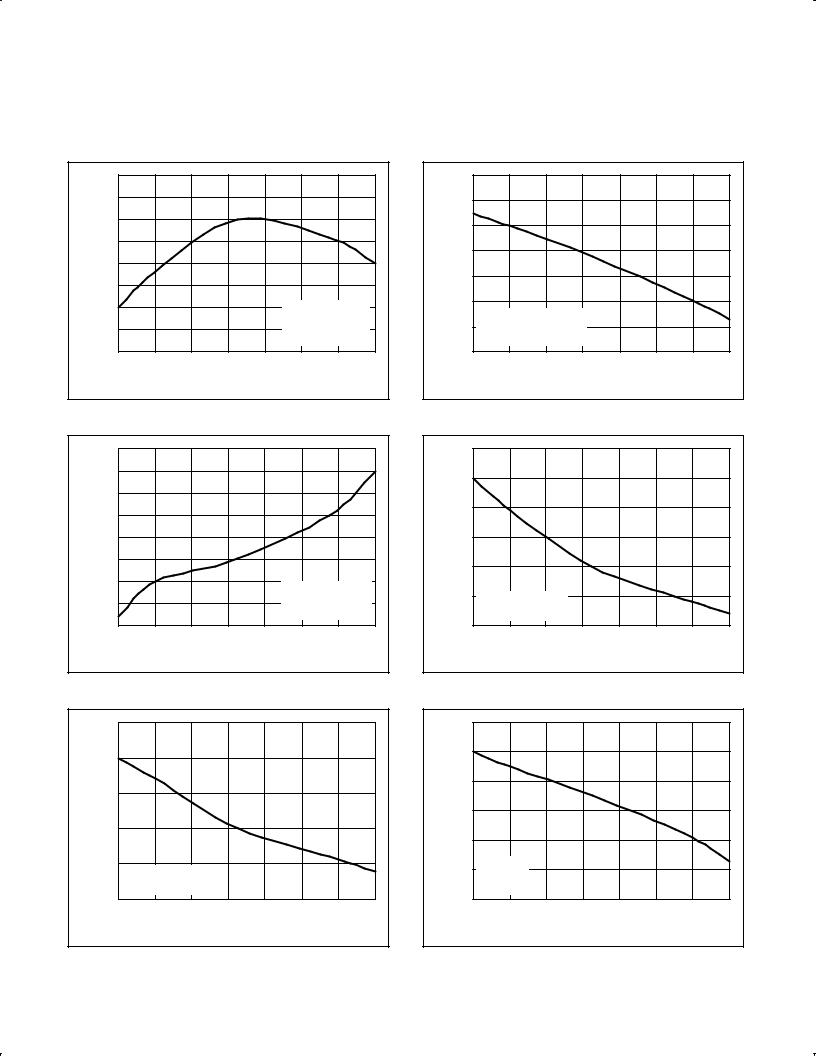

TYPICAL PERFORMANCE CURVES, NE56632-20

|

2.0050 |

|

|

|

|

|

|

|

(V) |

2.0025 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

THRESHOLD |

2.0000 |

|

|

|

|

|

|

|

1.9975 |

|

|

|

|

|

|

|

|

1.9950 |

|

|

|

|

|

|

|

|

DETECTION |

|

|

|

|

|

|

|

|

1.9925 |

|

|

|

|

|

|

|

|

1.9900 |

|

|

|

|

Test Circuit 1 |

|

|

|

, |

|

|

|

|

|

VCC = HIGH-to-LOW |

|

|

S |

|

|

|

|

|

|

||

V |

1.9875 |

|

|

|

|

RL = 4.7 kΩ |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

VOL ≤ 0.4 V |

|

|

|

1.9850 |

|

|

|

|

S1 = ON |

|

|

|

|

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

AMBIENT TEMPERATURE, Tamb (°C)

SL01620

Figure 3. Detection threshold versus temperature.

|

0.225 |

|

|

|

|

|

|

|

(V) |

0.220 |

|

|

|

|

|

|

|

VOLTAGE |

0.215 |

|

|

|

|

|

|

|

0.210 |

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

0.205 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LEVEL |

0.200 |

|

|

|

|

|

|

|

0.195 |

|

|

|

|

|

|

|

|

, LOW- |

|

|

|

|

Test Circuit 1 |

|

|

|

|

|

|

|

|

|

|

||

0.190 |

|

|

|

|

VCC1 = VS(min) ± 0.05 V |

|

||

OL |

|

|

|

|

RL = 4.7 kΩ |

|

|

|

V |

|

|

|

|

|

S1 = ON |

|

|

|

|

|

|

|

|

|

|

|

|

0.185 |

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

AMBIENT TEMPERATURE, Tamb (°C)

SL01622

Figure 5. LOW-level output voltage versus temperature.

μA) |

4.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

( |

|

|

|

|

|

|

|

|

(OFF time), |

4.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CURRENT |

3.5 |

|

|

|

|

|

|

|

3.0 |

|

|

|

|

|

|

|

|

, SUPPLY |

|

|

|

|

|

|

|

|

2.5 |

|

|

|

|

|

|

|

|

CCH |

Test Circuit 1 |

|

|

|

|

|

|

|

RL = ∞ |

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC1 = VS(typ)/0.85 |

|

|

|

|

|

||

|

2.0 |

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

AMBIENT TEMPERATURE, Tamb (°C)

SL01624

Figure 7. Supply current (OFF time) versus temperature.

|

100 |

|

|

|

|

|

|

|

|

(mV) |

90 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOLTAGE |

80 |

|

|

|

|

|

|

|

|

70 |

|

|

|

|

|

|

|

|

|

HYSTERESIS |

|

|

|

|

|

|

|

|

|

60 |

|

|

|

|

|

|

|

|

|

50 |

|

|

|

|

|

|

|

|

|

, |

|

Test Circuit 1 |

|

|

|

|

|

|

|

hys |

|

|

|

|

|

|

|

||

|

VCC = LOW-to-HIGH-to-LOW |

|

|

|

|

||||

V |

40 |

|

|

|

|

||||

|

|

RL = 4.7 kΩ |

|

|

|

|

|

|

|

|

|

S1 = ON |

|

|

|

|

|

|

|

|

30 |

|

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

|

|

|

|

|

AMBIENT TEMPERATURE, Tamb (°C) |

|

|

|||

|

|

|

|

|

|

|

|

|

SL01621 |

Figure 4. Hysteresis voltage versus temperature.

|

9 |

|

|

|

|

|

|

|

|

(μA) |

8 |

|

|

|

|

|

|

|

|

(ON time), |

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

CURRENT |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

, SUPPLY |

5 |

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

CCL |

Test Circuit 1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

VCC1 |

= VS(min) ± 0.05 V |

|

|

|

|

|

||

I |

|

|

|

|

|

|

|||

|

3 |

RL = ∞ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

|

|

|

|

|

AMBIENT TEMPERATURE, Tamb (°C) |

|

|

|||

|

|

|

|

|

|

|

|

|

SL01623 |

Figure 6. Supply current (ON time) versus temperature.

(V) |

0.9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VOLTAGE |

0.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

THRESHOLD |

0.7 |

|

|

|

|

|

|

|

|

|

0.6 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

OPERATING |

0.5 |

|

|

|

|

|

|

|

|

|

0.4 |

Test Circuit 1 |

|

|

|

|

|

|

|||

RL = 4.7 kΩ |

|

|

|

|

|

|

||||

, MIN. |

|

|

|

|

|

|

||||

|

VOL ≤ 0.4 V |

|

|

|

|

|

|

|||

|

S1 = ON |

|

|

|

|

|

|

|||

OPL |

0.3 |

|

|

|

|

|

|

|

|

|

±40 |

±20 |

0 |

20 |

40 |

60 |

80 |

100 |

|||

V |

||||||||||

AMBIENT TEMPERATURE, Tamb (°C)

SL01625

Figure 8. Min. operating threshold voltage versus temperature.

2002 Mar 25 |

5 |

Loading...

Loading...