Philips NE568AN, NE568AD, SA568AN, SA568AD Datasheet

Philips Semiconductors |

Product specification |

|

|

|

|

150MHz phase-locked loop |

NE/SA568A |

|

|

|

|

DESCRIPTION

The NE568A is a monolithic phase-locked loop (PLL) which operates from 1Hz to frequencies in excess of 150MHz and features an extended supply voltage range and a lower temperature coefficient of the VCO center frequency in comparison with its predecessor, the NE 568. The NE568A is function and pin-compatible with the NE568, requiring only minor changes in peripheral circuitry (see Figure 3). Temperature compensation network is different, no resistor on Pin 12, needs to be grounded and

Pin 13 has a 3.9kΩ resistor to ground. Timing cap, C2, is different and for 70MHz operation with temperature compensation network should be 16pF, not 34pF as was used in the NE568. The NE568A has the following improvements: ESD protected; extended VCC range from 4.5V to 5.5V; operating temperature range -55 to 125°C

(see Signetics Military 568A data sheet); less layout sensitivity; and lower TC of VCO (center frequency). The integrated circuit consists of a limiting amplifier, a current-controlled oscillator (ICO), a phase detector, a level shift circuit, V/I and I/V converters, an output buffer, and bias circuitry with temperature and frequency compensating characteristics. The design of the NE568A is particularly well-suited for demodulation of FM signals with extremely large deviation in systems which require a highly linear output. In satellite receiver applications with a 70MHz IF, the NE568A will demodulate ±20% deviations with less than 1.0% typical non-linearity. In addition to high linearity, the circuit has a loop filter which can be configured with series or shunt elements to optimize loop dynamic performance. The NE568A is available in 20-pin dual in-line and

20-pin SO (surface mounted) plastic packages.

FEATURES

•Operation to 150MHz

•High linearity buffered output

PIN CONFIGURATION

D, N Packages

|

|

|

|

|

|

|

VCC2 |

1 |

|

|

|

20 |

LF1 |

|

|

|

|

|

|

|

GND2 |

2 |

|

|

|

19 |

LF2 |

|

|

|

|

|

|

|

GND1 |

3 |

|

|

|

18 |

LF3 |

|

|

|

|

|

|

|

TCAP1 |

4 |

|

|

|

17 |

LF4 |

|

|

|

|

|

|

|

TCAP2 |

5 |

|

|

|

16 |

FREQ ADJ |

|

|

|

|

|

|

|

GND1 |

6 |

|

|

|

15 |

OUTFILT |

|

|

|

|

|

|

|

VCC1 |

7 |

|

|

|

14 |

VOUT |

|

|

|

|

|

||

|

|

|

|

|

||

REFBYP |

8 |

|

|

|

13 |

TCADJ2 |

|

|

|

|

|

|

|

PNPBYP |

9 |

|

|

|

12 |

TCADJ1 |

|

|

|

|

|

|

|

INPBYP |

10 |

|

|

|

11 |

VIN |

|

|

|

|

|

|

|

|

|

TOP VIEW |

|

SR01037 |

||

Figure 1. Pin Configuration

•Series or shunt loop filter component capability

•External loop gain control

•Temperature compensated

•ESD protected1

APPLICATIONS

•Satellite receivers

•Fiber optic video links

•VHF FSK demodulators

•Clock Recovery

ORDERING INFORMATION

DESCRIPTION |

TEMPERATURE RANGE |

ORDER CODE |

DWG # |

|

|

|

|

20-Pin Plastic Small Outline Large (SOL) Package |

0 to +70°C |

NE568AD |

SOT163-1 |

|

|

|

|

20-Pin Plastic Dual In-Line Package (DIP) |

0 to +70°C |

NE568AN |

SOT146-1 |

|

|

|

|

20-Pin Plastic Small Outline Large (SOL) Package |

-40 to +85°C |

SA568AD |

SOT163-1 |

|

|

|

|

20-Pin Plastic Dual In-Line Package (DIP) |

-40 to +85°C |

SA568AN |

SOT146-1 |

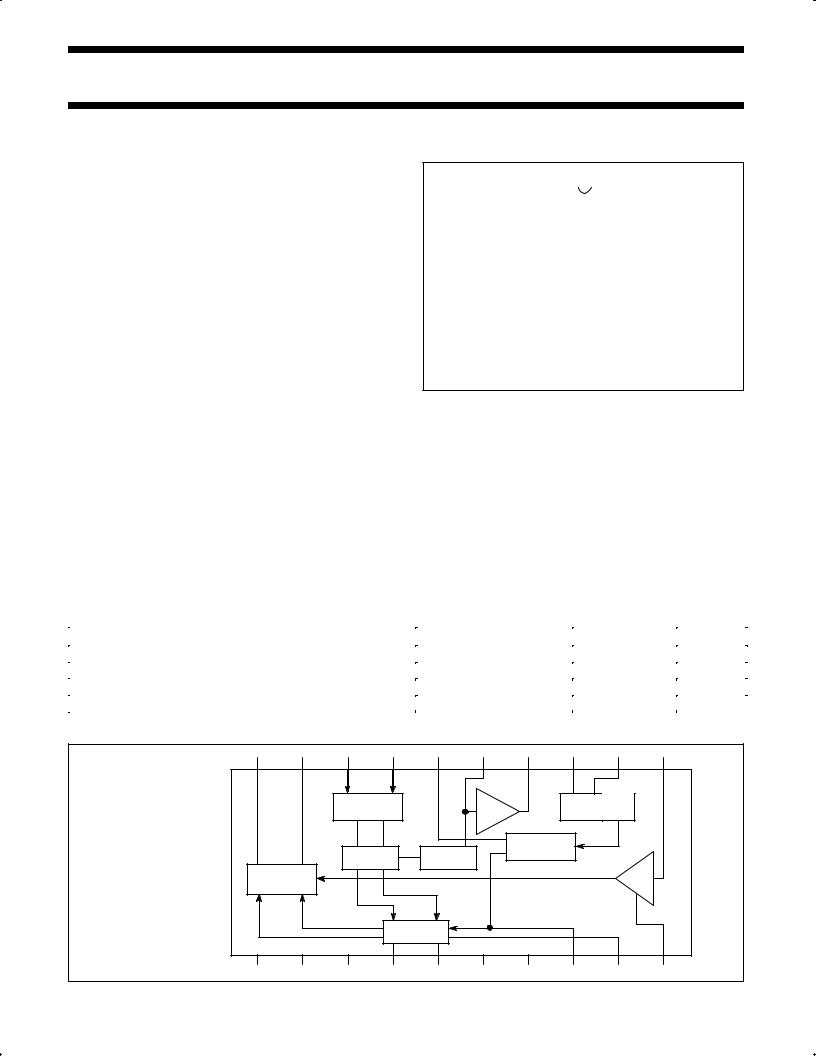

BLOCK DIAGRAM

NOTE:

Pins 4 and 5 can tolerate

1000V only, and all other pins, greater than 2000V for ESD (human body model).

LF1 |

LF2 |

LF3 |

LF4 |

FREQ ADJ |

OUTFILT |

VOUT |

TCADJ2 |

TCADJ1 |

VIN |

|

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

|

|

|

LEVEL SHIFT |

|

OUT |

|

TCADJ |

BIAS |

|

|

|

|

|

|

|

|

BUF |

|

|

|

|

|

|

|

|

V/I |

I/V |

|

LEVEL SHIFT |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

CONVERTER |

CONVERTER |

|

|

|

|

|

||

PHASE |

|

|

|

|

|

|

AMP |

|

|

|

DETECTOR |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

ICO |

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

VCC2 |

GND2 |

GND1 |

TCAP1 |

TCAP2 |

GND1 |

VCC1 |

REFBYP |

PNPBYP |

INPBYP |

SR01038 |

Figure 2. Block Diagram

1996 Feb 1 |

1 |

853-1558 16328 |

Philips Semiconductors |

Product specification |

|

|

|

|

150MHz phase-locked loop |

NE/SA568A |

|

|

|

|

ABSOLUTE MAXIMUM RATINGS

SYMBOL |

PARAMETER |

RATING |

UNITS |

|

|

|

|

VCC |

Supply voltage |

6 |

V |

TJ |

Junction temperature |

+150 |

°C |

TSTG |

Storage temperature range |

-65 to +150 |

°C |

PDMAX |

Maximum power dissipation |

400 |

mW |

θJA |

Thermal resistance |

80 |

°C/W |

ELECTRICAL CHARACTERISTICS

The elctrical characteristics listed below are actual tests (unless otherwise stated) performed on each device with an automatic IC tester prior to shipment. Performance of the device in automated test set-up is not necessarily optimum. The NE568A is

layout-sensitive. Evaluation of performance for correlation to the data sheet should be done with the circuit and layout of Figures 3, 4, and 5 with the evaluation unit soldered in place. (Do not use a socket!)

DC ELECTRICAL CHARACTERISTICS

VCC = 5V; TA = 25°C; fO = 70MHz, Test Circuit Figure 3, fIN = -20dBm, R4 = 3.9kΩ, unless otherwise specified.

|

|

|

|

LIMITS |

|

|

|

|

|

|

|

|

|

SYMBOL |

PARAMETER |

TEST CONDITIONS |

|

NE/SA568A |

|

UNITS |

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

VCC |

Supply voltage |

|

4.5 |

5 |

5.5 |

V |

ICC |

Supply current |

|

|

54 |

70 |

mA |

AC ELECTRICAL CHARACTERISTICS

|

|

|

|

|

LIMITS |

|

|

|

|

|

|

|

|

|

|

SYMBOL |

PARAMETER |

TEST CONDITIONS |

|

NE/SA568A |

|

UNITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

|

f |

Maximum oscillator operating frequency3 |

|

|

150 |

|

|

MHz |

OSC |

|

|

|

|

|

|

|

|

Input signal level |

|

|

50 |

|

2000 |

mVP-P |

|

|

|

|

±201 |

|

+10 |

dBm |

BW |

Demodulated bandwidth |

|

|

|

fO/7 |

|

MHz |

|

Non-linearity5 |

Dev = ±20%, Input = -20dBm |

|

1.0 |

4.0 |

% |

|

|

Lock range2 |

Input = -20dBm |

±25 |

±35 |

|

% of f |

|

|

|

|

|

|

|

|

O |

|

Capture range2 |

Input = -20dBm |

±20 |

±30 |

|

% of f |

|

|

|

|

|

|

|

|

O |

|

TC of fO |

|

Figure 3 |

|

100 |

|

ppm/°C |

RIN |

Input resistance4 |

|

|

1 |

|

|

kΩ |

|

Output impedance |

|

|

|

6 |

|

Ω |

|

|

|

|

|

|

|

|

|

Demodulated VOUT |

Dev = ±20% of fO measured at |

0.40 |

0.52 |

|

VP-P |

|

|

|

Pin 14 |

|

||||

|

AM rejection |

VIN = -20dBm (30% AM) |

|

50 |

|

dB |

|

|

|

referred to ±20% deviation |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Distribution6 |

Centered at 70MHz, R2 = |

|

|

|

|

|

f |

1.2kΩ, C |

= 16pF, R = 3.9kΩ |

-15 |

0 |

+15 |

% |

|

O |

|

2 |

4 |

|

|

|

|

|

|

(C2 + CSTRAY = 20pF) |

|

|

|

|

|

fO |

Drift with supply |

4.5V to 5.5V |

|

2 |

|

%/V |

|

NOTE:

1.Signal level to assure all published parameters. Device will continue to function at lower levels with varying performance.

2.Limits are set symmetrical to fO. Actual characteristics may have asymmetry beyond the specified limits.

3.Not 100% tested, but guaranteed by design.

4.Input impedance depends on package and layout capacitances. See Figures 6 and 5.

5.Linearity is tested with incremental changes in inupt frequency and measurement of the DC output voltage at Pin 14 (VOUT). Non-linearity is then calculated from a straight line over the deviation range specified.

6.Free-running frequency is measured as feedthrough to Pin 14 (VOUT) with no input signal applied.

1996 Feb 1 |

2 |

Philips Semiconductors |

Product specification |

|

|

|

|

150MHz phase-locked loop |

NE/SA568A |

|

|

|

|

|

|

|

1 |

VCC2 |

LF1 |

20 |

|

|

|

C1 |

|

|

|

|

|

|

|

||

|

|

|

2 |

GND2 |

LF2 |

19 |

|

|

|

|

|

|

|

|

|

|

C10 |

||

|

|

|

|

|

|

|

|

R1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

GND1 |

LF3 |

18 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

C9 |

|

|

|

|

4 |

TCAP1 |

LF4 |

17 |

|

|

|

|

|

|

|

|

|

|

|

||

|

RFC1 |

C2 |

|

|

16 |

R2 |

|

|

|

|

|

|

5 |

TCAP2 |

FREQADJ |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

6 |

GND1 |

OUTFILT |

15 |

C11 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

C8 |

|

|

|

C12 |

|

VOUT |

|

|

|

7 |

|

|

14 |

|

R3 |

|

|

|

|

|

VCC1 |

VOUT |

|

|

|

|

|

|

|

C3 |

|

|

|

|

R4 |

|

VCC |

|

|

8 |

REFBYP |

TCADJ2 |

13 |

|

|

|

|

RFC2 |

|

|

|

|

|

|||

C5 |

C6 |

|

|

|

|

|

|||

C4 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

PNPBYP |

TCADJ1 |

12 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

10 |

|

|

11 |

C13 |

|

VIN |

|

|

|

INPBYP |

VIN |

|

|

|||

|

|

|

C7 |

|

|

|

|

||

|

|

|

|

|

|

|

|

R5 |

|

|

|

|

|

|

|

|

|

|

|

SR01039

Figure 3. Test Circuit for AC Parameters

FUNCTIONAL DESCRIPTION

The NE568A is a high-performance phase-locked loop (PLL). The circuit consists of conventional PLL elements, with special circuitry for linearized demodulated output, and high-frequency performance.

The process used has NPN transistors with fT > 6GHz. The high gain and bandwidth of these transistors make careful attention to layout and bypass critical for optimum performance. The performance of the PLL cannot be evaluated independent of the layout. The use of the application layout in this data sheet and surface-mount capacitors are highly recommended as a starting point.

The input to the PLL is through a limiting amplifier with a gain of 200. The input of this amplifier is differential (Pins 10 and 11). For single-ended applications, the input must be coupled through a

DC-blocking capacitor with low impedance at the frequency of interest. The single-ended input is normally applied to Pin 11 with Pin 10 AC-bypassed with a low-impedance capacitor. The input impedance is characteristically slightly above 500Ω. Impedance match is not necessary, but loading the signal source should be avoided. When the source is 50 or 75Ω, a DC-blocking capacitor is usually all that is needed.

Input amplification is low enough to assure reasonable response time in the case of large signals, but high enough for good AM rejection. After amplification, the input signal drives one port of a multiplier-cell phase detector. The other port is driven by the current-controlled oscillator (ICO). The output of the phase comparator is a voltage proportional to the phase difference of the input and ICO signals. The error signal is filtered with a low-pass filter to provide a DC-correction voltage, and this voltage is converted to a current which is applied to the ICO, shifting the frequency in the direction which causes the input and ICO to have a 90° phase relationship.

The oscillator is a current-controlled multivibrator. The current control affects the charge/discharge rate of the timing capacitor. It is common for this type of oscillator to be referred to as a

voltage-controlled oscillator (VCO), because the output of the phase comparator and the loop filter is a voltage. To control the frequency of an integrated ICO multivibrator, the control signal must be conditioned by a voltage-to-current converter. In the NE568A, special circuitry predistorts the control signal to make the change in frequency a linear function over a large control-current range.

The free-running frequency of the oscillator depends on the value of the timing capacitor connected between Pins 4 and 5. The value of the timing capacitor depends on internal resistive components and current sources. When R2 = 1.2kΩ and R4 = 0Ω, a very close approximation of the correct capacitor value is:

C * 0.0014 F fO

where

C * C2 CSTRAY

The temperature-compensation resistor, R4, affects the actual value of capacitance. This equation is normalized to 70MHz. See 10 for correction factors.

The loop filter determines the dynamic characteristics of the loop. In most PLLs, the phase detector outputs are internally connected to the ICO inputs. The NE568A was designed with filter output to input connections from Pins 20 (φ DET) to 17 (ICO), and Pins 19 (φ DET) to 18 (ICO) external. This allows the use of both series and shunt loop-filter elements. The loop constratints are:

KO 0.12V Radian (Phase Detector Constant)

KO 4.2 109 Radians (ICO Constant) at 70MHz

V±sec

The loop filter determines the general characteristics of the loop. Capacitors C9, C10, and resistor R1, control the transient output of the phase detector. Capacitor C9 suppresses 70MHz feedthrough by interaction with 100Ω load resistors internal to the phase detector.

1996 Feb 1 |

3 |

Loading...

Loading...