Samsung K9F2808U0B-YIB0, K9F2808U0B-VCB0, K9F2808U0B-DIB0, K9F2808U0B-DCB0, K9F2808Q0B-DIB0 Datasheet

...

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

Document Title

16M x 8 Bit NAND Flash Memory

Revision History

Revision No. |

History |

Draft Date |

Remark |

0.0 |

Initial issue. |

May 28’th 2001 |

Advance |

0.1 |

K9F2808U0B(3.3V device)’s qualification is finished |

Jun. 30th 2001 |

|

0.2K9F2808Q0B (1.8V device)

|

- Changed typical read operation current (Icc1) from 8mA to 5mA |

Jul. 30th 2001 |

K9F2808Q0B |

||||

|

- Changed typical program operation current (Icc2) from 8mA to 5mA |

|

: Preliminary |

||||

|

- Changed typical erase operation current (Icc3) from 8mA to 5mA |

|

|

||||

|

- Changed typical program time(tPROG) from 200us to 300us |

|

|

||||

|

|

|

|

|

|

||

|

- Changed ALE to |

RE |

Delay (ID read, tAR1) from 100ns to 20ns |

|

|

||

|

- Changed CLE hold time(tCLH) from 10ns to 15ns |

|

|

||||

|

- Changed CE hold time(tCH) from 10ns to 15ns |

|

|

||||

|

- Changed ALE hold time(tALH) from 10ns to 15ns |

|

|

||||

|

- Changed Data hold time(tDH) from 10ns to 15ns |

|

|

||||

|

- Changed CE Access time(tCEA) from 45ns to 60ns |

|

|

||||

|

- Changed Read cycle time(tRC) from 50ns to 70ns |

|

|

||||

|

- Changed Write Cycle time(tWC) from 50ns to 70ns |

|

|

||||

|

- Changed RE Access time(tREA) from 35ns to 40ns |

|

|

||||

|

|

|

|

||||

|

- Changed |

RE |

High Hold time(tREH) from 15ns to 20ns |

|

|

||

|

- Changed WE High Hold time(tWH) from 15ns to 20ns |

|

|

||||

0.3 |

1. Device Code is changed |

|

|

||||

- TBGA package information : ’B’ --> ’D’ |

|

|

|

Aug. 23th 2001 |

|||

ex) K9F2808Q0B-BCB0 ,BIB0 |

--> K9F2808Q0B-DCB0,DIB0 |

|

|

||||

K9F2808U0B-BCB0 ,BIB0 |

--> K9F2808Q0B-DCB0,DIB0 |

|

|

||||

2. VIH ,VIL of K9F2808Q0B(1.8 device) is changed |

|

|

|

||||

|

|

|

(before revision) |

|

|

|

|

|

|

|

|

|

|

|

|

Input High Voltage |

VIH |

I/O pins |

VccQ-0.4 |

|

VccQ |

|

|

|

|

|

|

|

|

||

Except I/O pins |

VCC-0.4 |

- |

VCC |

|

|||

|

|

|

|||||

|

|

|

|

|

|

|

|

Input Low Voltage, |

V IL |

|

- |

0 |

- |

0.4 |

|

All inputs |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(after |

revision) |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O pins |

VccQ-0.4 |

|

VccQ |

|

|

|

|

|

+0.3 |

|

|||

Input High Voltage |

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

||

Except I/O pins |

VCC-0.4 |

- |

VCC |

|

|||

|

|

|

|||||

|

|

+0.3 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Low Voltage, |

V IL |

|

- |

-0.3 |

- |

0.4 |

|

All inputs |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site. http://www.intl.samsungsemi.com/Memory/Flash/datasheets.html

The attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near you.

1

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

Revision History

Revision No. History

0.41. IOL(R/B) of 1.8V device is changed. -min. Value: 7mA -->3mA

-typ. Value: 8mA -->4mA

2.AC parameter is changed. tRP(min.) : 30ns --> 25ns

0.51. Parameters are changed in 1.8V part(K9F2808Q0B) .

-tCH is changed from 15ns to 20ns

-tCLH is changed from 15ns to 20ns

-tALH is changed from 15ns to 20ns

-tDH is changed from 15ns to 20ns

0.61. Parameters are changed in 1.8V part(K9F2808Q0B) .

-tRP is changed from 25ns to 35ns

-tWB is changed from 100ns to 150ns

-tREA is changed from 40ns to 45ns

Draft Date |

Remark |

Nov 5th 2001 |

Preliminary |

Feb 15th 2002

May 3rd 2002

Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site. http://www.intl.samsungsemi.com/Memory/Flash/datasheets.html

The attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near you.

2

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

16M x 8 Bit Bit NAND Flash Memory

PRODUCT LIST

Part Number |

Vcc Range |

Organization |

PKG Type |

|

|

|

|

|

|

K9F2808Q0B-D |

1.7 ~ 1.9V |

|

TBGA |

|

|

|

|

|

|

K9F2808U0B-Y |

|

X8 |

TSOP1 |

|

|

2.7 ~ 3.6V |

|

||

K9F2808U0B-D |

TBGA |

|||

|

||||

|

|

|

|

|

K9F2808U0B-V |

|

|

WSOP1 |

FEATURES

∙ Voltage Supply |

∙ Command/Address/Data Multiplexed I/O Port |

|

- K9F2808Q0B : 1.7~1.9V |

∙ Hardware Data Protection |

|

- K9F2808U0B : 2.7 ~ 3.6 V |

- Program/Erase Lockout During Power Transitions |

|

∙ Organization |

∙ Reliable CMOS Floating-Gate Technology |

|

- Memory Cell Array : (16M + 512K)bit x 8bit |

- Endurance : 100K Program/Erase Cycles |

|

- Data Register : (512 + 16)bit x8bit |

- Data Retention : 10 Years |

|

∙ Automatic Program and Erase |

∙ Command Register Operation |

|

- Page Program : (512 + 16)Byte |

∙ Package |

|

- Block Erase : (16K + 512)Byte |

- K9F2808U0B-YCB0/YIB0 : |

|

∙ 528-Byte Page Read Operation |

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) |

|

- Random Access : 10μs(Max.) |

- K9F2808X0B-DCB 0/ DIB0 |

|

- Serial Page Access |

63Ball TBGA ( 9 x 11 /0.8mm pitch , Width 1.0 mm) |

|

- K9F2808Q0B : 70ns |

- K9F2808U0B-VCB0/VIB0 |

|

- K9F2808U0B : 50ns |

48 - Pin WSOP I (12X17X0.7mm) |

|

∙ Fast Write Cycle Time |

* K9F2808U0B-V(WSOPI ) |

is the same device as |

- Program Time |

K9F2808U0B-Y(TSOP1) |

except package type. |

- K9F2808Q0B : 300 μs(Typ.) |

|

|

- K9F2808U0B : 200μs(Typ.) |

|

|

- Block Erase Time : 2ms(Typ.) |

|

|

GENERAL DESCRIPTION

The K9F2808X0B is a 16M(16,777,216)x8bit NAND Flash Memory with a spare 512K(524,288)x8bit. The device is offered in 1.8V or 3.3V Vcc. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation programs the 528-byte page in typical 200μs and an erase operation can be performed in typical 2ms on a 16K-byte block. Data in a page can be read out at 70ns/50ns(K9F2808Q0B:70ns, K9F2808U0B:50ns) cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write control automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even write-intensive systems can take advantage of the K9F2808X0B’s extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm.

The K9F2808X0B is suitable for use in data memory of mobile communication system to reduce not only mount area but also power consumption.

3

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

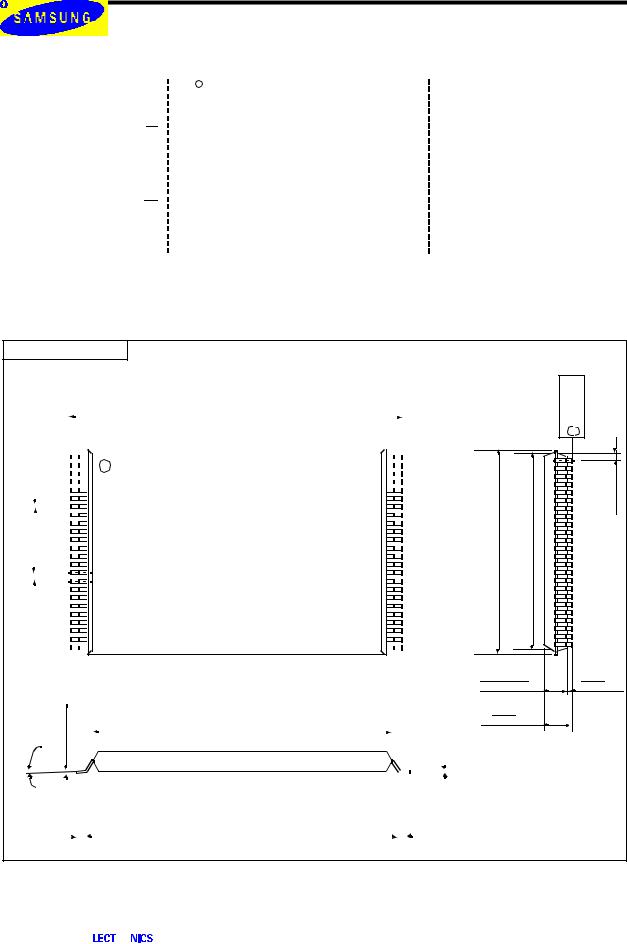

PIN CONFIGURATION (TSOP1)

K9F2808U0B-YCB0/YIB0

N.C |

|

|

1 |

48 |

|

N.C |

||

|

|

|||||||

N.C |

|

|

2 |

47 |

|

N.C |

||

|

|

|||||||

N.C |

|

3 |

46 |

|

N.C |

|||

|

|

|||||||

N.C |

|

|

4 |

45 |

|

N.C |

||

|

|

|

||||||

N.C |

|

|

5 |

44 |

|

I/O7 |

||

|

|

|||||||

GND |

|

6 |

43 |

|

I/O6 |

|||

|

|

|||||||

|

R/B |

|

|

|

7 |

42 |

|

I/O5 |

|

|

|

||||||

|

RE |

|

|

8 |

41 |

|

I/O4 |

|

|

|

|||||||

|

CE |

|

|

9 |

40 |

|

N.C |

|

|

|

|||||||

N.C |

|

|

10 |

39 |

|

N.C |

||

|

|

|||||||

N.C |

|

11 |

38 |

|

N.C |

|||

|

|

|||||||

Vcc |

|

|

12 |

37 |

|

Vcc |

||

|

|

|

||||||

Vss |

|

|

13 |

36 |

|

Vss |

||

|

|

|||||||

N.C |

|

14 |

35 |

|

N.C |

|||

|

|

|||||||

N.C |

|

|

15 |

34 |

|

N.C |

||

|

|

|

||||||

CLE |

|

|

16 |

33 |

|

N.C |

||

|

|

|||||||

ALE |

|

|

17 |

32 |

|

I/O3 |

||

|

|

|||||||

WE |

|

|

18 |

31 |

|

I/O2 |

||

|

|

|

||||||

WP |

|

19 |

30 |

|

I/O1 |

|||

|

|

|||||||

N.C |

|

|

20 |

29 |

|

I/O0 |

||

|

|

|

||||||

N.C |

|

|

21 |

28 |

|

N.C |

||

|

|

|||||||

N.C |

|

22 |

27 |

|

N.C |

|||

|

|

|||||||

N.C |

|

|

23 |

26 |

|

N.C |

||

|

|

|

||||||

N.C |

|

|

24 |

25 |

|

N.C |

||

|

|

|||||||

|

|

|

||||||

PACKAGE DIMENSIONS

48-PIN LEAD PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

48 - TSOP1 - 1220F

|

|

|

|

|

|

20.00± 0 . 2 0 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

0.787± 0.008 |

|

|

|

|

|

|

|

|

||||||

.07+0 3.00- |

03.0+0 00.0-1 |

|

#1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

#48 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

0.20 |

0 .00 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.50 |

0.0 197 |

|

|

#24 |

|

|

|

|

|

|

#25 |

|

|

TYP |

18.40± 0.10 |

|

|

.07+05 |

.0305 |

|

||||||

|

|

3.00+0 01.00- |

||||||||||

|

|

|

|

|

|

|

|

|

|

|||

0 .25 |

|

0.010 |

|

0.724± 0.004 |

|

|

0.125 |

0.005 |

||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|||||||

0~8¡Æ |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Unit :mm/Inch

|

MAX |

|

0.10 |

|

0.004 |

|

|

|

|

) |

|||

0 .25 |

|

0.010 |

|

|

|||

( |

|||

MAX |

|

|

||

12.00 |

0.472 |

|||

12.40 |

0.488 |

|||

|

|

|||

|

|

|||

1.00± 0 |

. 0 5 |

0.05 |

0.039 ±0 |

.002 |

0.002 MIN |

1.20 |

|

|

0.047 MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.45~0.75 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.50 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

( |

) |

|

|||||||||||

|

|

0.018~0.030 |

|

|

|

|

|

|

|

|

|

|

|

0.020 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

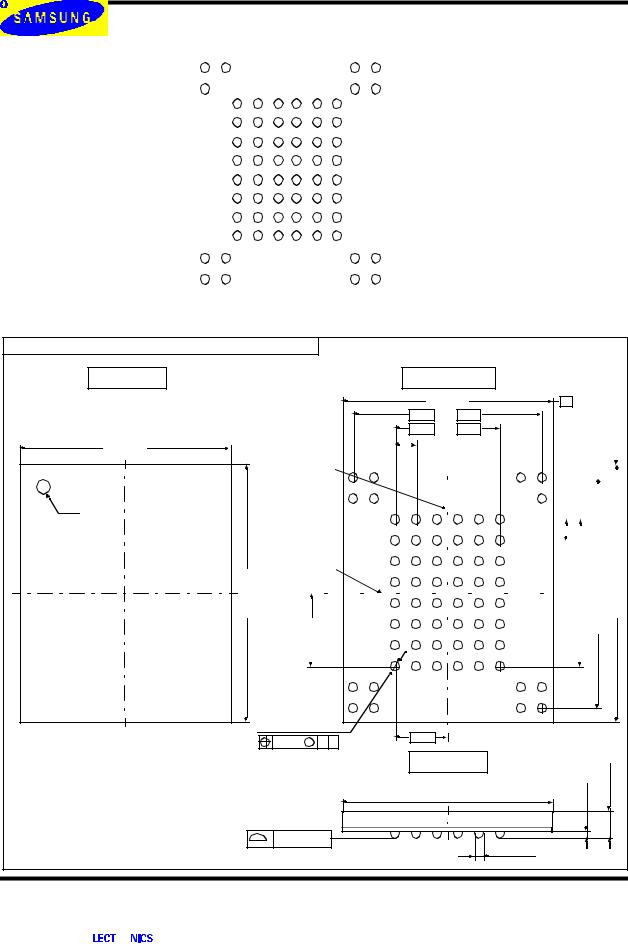

PIN CONFIGURATION (TBGA)

K9F2808X0B-DCB0/DIB0

DNU DNU |

|

|

|

|

DNU DNU |

DNU |

|

|

|

|

DNU DNU |

/WP |

ALE |

NC |

/CE |

/WE |

R/B |

NC |

/RE |

CLE NC |

NC |

NC |

|

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

NC |

I/O0 |

NC |

NC |

NC |

Vcc |

NC |

I/O1 |

NC |

VccQ I/O5 |

I/O7 |

|

Vss |

I/O2 |

I/O3 |

I/O4 |

I/O6 |

Vss |

DNU DNU |

|

|

|

|

DNU DNU |

DNU DNU |

|

|

|

|

DNU DNU |

|

|

|

|

|

|

(Top View)

PACKAGE DIMENSIONS

63-Ball TBGA (measured in millimeters)

Top View

9.00±0.10 |

#A1 |

11.00±0.10 |

Bottom View |

|

|

9.00 ±0.10 |

A |

|

0.80 |

x9= 7.20 |

|

0.80 |

x5= 4.00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

(Datum A) |

|

|

|

6 5 |

4 |

3 2 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.80 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

(Datum B) |

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.60 |

|

8.80 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x7= |

|

x11=0.80 |

11.00±0. |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

2.80 |

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.80 |

|

|

||||||||||||||

|

|

|

|

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

63- 0.45 ±0.05 |

2.00 |

|

|

|

0.20 M A B |

|

|

|

|

|

|

|

|

|

|

Side View |

±0.05 |

±0.10 |

|

|

|

|

||

|

9.00 |

±0.10 |

0.32 |

0.90 |

|

|

|

||

0.08MAX |

|

|

0.45±0.05 |

|

|

|

|

|

|

5

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

PIN CONFIGURATION (WSOP1)

K9F2808U0B-VCB0/VIB0

N.C |

|

1 |

48 |

|

N.C |

||

N.C |

|

2 |

47 |

|

N.C |

||

DNU |

|

3 |

46 |

|

DNU |

||

|

|

||||||

N.C |

|

4 |

45 |

|

N.C |

||

N.C |

|

5 |

44 |

|

I/O7 |

||

|

|

||||||

N.C |

|

|

6 |

43 |

|

I/O6 |

|

R/B |

|

7 |

42 |

|

I/O5 |

||

|

RE |

|

|

8 |

41 |

|

I/O4 |

|

|

|

|||||

|

CE |

|

9 |

40 |

|

N.C |

|

DNU |

|

10 |

39 |

|

DNU |

||

N.C |

|

11 |

38 |

|

N.C |

||

|

|

||||||

Vcc |

|

12 |

37 |

|

Vcc |

||

Vss |

|

13 |

36 |

|

Vss |

||

N.C |

|

14 |

35 |

|

N.C |

||

DNU |

|

15 |

34 |

|

DNU |

||

CLE |

|

16 |

33 |

|

N.C |

||

|

|

||||||

ALE |

|

17 |

32 |

|

I/O3 |

||

WE |

|

18 |

31 |

|

I/O2 |

||

WP |

|

19 |

30 |

|

I/O1 |

||

|

|

||||||

N.C |

|

20 |

29 |

|

I/O0 |

||

N.C |

|

21 |

28 |

|

N.C |

||

DNU |

|

22 |

27 |

|

DNU |

||

N.C |

|

23 |

26 |

|

N.C |

||

N.C |

|

24 |

25 |

|

N.C |

||

|

|

|

|

|

|

|

|

PACKAGE DIMENSIONS

48-PIN LEAD PLASTIC VERY VERY THIN SMALL OUT-LINE PACKAGE TYPE (I)

48 - WSOP1 - 1217F |

Unit :mm |

|

|

#1

+0.07 |

-0 .03 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|||

0.16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

+0.0 7 |

-0.0 3 |

|

|

|

|

|

|

0 .20 |

|

|

|

|

|

|

|

0.50TY P |

|

(0.50± 0.0 6) |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

#24

15.40± 0.10

17.00 ±0.20

0.70 MAX

0.58± 0.04

#48

0 1. 0±0 0.2 1

#25

(0.1Min)

+0.0 7 5 -0 .03 5 |

|

0.10 |

0 |

° |

|

~ |

|

8 |

|

|

° |

0.45~0.75

6

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

PIN DESCRIPTION

Pin Name |

|

|

|

|

|

|

|

|

|

Pin Function |

|||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

DATA INPUTS/OUTPUTS |

|||||||||||||

I/O0 ~ I/O7 |

The I/O pins are used to input command, address and data, and to output data during read operations. The |

||||||||||||||||||

|

|

|

|

|

|

I/O pins float to high-z when the chip is deselected or when the outputs are disabled. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

COMMAND LATCH ENABLE |

|||||||||||||

CLE |

The CLE input controls the activating path for commands sent to the command register. When active high, |

||||||||||||||||||

|

|

|

|

|

|

commands are latched into the command register through the I/O ports on the rising edge of the WE signal. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

ADDRESS LATCH ENABLE |

|||||||||||||

ALE |

The ALE input controls the activating path for address to the internal address registers. Addresses are |

||||||||||||||||||

|

|

|

|

|

|

latched on the rising edge of WE with ALE high. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

CHIP ENABLE |

|||||||||||||

|

|

|

|

|

|

The |

CE |

|

|

input is the device selection control. When the device is in the Busy state, |

CE |

high is ignored, and |

|||||||

|

CE |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

the device does not return to standby mode in program or erase opertion. Regarding CE control during read |

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

operation, refer to ’Page read’ section of Device operation. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

READ ENABLE |

|||||||||||||

|

RE |

|

|

|

The |

RE |

|

input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid |

|||||||||||

|

|

|

|

|

|

tREA after the falling edge of |

RE |

which also increments the internal column address counter by one. |

|||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

WRITE ENABLE |

|||||||||||||

|

WE |

|

|

The |

W E |

|

input controls writes to the I/O port. Commands, address and data are latched on the rising edge of |

||||||||||||

|

|

|

|

|

|

the |

WE |

pulse. |

|||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

WRITE PROTECT |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

WP |

|

|

The |

WP |

|

pin provides inadvertent write/erase protection during power transitions. The internal high voltage |

||||||||||||

|

|

|

|

|

|

generator is reset when the WP pin is active low. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

READY/BUSY OUTPUT |

|||||||||||||

|

|

|

|

|

|

|

|

output indicates the status of the device operation. When low, it indicates that a program, erase or |

|||||||||||

|

|

|

|

|

|

The R/B |

|||||||||||||

|

R/B |

||||||||||||||||||

|

random read operation is in process and returns to high state upon completion. It is an open drain output and |

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

does not float to high-z condition when the chip is deselected or when outputs are disabled. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

OUTPUT BUFFER POWER |

|||||||||||||

VccQ |

VCCQ is the power supply for Output Buffer. |

||||||||||||||||||

|

|

|

|

|

|

VccQ is internally connected to Vcc, thus should be biased to Vcc. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

Vcc |

POWER |

|||||||||||||||||

|

VCC is the power supply for device. |

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|||||||||||||||||

|

Vss |

GROUND |

|||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

N.C |

NO CONNECTION |

|||||||||||||||||

|

Lead is not internally connected. |

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

GND INPUT FOR ENABLING SPARE AREA |

|||||||||||||

GND |

To do sequential read mode including spare area , connect this input pin to Vss or set to static low state |

||||||||||||||||||

|

|

|

|

|

|

or to do sequential read mode excluding spare area , connect this input pin to Vcc or set to static high state. |

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||

DNU |

DO NOT USE |

||||||||||||||||||

Leave it disconnected. |

|||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

||||||||||||||||||

NOTE : Connect all VCC and VSS pins of each device to common power supply outputs. |

|||||||||||||||||||

7

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

Figure 1. FUNCTIONAL BLOCK DIAGRAM

VCC

VSS

A9 - A 23 |

X-Buffers |

|

|

|

|

Latches |

128M + 4M Bit |

|

|

||

|

|

|

|||

|

& Decoders |

NAND Flash |

|

|

|

|

|

ARRAY |

|

|

|

A0 - A7 |

Y-Buffers |

|

|

|

|

Latches |

|

|

|

||

|

|

|

|

||

|

& Decoders |

(512 + 16)Byte x 32768 |

|

|

|

|

|

Page Register & S/A |

|

|

|

Command |

A8 |

Y-Gating |

|

|

|

|

|

|

|

||

|

Command |

|

|

|

|

|

Register |

I/O Buffers & Latches |

|

Vcc/V CCQ |

|

|

|

|

|||

|

|

|

|

VSS |

|

CE |

Control Logic |

|

|

|

|

RE |

& High Voltage |

|

Output |

I/0 0 |

|

WE |

Generator |

Global Buffers |

|

||

Driver |

I/0 7 |

||||

|

|

|

|||

|

|

|

|

||

|

CLE ALE WP |

|

|

|

Figure 2. ARRAY ORGANIZATION

32K Pages

(=1,024 Blocks)

|

|

1 Block =32 Pages |

|

|

|

= (16K + 512) Byte |

|

|

|

1 Page = 528 Byte |

|

|

|

1 Block = 528 Bytes x 32 Pages |

|

1st half Page Register |

2nd half Page Register |

= (16K + 512) Byte |

|

1 Device = 528Byte x 32Pages x 1024 Blocks |

|||

(=256 Bytes) |

(=256 Bytes) |

||

= 132 Mbits |

|||

|

|

||

|

|

8 bit |

|

512B Byte |

16 Byte |

||

Page Register |

I/O 0 ~ I/O 7 |

||

|

|||

512 Byte |

16 Byte |

||

|

I/O 0 |

I/O 1 |

I/O 2 |

I/O 3 |

I/O 4 |

I/O 5 |

I/O 6 |

I/O 7 |

|

|

|

|

|

|

|

|

|

1st Cycle |

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

|

|

|

|

|

|

|

|

|

2nd Cycle |

A9 |

A10 |

A11 |

A12 |

A13 |

A14 |

A15 |

A16 |

|

|

|

|

|

|

|

|

|

3rd Cycle |

A17 |

A18 |

A19 |

A20 |

A21 |

A22 |

A23 |

* L |

NOTE : Column Address : Starting Address of the Register.

00h Command(Read) : Defines the starting address of the 1st half of the register. 01h Command(Read) : Defines the starting address of the 2nd half of the register. * A 8 is set to "Low" or "High" by the 00h or 01h Command.

*L must be set to "Low".

*The device ignores any additional input of address cycles than reguired.

Column Address

Row Address

(Page Address)

8

K9F2808Q0B-DCB0,DIB0 K9F2808U0B-YCB0,YIB0 K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

PRODUCT INTRODUCTION

The K9F2808X0B is a 132Mbit(138,412,032 bit) memory organized as 32,768 rows(pages) by 528 columns. Spare 16 columns are located in 512 to 527 column address. A 528-byte data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 16 cells that are serially connected like NAND structure. Each of the 16 cells resides in a different page. A block consists of the 32 pages formed by one NAND structures, totaling 8448 NAND structures of 16 cells. The array organization is shown in Figure 2. Program and read operations are executed on a page basis, while erase operation is executed on a block basis. The memory array consists of 1024 blocks, and a block is separately erasable by 16K-byte unit. It indicates that the bit by bit erase operation is prohibited on the K9F2808X0B.

The K9F2808X0B has addresses multiplexed with 8 I/O ′s. This scheme dramatically reduces pin counts and allows systems upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O ′s by bringing WE to low while CE is low. Data is latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. All commands require one bus cycle except Page Program command and Block Erase command which require two cycles: one cycle for setup and another for execution. The 16M byte physical space requires 24 addresses, thereby requiring three cycles for byte-level addressing: column address, low row address and high row address, in that order. Page Read and Page Program need the same three address cycles following required command input. In Block Erase operation, however, only two row address cycles are used. Device operations are selected by writing specific commands into command register. Table 1 defines the specific commands of the K9F2808X0B.

Table 1. COMMAND SETS

Function |

|

1st. Cycle |

2nd. Cycle |

Acceptable Command during Busy |

|

|

|

|

|

Read 1 |

|

00h/01h ( 1) |

- |

|

Read 2 |

|

50h |

- |

|

|

|

|

|

|

Read ID |

|

90h |

- |

|

|

|

|

|

|

Reset |

|

FFh |

- |

O |

Page Program |

|

80h |

10h |

|

Block Erase |

|

60h |

D0h |

|

|

|

|

|

|

Read Status |

|

70h |

- |

O |

NOTE: 1. The 00h command defines starting address of the 1st half of registers. |

|

|||

The 01h command defines starting address of the 2nd half of registers. |

|

|||

After data access on |

2nd half of register by the 01h command, start pointer is automatically moved to |

|||

1st half register(00h) on the next cycle.

Caution : Any undefined command inputs are prohibited except for above command set of Table 1.

9

Loading...

Loading...