Samsung K4S643232F-TP70, K4S643232F-TP60, K4S643232F-TI70, K4S643232F-TI60 Datasheet

K4S643232F-TI/P |

CMOS SDRAM |

2M x 32 SDRAM

512K x 32bit x 4 Banks Synchronous DRAM LVTTL(3.3V)

Industrial Temperature

86-TSOP

Revision 1.0

January 2002

Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.0 (Jan. 2002)

- 1 -

K4S643232F-TI/P |

CMOS SDRAM |

Revision History

Revision 1.0 (January 16, 2001)

• Defined DC spec.

Revision 0.0 (December 28, 2001)

•Initial draft

•Industrial Temperature (-40°c ~ 85°c )

Rev. 1.0 (Jan. 2002)

- 2 -

K4S643232F-TI/P |

CMOS SDRAM |

512K x 32Bit x 4 Banks Synchronous DRAM

FEATURES

•3.3V power supply

•LVTTL compatible with multiplexed address

•Four banks operation

•MRS cycle with address key programs

-. CAS latency ( 2 & 3)

-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)

•All inputs are sampled at the positive going edge of the system clock

•Burst read single-bit write operation

•DQM for masking

•Auto & self refresh

•15.6us refresh duty cycle(4K/64ms)

•Industrial Temperature range : -40°c ~ 85°c

GENERAL DESCRIPTION

The K4S643232F is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 524,288 words by 32 bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock. I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

ORDERING INFORMATION

Part NO. |

Max Freq. |

Interface |

Package |

|

K4S643232F-TI/P60 |

166MHz |

LVTTL |

86 |

|

|

|

TSOP(II) |

||

K4S643232F-TI/P70 |

143MHz |

|||

|

||||

|

|

|

|

* -I/P : Industrial temperature (-40°c to + 85°c)

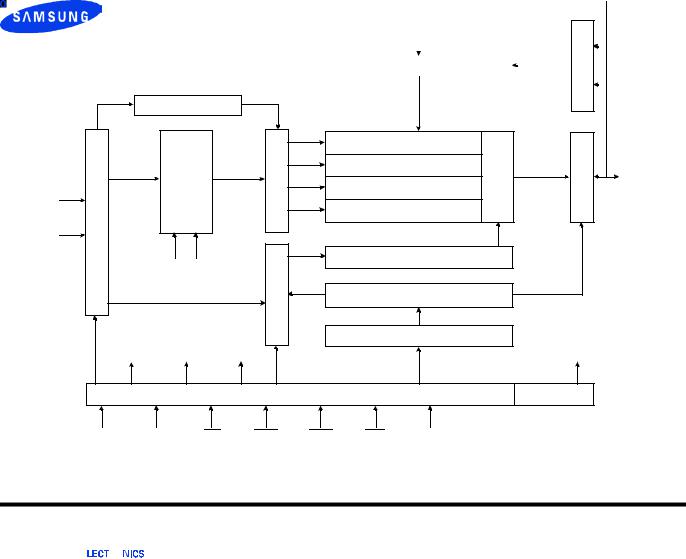

FUNCTIONAL BLOCK DIAGRAM

|

|

|

|

I/O |

|

|

LWE |

|

|

|

|

Control |

|

|

|

Data Input Register |

|

|

|

LDQM |

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bank Select

|

Address |

|

CounterRefresh |

BufferRow |

DecoderRow |

|

|

512K x 32 |

AMPSense |

BufferOutput |

|

|

|

|

|

512K x 32 |

DQi |

||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

512K x 32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

512K x 32 |

|

|

|

|

Register |

|

LRAS |

LCBR |

Buffer.Col |

|

|

|

|

|

|

ADD |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Column Decoder |

|

|

|

|

|

|

|

|

|

|

|

Latency & Burst Length |

|

|

||

|

LCKE |

|

|

|

|

|

Programming Register |

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

LRAS |

LCBR |

LWE |

LCAS |

|

LWCBR |

|

LDQM |

|

|

|

|

|

|

|

Timing Register |

|

|

|

|

|

|

|

CLK |

CKE |

|

CS |

RAS |

CAS |

WE |

DQM |

|

|

|

|

|

|

|

|

|

|

|

* Samsung Electronics reserves the right to |

|||

|

|

|

|

|

|

|

|

|

change products or specification without |

||

|

|

|

|

|

|

|

|

|

notice. |

|

|

|

|

|

|

|

|

- 3 - |

|

|

|

Rev. 1.0 (Jan. 2002) |

|

|

|

|

|

|

|

|

|

|

|

|

|

K4S643232F-TI/P |

CMOS SDRAM |

PIN CONFIGURATION (Top view)

|

VDD |

|

1 |

86 |

|

VSS |

|

|

|

|

|||||

|

|

|

|||||

|

DQ0 |

|

2 |

85 |

|

DQ15 |

|

|

|

|

|||||

|

|

|

|||||

VDDQ |

|

3 |

84 |

|

VSSQ |

||

|

|

||||||

|

|

||||||

|

DQ1 |

|

4 |

83 |

|

DQ14 |

|

|

|

|

|||||

|

|

|

|||||

|

DQ2 |

|

5 |

82 |

|

DQ13 |

|

|

|

|

|||||

|

|

|

|||||

VSSQ |

|

6 |

81 |

|

VDDQ |

||

|

|

||||||

|

|

||||||

|

DQ3 |

|

7 |

80 |

|

DQ12 |

|

|

|

|

|||||

|

|

|

|||||

|

DQ4 |

|

8 |

79 |

|

DQ11 |

|

|

|

|

|||||

|

|

|

|||||

VDDQ |

|

9 |

78 |

|

VSSQ |

||

|

|

||||||

|

|

||||||

|

DQ5 |

|

10 |

77 |

|

DQ10 |

|

|

|

|

|||||

|

|

|

|||||

|

DQ6 |

|

11 |

76 |

|

DQ9 |

|

|

|

|

|||||

|

|

|

|||||

VSSQ |

|

12 |

75 |

|

VDDQ |

||

|

|

||||||

|

|

||||||

|

DQ7 |

|

13 |

74 |

|

DQ8 |

|

|

|

|

|||||

|

|

|

|||||

|

N.C |

|

14 |

73 |

|

N.C |

|

|

|

|

|||||

|

|

|

|||||

|

VDD |

|

15 |

72 |

|

VSS |

|

|

|

|

|||||

|

|

|

|||||

DQM0 |

|

16 |

71 |

|

DQM1 |

||

|

|

||||||

|

|

||||||

|

WE |

|

|

17 |

70 |

|

N.C |

|

|

|

|||||

|

|

|

|||||

|

CAS |

|

18 |

69 |

|

N.C |

|

|

|

|

|||||

|

|

|

|||||

|

RAS |

|

19 |

68 |

|

CLK |

|

|

|

|

|||||

|

|

|

|||||

|

CS |

|

20 |

67 |

|

CKE |

|

|

|

|

|||||

|

|

|

|||||

|

N.C |

|

21 |

66 |

|

A9 |

|

|

|

|

|||||

|

|

|

|||||

|

BA0 |

|

22 |

65 |

|

A8 |

|

|

|

|

|||||

|

|

|

|||||

|

BA1 |

|

23 |

64 |

|

A7 |

|

|

|

|

|||||

|

|

|

|||||

A10/AP |

|

24 |

63 |

|

A6 |

||

|

|

||||||

|

|

||||||

|

A0 |

|

25 |

62 |

|

A5 |

|

|

|

|

|||||

|

|

|

|||||

|

A1 |

|

26 |

61 |

|

A4 |

|

|

|

|

|||||

|

|

|

|||||

|

A2 |

|

27 |

60 |

|

A3 |

|

|

|

|

|||||

|

|

|

|||||

DQM2 |

|

28 |

59 |

|

DQM3 |

||

|

|

||||||

|

|

||||||

|

VDD |

|

29 |

58 |

|

VSS |

|

|

|

|

|||||

|

|

|

|||||

|

N.C |

|

30 |

57 |

|

N.C |

|

|

|

|

|||||

|

|

|

|||||

DQ16 |

|

31 |

56 |

|

DQ31 |

||

|

|

||||||

|

|

||||||

VSSQ |

|

32 |

55 |

|

VDDQ |

||

|

|

||||||

|

|

||||||

DQ17 |

|

33 |

54 |

|

DQ30 |

||

|

|

||||||

|

|

||||||

DQ18 |

|

34 |

53 |

|

DQ29 |

||

|

|

||||||

|

|

||||||

VDDQ |

|

35 |

52 |

|

VSSQ |

||

|

|

||||||

|

|

||||||

DQ19 |

|

36 |

51 |

|

DQ28 |

||

|

|

||||||

|

|

||||||

DQ20 |

|

37 |

50 |

|

DQ27 |

||

|

|

||||||

|

|

||||||

VSSQ |

|

38 |

49 |

|

VDDQ |

||

|

|

||||||

|

|

||||||

DQ21 |

|

39 |

48 |

|

DQ26 |

||

|

|

||||||

|

|

||||||

DQ22 |

|

40 |

47 |

|

DQ25 |

||

|

|

||||||

|

|

||||||

VDDQ |

|

41 |

46 |

|

VSSQ |

||

|

|

||||||

|

|

||||||

DQ23 |

|

42 |

45 |

|

DQ24 |

||

|

|

||||||

|

|

||||||

|

VDD |

|

43 |

44 |

|

VSS |

|

|

|

|

|||||

|

|

|

|||||

|

|

|

|

|

|

|

|

86Pin TSOP (II) (400mil x 875mil) (0.5 mm Pin pitch)

Rev. 1.0 (Jan. 2002)

- 4 -

Loading...

Loading...