Samsung K4S641632D-TC-L80, K4S641632D-TC-L75, K4S641632D-TC-L70, K4S641632D-TC-L1L, K4S641632D-TC-L1H Datasheet

...

K4S641632D |

CMOS SDRAM |

64Mbit SDRAM

1M x 16Bit x 4 Banks Synchronous DRAM LVTTL

Revision 0.3

June 2000

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.3 June 2000

K4S641632D |

CMOS SDRAM |

Revision History

Revision 0.1 (May 2000)

• Changed tOH of K4S280432C-TC75/TL75 from 2.7ns to 3.0ns.

Revision 0.2 (May 2000)

• Added -70 (7.0ns) Speed.

Revision 0.3 (June 2000)

• Added -60 (6.0ns) and -55(5.5ns) Speed.

Rev. 0.3 June 2000

K4S641632D |

CMOS SDRAM |

1M x 16Bit x 4 Banks Synchronous DRAM |

|

FEATURES |

GENERAL DESCRIPTION |

•JEDEC standard 3.3V power supply

•LVTTL compatible with multiplexed address

•Four banks operation

•MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)

•All inputs are sampled at the positive going edge of the system clock

•Burst read single-bit write operation

•DQM for masking

•Auto & self refresh

•64ms refresh period (4K cycle)

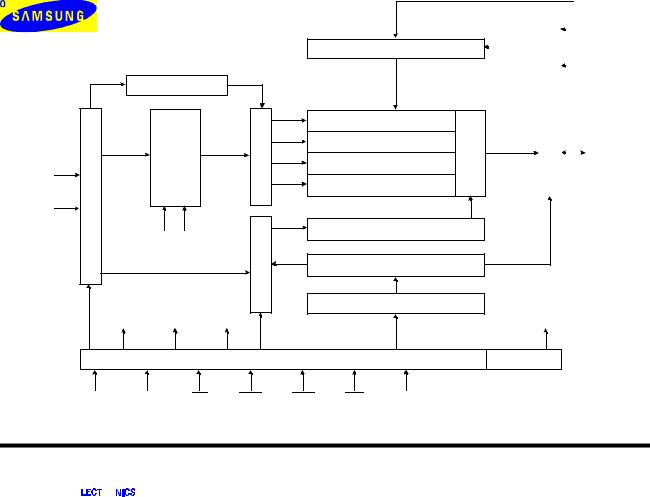

FUNCTIONAL BLOCK DIAGRAM

The K4S641632D is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 1,048,576 words by 16 bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high perfor-

mance memory system applications.

ORDERING INFORMATION

Part No. |

Max Freq. |

Interface |

Package |

|

K4S641632D-TC/L55 |

183MHz(CL=3) |

|

|

|

K4S641632D-TC/L60 |

166MHz(CL=3) |

|

|

|

K4S641632D-TC/L70 |

143MHz(CL=3) |

|

54 |

|

K4S641632D-TC/L75 |

133MHz(CL=3) |

LVTTL |

||

TSOP(II) |

||||

K4S641632D-TC/L80 |

125MHz(CL=3) |

|

||

|

|

|||

K4S641632D-TC/L1H |

100MHz(CL=2) |

|

|

|

K4S641632D-TC/L1L |

100MHz(CL=3) |

|

|

|

|

|

|

|

|

|

Data Input Register |

|

|

|

|

Bank Select |

|

|

|

|

|

||

|

Address |

|

CounterRefresh |

BufferRow |

DecoderRow |

|

|

1M x 16 |

AMPSense |

|

|

|

|

1M x 16 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1M x 16 |

|

CLK |

|

|

|

|

|

|

|

1M x 16 |

|

|

Register |

|

LRAS |

LCBR |

Buffer.Col |

|

|

|

|

ADD |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Column Decoder |

|

|

|

|

|

|

|

|

|

Latency & Burst Length |

|

|

|

LCKE |

|

|

|

|

|

Programming Register |

|

|

|

|

|

|

|

|

|

|

||

|

|

LRAS |

LCBR |

LWE |

LCAS |

|

LWCBR |

|

|

|

|

|

|

|

Timing Register |

|

|

|

|

|

CLK |

CKE |

|

CS |

RAS |

CAS |

WE |

L(U)DQM |

|

|

|

|

|

|

|

|

|

I/O |

|

|

|

|

LWE |

|

|

|

|

|

||

|

Control |

|

|

|

|

LDQM |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

|

|

|

|

DQi |

|

Buffer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LDQM

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.3 June 2000

|

K4S641632D |

|

|

|

|

|

|

CMOS SDRAM |

|||||||||||||

PIN CONFIGURATION (Top view) |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

1 |

54 |

|

|

VSS |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

DQ0 |

|

2 |

53 |

|

|

DQ15 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

VDDQ |

|

3 |

52 |

|

|

VSSQ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

DQ1 |

|

4 |

51 |

|

|

DQ14 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

DQ2 |

|

5 |

50 |

|

|

DQ13 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

VSSQ |

|

6 |

49 |

|

|

VDDQ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

DQ3 |

|

7 |

48 |

|

|

DQ12 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

DQ4 |

|

8 |

47 |

|

|

DQ11 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

VDDQ |

|

9 |

46 |

|

|

VSSQ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

DQ5 |

|

10 |

45 |

|

|

DQ10 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

DQ6 |

|

11 |

44 |

|

|

DQ9 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

VSSQ |

|

12 |

43 |

|

|

VDDQ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

DQ7 |

|

13 |

42 |

|

|

DQ8 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

VDD |

|

14 |

41 |

|

|

VSS |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

LDQM |

|

15 |

40 |

|

|

N.C/RFU |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

WE |

|

|

16 |

39 |

|

|

UDQM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

CAS |

|

17 |

38 |

|

|

CLK |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

RAS |

|

18 |

37 |

|

|

CKE |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

CS |

|

19 |

36 |

|

|

N.C |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

BA0 |

|

20 |

35 |

|

|

A11 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

BA1 |

|

21 |

34 |

|

|

A9 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

A10/AP |

|

22 |

33 |

|

|

A8 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

A0 |

|

23 |

32 |

|

|

A7 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

A1 |

|

24 |

31 |

|

|

A6 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

A2 |

|

25 |

30 |

|

|

A5 |

54Pin TSOP (II) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

A3 |

|

26 |

29 |

|

|

A4 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

(400mil x 875mil) |

||||||||||

|

|

|

|

|

|

|

|

VDD |

|

27 |

28 |

|

|

VSS |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

(0.8 mm Pin pitch) |

||||||||||

|

PIN FUNCTION DESCRIPTION |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Pin |

|

Name |

|

|

|

|

|

|

|

Input Function |

|||||||

|

|

CLK |

System clock |

|

Active on the positive going edge to sample all inputs. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Disables or enables device operation by masking or enabling all inputs except |

||||||||||

|

|

CS |

Chip select |

|

|||||||||||||||||

|

|

|

CLK, CKE and L(U)DQM |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Masks system clock to freeze operation from the next clock cycle. |

||||||||||

|

|

CKE |

Clock enable |

|

CKE should be enabled at least one cycle prior to new command. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Disable input buffers for power down in standby. |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

A0 ~ A11 |

Address |

|

Row/column addresses are multiplexed on the same pins. |

||||||||||||||||

|

|

|

Row address : RA0 ~ RA11, Column address : CA0 ~ CA7 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

BA0 ~ BA1 |

Bank select address |

|

Selects bank to be activated during row address latch time. |

||||||||||||||||

|

|

|

Selects bank for read/write during column address latch time. |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Latches row addresses on the positive going edge of the CLK with RAS low. |

||||||||||

|

|

RAS |

Row address strobe |

|

|||||||||||||||||

|

|

|

Enables row access & precharge. |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Latches column addresses on the positive going edge of the CLK with CAS low. |

||||||||||

|

|

CAS |

Column address strobe |

|

|||||||||||||||||

|

|

|

Enables column access. |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Enables write operation and row precharge. |

||||||||||

|

|

WE |

Write enable |

|

|||||||||||||||||

|

|

|

Latches data in starting from CAS, WE active. |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

L(U)DQM |

Data input/output mask |

|

Makes data output Hi-Z, tSHZ after the clock and masks the output. |

||||||||||||||||

|

|

|

Blocks data input when L(U)DQM active. |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

DQ0 ~ 15 |

Data input/output |

|

Data inputs/outputs are multiplexed on the same pins. |

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

VDD/VSS |

Power supply/ground |

|

Power and ground for the input buffers and the core logic. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

VDDQ/VSSQ |

Data output power/ground |

|

Isolated power supply and ground for the output buffers to provide improved noise |

||||||||||||||||

|

|

|

immunity. |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

N.C/RFU |

No connection |

|

This pin is recommended to be left No Connection on the device. |

||||||||||||||||

|

|

/reserved for future use |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rev. 0.3 June 2000 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Loading...

Loading...