Texas Instruments CD 74 HCT 4046 A, CD 74 HC 4046 A, CD 54 HC 4046 A INSTALLATION INSTRUCTIONS

CD54HC4046A, CD74HC4046A,

CD54HCT4046A, CD74HCT4046A

Data sheet acquired from Harris Semiconductor

SCHS204J

February 1998 - Revised December 2003

High-Speed CMOS Logic Phase-Locked Loop with VCO

[ /Title (CD74 HC404 6A, CD74 HCT40 46A) /Subject (HighSpeed CMOS

www.DataSheet4U.com

Features

•Operating Frequency Range

-Up to 18MHz (Typ) at VCC = 5V

-Minimum Center Frequency of 12MHz at VCC = 4.5V

•Choice of Three Phase Comparators

-EXCLUSIVE-OR

-Edge-Triggered JK Flip-Flop

-Edge-Triggered RS Flip-Flop

•Excellent VCO Frequency Linearity

•VCO-Inhibit Control for ON/OFF Keying and for Low Standby Power Consumption

•Minimal Frequency Drift

•Operating Power Supply Voltage Range

-VCO Section . . . . . . . . . . . . . . . . . . . . . . . . . . 3V to 6V

-Digital Section . . . . . . . . . . . . . . . . . . . . . . . . 2V to 6V

•Fanout (Over Temperature Range)

-Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

-Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

•Wide Operating Temperature Range . . . -55oC to 125oC

•Balanced Propagation Delay and Transition Times

•Significant Power Reduction Compared to LSTTL Logic ICs

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1 A at VOL, VOH

Applications

•FM Modulation and Demodulation

•Frequency Synthesis and Multiplication

•Frequency Discrimination

•Tone Decoding

•Data Synchronization and Conditioning

•Voltage-to-Frequency Conversion

•Motor-Speed Control

Description

The ’HC4046A and ’HCT4046A are high-speed silicon-gate CMOS devices that are pin compatible with the CD4046B of the “4000B” series. They are specified in compliance with JEDEC standard number 7.

The ’HC4046A and ’HCT4046A are phase-locked-loop circuits that contain a linear voltage-controlled oscillator (VCO) and three different phase comparators (PC1, PC2 and PC3). A signal input and a comparator input are common to each comparator.

The signal input can be directly coupled to large voltage signals, or indirectly coupled (with a series capacitor) to small voltage signals. A self-bias input circuit keeps small voltage signals within the linear region of the input amplifiers. With a passive low-pass filter, the 4046A forms a second-order loop PLL. The excellent VCO linearity is achieved by the use of linear op-amp techniques.

Ordering Information

|

TEMP. RANGE |

|

PART NUMBER |

(oC) |

PACKAGE |

CD54HC4046AF3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD54HCT4046AF3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD74HC4046AE |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HC4046AM |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4046AMT |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4046AM96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4046ANSR |

-55 to 125 |

16 Ld SOP |

|

|

|

CD74HC4046APWR |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HC4046APWT |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HCT4046AE |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HCT4046AM |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4046AMT |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4046AM96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

NOTE: When ordering, use the entire part number. The suffixes 96 and R denote tape and reel. The suffix T denotes a small-quantity reel of 250.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © 2003, Texas Instruments Incorporated

1

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

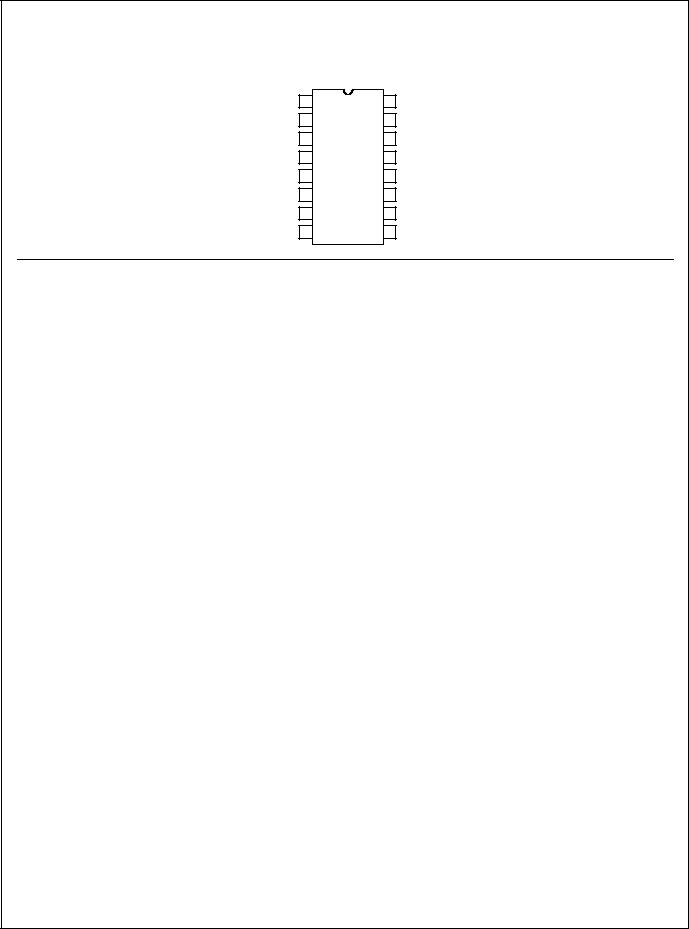

Pinout

CD54HC4046A, CD54HCT4046A (CERDIP)

CD74HC4046A (PDIP, SOIC, SOP, TSSOP)

CD74HCT4046A (PDIP, SOIC)

TOP VIEW

PCPOUT |

1 |

PC1OUT |

2 |

COMPIN |

3 |

VCOOUT |

4 |

INH |

5 |

C1A |

6 |

C1B |

7 |

GND |

8 |

16 VCC |

15 PC3OUT |

14 |

SIGIN |

13 |

PC2OUT |

12 |

R2 |

11 R1 |

10 |

DEMOUT |

9 |

VCOIN |

Functional Diagram

3 |

|

2 |

PC1OUT |

||

|

|

||||

|

|

||||

COMPIN |

|

φ |

15 |

PC3OUT |

|

|

|||||

14 |

13 |

||||

PC2OUT |

|||||

|

|

||||

|

|

||||

SIGIN |

|

|

1 |

PCPOUT |

|

|

|

||||

6 |

|

|

|||

|

|

|

|||

|

|

|

|||

C1A |

|

|

|

|

|

|

|

|

|

||

7 |

|

4 |

|

||

C1B |

|

|

|

||

|

|

|

|||

11 |

|

|

VCOOUT |

||

|

|

||||

R1 |

|

VCO |

|

|

|

|

|

|

|||

12 |

10 |

|

|||

R2 |

|

|

|

||

|

|

|

|||

9 |

|

|

DEMOUT |

||

|

|

||||

VCOIN |

|

|

|

|

|

|

|

|

|

||

5 |

|

|

|

||

INH |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Pin Descriptions

PIN NUMBER |

SYMBOL |

NAME AND FUNCTION |

|

|

|

1 |

PCPOUT |

Phase Comparator Pulse Output |

2 |

PC1OUT |

Phase Comparator 1 Output |

3 |

COMPIN |

Comparator Input |

4 |

VCOOUT |

VCO Output |

5 |

INH |

Inhibit Input |

|

|

|

6 |

C1A |

Capacitor C1 Connection A |

7 |

C1B |

Capacitor C1 Connection B |

8 |

GND |

Ground (0V) |

|

|

|

9 |

VCOIN |

VCO Input |

10 |

DEMOUT |

Demodulator Output |

11 |

R1 |

Resistor R1 Connection |

12 |

R2 |

Resistor R2 Connection |

13 |

PC2OUT |

Phase Comparator 2 Output |

14 |

SIGIN |

Signal Input |

15 |

PC3OUT |

Phase Comparator 3 Output |

16 |

VCC |

Positive Supply Voltage |

2

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

VREF

12 R2

R2

11 R1

R1

|

10 |

|

R5 |

DEMOUT |

- |

|

C1

6

7 4

7 4

C1A C1B |

OUT |

|

|

|

VCO |

+

- |

VCO |

|

-+

+

INH VCOIN

5 9

3 14

COMPIN SIGIN

SD

Q

Q

RD

CC |

|

|

|

|

UP |

||

|

|

|

|

||||

V |

|

|

|||||

Q |

|||||||

|

|

|

D |

|

|||

|

|

|

|

||||

CP Q

RD

VCC D Q

CP Q DOWN

RD

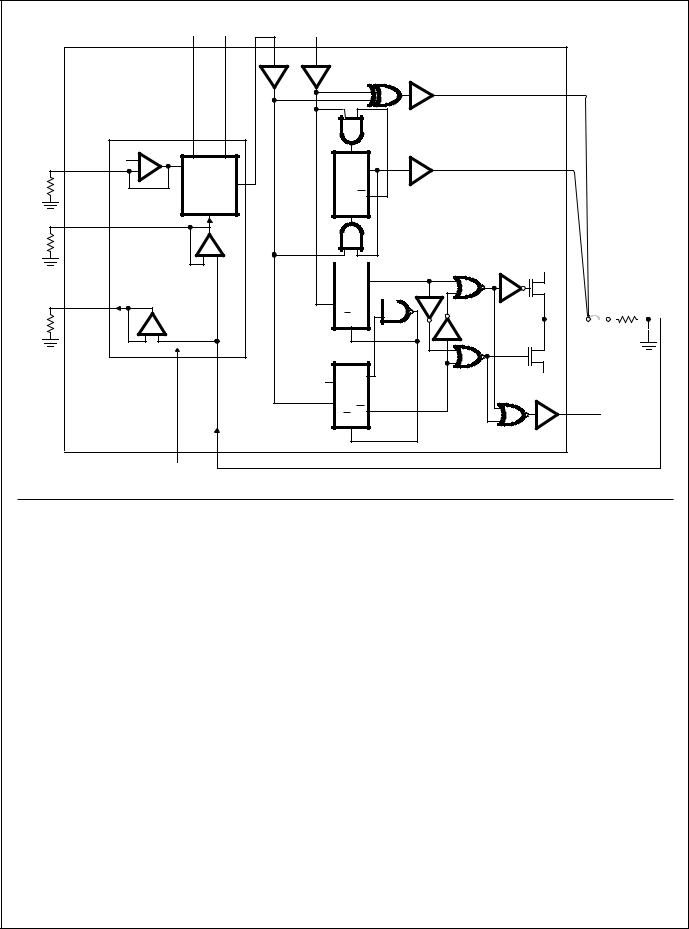

FIGURE 1. LOGIC DIAGRAM

PC1OUT 2

PC3OUT 15

VCC

p

R3

13

PC2OUT

C2

C2

n

GND

1

PCPOUT

General Description

VCO

The VCO requires one external capacitor C1 (between C1A and C1B) and one external resistor R1 (between R1 and GND) or two external resistors R1 and R2 (between R1 and GND, and R2 and GND). Resistor R1 and capacitor C1 determine the frequency range of the VCO. Resistor R2 enables the VCO to have a frequency offset if required. See logic diagram, Figure 1.

The high input impedance of the VCO simplifies the design of low-pass filters by giving the designer a wide choice of resistor/capacitor ranges. In order not to load the low-pass filter, a demodulator output of the VCO input voltage is provided at pin 10 (DEMOUT). In contrast to conventional techniques where the DEMOUT voltage is one threshold voltage lower than the VCO input voltage, here the DEMOUT

voltage equals that of the VCO input. If DEMOUT is used, a load resistor (RS) should be connected from DEMOUT to

GND; if unused, DEMOUT should be left open. The VCO output (VCOOUT) can be connected directly to the comparator input (COMPIN), or connected via a frequencydivider. The VCO output signal has a specified duty factor of 50%. A LOW level at the inhibit input (INH) enables the VCO and demodulator, while a HIGH level turns both off to minimize standby power consumption.

Phase Comparators

The signal input (SIGIN) can be directly coupled to the selfbiasing amplifier at pin 14, provided that the signal swing is between the standard HC family input logic levels. Capacitive coupling is required for signals with smaller swings.

Phase Comparator 1 (PC1)

This is an Exclusive-OR network. The signal and comparator input frequencies (fi) must have a 50% duty factor to obtain the maximum locking range. The transfer characteristic of PC1, assuming ripple (fr = 2fi) is suppressed, is:

VDEMOUT = (VCC/π ) (φ SIGIN - φ COMPIN) where VDEMOUT is the demodulator output at pin 10; VDEMOUT = VPC1OUT (via low-pass filter).

The average output voltage from PC1, fed to the VCO input via the low-pass filter and seen at the demodulator output at

pin 10 (VDEMOUT), is the resultant of the phase differences of signals (SIGIN) and the comparator input (COMPIN) as

shown in Figure 2. The average of VDEM is equal to 1/2 VCC when there is no signal or noise at SIGIN, and with this

input the VCO oscillates at the center frequency (fo). Typical waveforms for the PC1 loop locked at fo are shown in Figure 3.

3

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

The frequency capture range (2fC) is defined as the frequency range of input signals on which the PLL will lock if it was initially out-of-lock. The frequency lock range (2fL) is defined as the frequency range of input signals on which the loop will stay locked if it was initially in lock. The capture range is smaller or equal to the lock range.

With PC1, the capture range depends on the low-pass filter characteristics and can be made as large as the lock range. This configuration retains lock behavior even with very noisy input signals. Typical of this type of phase comparator is that it can lock to input frequencies close to the harmonics of the VCO center frequency.

VCC

VDEMOUT (AV)

1/2 VCC

0

0o |

90o |

φ DEMOUT |

180o |

FIGURE 2. PHASE COMPARATOR 1: AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:

VDEMOUT = VPC1OUT = (VCC/π ) (φ SIGIN -

φ COMPIN); φ DEMOUT = (φ SIGIN - φ COMPIN)

SIGIN

COMPIN

VCOOUT

PC1OUT

VCC

VCOIN

GND

FIGURE 3. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 1, LOOP LOCKED AT fo

Phase Comparator 2 (PC2)

This is a positive edge-triggered phase and frequency detector. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of SIGIN and COMPIN are not important. PC2 comprises two D-type flip-flops, control-gating and a threestate output stage. The circuit functions as an up-down counter (Figure 1) where SIGIN causes an up-count and COMPIN a down-count. The transfer function of PC2, assuming ripple (fr = fi) is suppressed, is:

VDEMOUT |

= |

(VCC/4π ) |

(φ SIGIN |

- φ COMPIN) where |

|

VDEMOUT |

is |

the demodulator |

output |

at pin 10; |

|

VDEMOUT |

= |

VPC2OUT |

(via low-pass |

filter). |

|

The average output voltage from PC2, fed to the VCO via the low-pass filter and seen at the demodulator output at pin 10

(VDEMOUT), is the resultant of the phase differences of SIGIN and COMPIN as shown in Figure 4. Typical waveforms

for the PC2 loop locked at fo are shown in Figure 5.

VCC

VDEMOUT (AV)

1/2 VCC

0

-360o |

0o |

φ DEMOUT |

360o |

FIGURE 4. PHASE COMPARATOR 2: AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:

VDEMOUT = VPC2OUT

= (VCC/4π ) (φ SIGIN - φ COMPIN);

φ DEMOUT = (φ SIGIN - φ COMPIN)

SIGIN

COMPIN

VCOOUT

VCC

PC2OUT

GND

HIGH IMPEDANCE OFF - STATE

VCOIN

PCPOUT

FIGURE 5. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 2, LOOP LOCKED AT fo

When the frequencies of SIGIN and COMPIN are equal but the phase of SIGIN leads that of COMPIN, the p-type output driver at PC2OUT is held “ON” for a time corresponding to

the phase difference (φ DEMOUT). When the phase of SIGIN lags that of COMPIN, the n-type driver is held “ON”.

When the frequency of SIGIN is higher than that of COMPIN, the p-type output driver is held “ON” for most of the input signal cycle time, and for the remainder of the cycle both n- and p-type drivers are “OFF” (three-state). If the SIGIN frequency is lower than the COMPIN frequency, then it is the n-type driver that is held “ON” for most of the cycle. Subsequently, the voltage at the capacitor (C2) of

the low-pass filter connected to PC2 varies until the

OUT

signal and comparator inputs are equal in both phase and

4

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

frequency. At this stable point the voltage on C2 remains constant as the PC2 output is in three-state and the VCO input at pin 9 is a high impedance. Also in this condition, the signal at the phase comparator pulse output (PCPOUT) is a HIGH level and so can be used for indicating a locked condition.

Thus, for PC2, no phase difference exists between SIGIN and COMPIN over the full frequency range of the VCO. Moreover, the power dissipation due to the low-pass filter is reduced because both p- and n-type drivers are “OFF” for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the capture range and is independent of the low-pass filter. With no signal present at SIGIN, the VCO adjusts, via PC2, to its lowest frequency.

Phase Comparator 3 (PC3)

This is a positive edge-triggered sequential phase detector using an RS-type flip-flop. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of SIGIN and COMPIN are not important. The transfer characteristic of PC3, assuming ripple (fr = fi) is suppressed, is:

VDEMOUT = (VCC/2p) (fSIGIN - fCOMPIN) where VDEMOUT is the demodulator output at pin 10; VDEMOUT = VPC3OUT (via low-pass filter).

The average output from PC3, fed to the VCO via the lowpass filter and seen at the demodulator at pin 10

(VDEMOUT), is the resultant of the phase differences of SIGIN and COMPIN as shown in Figure 6. Typical

waveforms for the PC3 loop locked at fo are shown in Figure 7.

The phase-to-output response characteristic of PC3 (Figure 6) differs from that of PC2 in that the phase angle between SIGIN and COMPIN varies between 0o and 360o and is 180o at the center frequency. Also PC3 gives a greater voltage swing than PC2 for input phase differences but as aconsequence the ripple content of the VCO input signal is higher. With no signal present at SIGIN, the VCO adjusts, via PC3, to its highest frequency.

The only difference between the HC and HCT versions is the input level specification of the INH input. This input disables the VCO section. The comparator’s sections are identical, so that there is no difference in the SIGIN (pin 14) or COMPIN (pin 3) inputs between the HC and the HCT versions.

VCC

VDEMOUT (AV)

1/2 VCC

0

0o |

180o |

φ DEMOUT |

360o |

FIGURE 6. PHASE COMPARATOR 3: AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:

VDEMOUT = VPC3OUT

= (VCC/2π ) (φ SIGIN - φ COMPIN);

φ DEMOUT = (φ SIGIN - φ COMPIN)

SIGIN

COMPIN

VCOOUT

PC3OUT

VCC

VCOIN

GND

FIGURE 7. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 3, LOOP LOCKED AT fo

5

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

Absolute Maximum Ratings |

|

Thermal Information |

|

||||||||||

DC Supply Voltage, VCC |

. . |

. |

. |

. . . . . . . . . . . . . . . . . . . . |

-0.5V to 7V |

Package Thermal Impedance, θ JA (see Note 1): |

67oC/W |

||||||

DC Input Diode Current, IIK |

|

|

|

|

E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . |

||||||||

For V |

I |

< -0.5V or V |

I |

> V |

|

+ 0.5V . . . . . . . . . . . . . . . . . . |

. . . .±20mA |

M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 73oC/W |

||||

|

|

|

|

|

CC |

|

|

|

|

64oC/W |

|||

DC Output Diode Current, IOK |

|

|

NS (SOP) Package . . . . . . . . . . . . . . . . . . . . . . . . |

||||||||||

For V < -0.5V or V |

|

> V |

CC |

+ 0.5V . . . . . . . . . . . . . . . . |

. . . .±20mA |

PW (TSSOP) Package. . . . . . . . . . . . . . . . . . . . . . |

. . . . 108oC/W |

||||||

O |

|

O |

|

|

|

|

|

150oC |

|||||

DC Drain Current, per Output, I |

|

Maximum Junction Temperature . . . . . . . . . . . . . . . . |

|||||||||||

|

|

|

|

|

|

|

|

|

|

O |

±25mA |

|

-65oC to 150oC |

For -0.5V < V |

< V |

CC |

+ 0.5V. . . . . . . . . . . . . . . . . . . . . . |

Maximum Storage Temperature Range . . . . . . . . . . |

|||||||||

|

|

O |

|

|

|

|

|

|

|

300oC |

|||

DC Output Source or Sink Current per Output Pin, IO |

±25mA |

Maximum Lead Temperature (Soldering 10s) . . . . . . |

|||||||||||

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . |

(SOIC - Lead Tips Only) |

|

|||||||||||

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . . . |

. . . .±50mA |

|

|

||||||||||

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

DC Electrical Specifications

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

CONDITIONS |

VCC |

|

|

|

||||||

PARAMETER |

SYMBOL |

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCO SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH High Level Input |

VIH |

- |

- |

3 |

2.1 |

- |

- |

2.1 |

- |

2.1 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

- |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

INH Low Level Input |

VIL |

- |

- |

3 |

- |

- |

0.9 |

- |

0.9 |

- |

0.9 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT High Level |

VOH |

VIH or VIL |

-0.02 |

3 |

2.9 |

- |

- |

2.9 |

- |

2.9 |

- |

V |

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

6 |

5.9 |

- |

- |

5.9 |

- |

5.9 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT High Level |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-4 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-5.2 |

6 |

5.48 |

- |

- |

5.34 |

- |

5.2 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT Low Level |

VOL |

VIH or VIL |

0.02 |

2 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

6 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT Low Level |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.2 |

6 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

C1A, C1B Low Level |

VOL |

VIL or VIH |

4 |

4.5 |

- |

- |

0.40 |

- |

0.47 |

- |

0.54 |

V |

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.2 |

6 |

- |

- |

0.40 |

- |

0.47 |

- |

0.54 |

V |

|

(Test Purposes Only) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

DC Electrical Specifications (Continued)

|

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

|

CONDITIONS |

VCC |

|

|

|

||||||

PARAMETER |

SYMBOL |

|

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

INH VCOIN Input |

II |

|

VCC or |

- |

6 |

- |

- |

±0.1 |

- |

±1 |

- |

±1 |

µA |

Leakage Current |

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R1 Range (Note 2) |

- |

|

- |

- |

4.5 |

3 |

- |

300 |

- |

- |

- |

- |

kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2 Range (Note 2) |

- |

|

- |

- |

4.5 |

3 |

- |

300 |

- |

- |

- |

- |

kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 Capacitance |

- |

|

- |

- |

3 |

- |

- |

No |

- |

- |

- |

- |

pF |

Range |

|

|

|

|

|

|

|

Limit |

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

- |

- |

- |

- |

pF |

||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

|

- |

- |

- |

- |

pF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOIN Operating |

- |

|

Over the range |

3 |

1.1 |

- |

1.9 |

- |

- |

- |

- |

V |

|

Voltage Range |

|

|

specified for R1 for |

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

1.1 |

- |

3.2 |

- |

- |

- |

- |

V |

|||

|

|

|

Linearity See Figure |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

6 |

1.1 |

- |

4.6 |

- |

- |

- |

- |

V |

||

|

|

|

10, and 34 - 37 |

||||||||||

|

|

|

(Note 3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PHASE COMPARATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN |

VIH |

|

- |

- |

2 |

1.5 |

- |

- |

1.5 |

- |

1.5 |

- |

V |

DC Coupled |

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

- |

V |

High-Level Input |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

|

Voltage |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN |

VIL |

|

- |

- |

2 |

- |

- |

0.5 |

- |

0.5 |

- |

0.5 |

V |

DC Coupled |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

|

Low-Level Input |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

|

Voltage |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOH |

|

VIL or VIH |

-0.02 |

2 |

1.9 |

- |

- |

1.9 |

- |

1.9 |

- |

V |

High-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

Voltage |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

5.9 |

- |

- |

5.9 |

- |

5.9 |

- |

V |

|

CMOS Loads |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOH |

|

VIL or VIH |

-4 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

High-Level Output |

|

|

|

-5.2 |

6 |

5.48 |

- |

- |

5.34 |

- |

5.2 |

- |

V |

Voltage |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOL |

|

VIL or VIH |

0.02 |

2 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

Low-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

Voltage |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

CMOS Loads |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOL |

|

VIL or VIH |

4 |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

Low-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.2 |

6 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

Voltage |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN Input |

II |

|

VCC or |

- |

2 |

- |

- |

±3 |

- |

±4 |

- |

±5 |

µA |

Leakage Current |

|

|

GND |

|

3 |

- |

- |

±7 |

- |

±9 |

- |

±11 |

µA |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

±18 |

- |

±23 |

- |

±29 |

µA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

±30 |

- |

±38 |

- |

±45 |

µA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PC2OUT Three-State |

IOZ |

|

VIL or VIH |

- |

6 |

- |

- |

±0.5 |

- |

±5 |

- |

±10 |

µA |

Off-State Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN Input |

RI |

|

VI at Self-Bias |

3 |

- |

800 |

- |

- |

- |

- |

- |

kΩ |

|

Resistance |

|

|

Operation Point: |

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

250 |

- |

- |

- |

- |

- |

kΩ |

|||

|

|

|

∆ VI = 0.5V, |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

6 |

- |

150 |

- |

- |

- |

- |

- |

kΩ |

||

|

|

|

See Figure 10 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DEMODULATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Resistor Range |

RS |

|

at RS > 300kΩ |

3 |

50 |

- |

300 |

- |

- |

- |

- |

kΩ |

|

|

|

|

Leakage Current |

4.5 |

50 |

- |

300 |

- |

- |

- |

- |

kΩ |

|

|

|

|

Can Influence |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

6 |

50 |

- |

300 |

- |

- |

- |

- |

kΩ |

||

|

|

|

VDEMOUT |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

7

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

DC Electrical Specifications (Continued)

|

|

|

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

|

|

CONDITIONS |

VCC |

|

|

|

|||||||

PARAMETER |

SYMBOL |

|

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

||

Offset Voltage VCOIN |

VOFF |

|

VI = VVCO IN = |

3 |

- |

±30 |

- |

- |

- |

- |

- |

mV |

|||

to V |

DEM |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

±20 |

- |

- |

- |

- |

- |

mV |

|||||

|

|

2 |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Values Taken Over |

6 |

- |

±10 |

- |

- |

- |

- |

- |

mV |

||

|

|

|

|

|

RS Range |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

See Figure 23 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Dynamic Output |

RD |

|

VDEMOUT = |

3 |

- |

25 |

- |

- |

- |

- |

- |

Ω |

|||

Resistance at |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

25 |

- |

- |

- |

- |

- |

Ω |

|||||

DEMOUT |

|

2 |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

6 |

- |

25 |

- |

- |

- |

- |

- |

Ω |

|||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Quiescent Device |

ICC |

|

Pins 3, 5 and 14 |

6 |

- |

- |

8 |

- |

80 |

- |

160 |

µA |

|||

Current |

|

|

at VCC Pin 9 at |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

GND, I1 at Pins 3 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

and 14 to be |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

excluded |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HCT TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCO SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH High Level Input |

VIH |

- |

- |

4.5 to |

2 |

- |

- |

2 |

- |

2 |

- |

V |

|||

Voltage |

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH Low Level Input |

VIL |

- |

- |

4.5 to |

- |

- |

0.8 |

- |

0.8 |

- |

0.8 |

V |

|||

Voltage |

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT High Level |

VOH |

|

VIH or VIL |

-0.02 |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

||

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT High Level |

|

|

|

|

-4 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT Low Level |

VOL |

|

VIH or VIL |

0.02 |

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

||

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOOUT Low Level |

|

|

|

|

4 |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1A, C1B Low Level |

VOL |

|

VIH or VIL |

4 |

4.5 |

- |

- |

0.40 |

- |

0.47 |

- |

0.54 |

V |

||

Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Test Purposes Only) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH VCOIN Input |

II |

|

Any Voltage |

5.5 |

- |

|

±0.1 |

- |

±1 |

- |

±1 |

µA |

|||

Leakage Current |

|

|

Between VCC and |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R1 Range (Note 2) |

- |

- |

- |

4.5 |

3 |

- |

300 |

- |

- |

- |

- |

kΩ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2 Range (Note 2) |

- |

- |

- |

4.5 |

3 |

- |

300 |

- |

- |

- |

- |

kΩ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 Capacitance |

- |

- |

- |

4.5 |

0 |

- |

No |

- |

- |

- |

- |

pF |

|||

Range |

|

|

|

|

|

|

|

|

Limit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOIN Operating |

- |

|

Over the range |

4.5 |

1.1 |

- |

3.2 |

- |

- |

- |

- |

V |

|||

Voltage Range |

|

|

specified for R1 for |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Linearity See Figure |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

10, and 34 - 37 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

(Note 3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PHASE COMPARATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN |

VIH |

- |

- |

4.5 to |

2 |

- |

- |

2 |

- |

2 |

- |

V |

|||

DC Coupled |

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

High-Level Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

DC Electrical Specifications (Continued)

|

|

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

|

CONDITIONS |

VCC |

|

|

|

|||||||

PARAMETER |

SYMBOL |

|

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

|

SIGIN, COMPIN |

VIL |

- |

- |

4.5 to |

- |

- |

0.8 |

- |

0.8 |

- |

0.8 |

V |

||

DC Coupled |

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

Low-Level Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOH |

|

VIL or VIH |

- |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

High-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOH |

|

VIL or VIH |

- |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

High-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOL |

|

VIL or VIH |

- |

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

Low-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCPOUT, PCn OUT |

VOL |

|

VIL or VIH |

- |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

Low-Level Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TTL Loads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN Input |

II |

|

Any |

- |

5.5 |

- |

- |

±30 |

|

±38 |

|

±45 |

µA |

|

Leakage Current |

|

|

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Between |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PC2OUT Three-State |

IOZ |

|

VIL or VIH |

- |

5.5 |

- |

- |

±0.5 |

±5 |

- |

- |

±10 |

µA |

|

Off-State Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN Input |

RI |

|

VI at Self-Bias |

4.5 |

- |

250 |

- |

- |

- |

- |

- |

kΩ |

||

Resistance |

|

|

Operation Point: |

|

|

|

|

|

|

|

|

|

||

|

|

|

∆ VI = 0.5V, |

|

|

|

|

|

|

|

|

|

||

|

|

|

See Figure 10 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DEMODULATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Resistor Range |

RS |

|

at RS > 300kΩ |

4.5 |

5 |

- |

300 |

- |

- |

- |

- |

kΩ |

||

|

|

|

Leakage Current |

|

|

|

|

|

|

|

|

|

||

|

|

|

Can Influence |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

VDEM OUT |

|

|

|

|

|

|

|

|

|

|

Offset Voltage VCOIN |

VOFF |

|

VI = VVCO IN = |

4.5 |

- |

±20 |

- |

- |

- |

- |

- |

mV |

||

to VDEM |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Values taken over |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

RS Range |

|

|

|

|

|

|

|

|

|

|

|

|

|

See Figure 23 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dynamic Output |

RD |

|

VDEM OUT = |

4.5 |

- |

25 |

- |

- |

- |

- |

- |

Ω |

||

Resistance at |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

DEMOUT |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

Quiescent Device |

ICC |

|

VCC or |

- |

5.5 |

- |

- |

8 |

- |

80 |

- |

160 |

µA |

|

Current |

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Additional Quiescent |

∆ ICC |

|

VCC |

- |

4.5 to |

- |

100 |

360 |

- |

450 |

- |

490 |

µA |

|

Device Current Per |

(Note 4) |

-2.1 |

|

5.5 |

|

|

|

|

|

|

|

|

||

Input Pin: 1 Unit Load |

|

|

Excluding |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.The value for R1 and R2 in parallel should exceed 2.7kΩ .

3.The maximum operating voltage can be as high as VCC -0.9V, however, this may result in an increased offset voltage.

4.For dual-supply systems theoretical worst case (VI = 2.4V, VCC = 5.5V) specification is 1.8mA.

9

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

HCT Input Loading Table

INPUT |

UNIT LOADS |

|

|

INH |

1 |

|

|

NOTE: Unit load is ∆ ICC limit specific in DC Electrical Specifications

Table, e.g., 360µA max. at 25oC.

Switching Specifications CL = 50pF, Input tr, tf = 6ns

|

|

|

|

|

|

|

|

|

|

|

-40oC TO |

-55oC TO |

|

||

|

|

|

|

|

|

TEST |

|

|

25oC |

|

85oC |

125oC |

|

||

|

PARAMETER |

SYMBOL |

CONDITIONS |

VCC (V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

|||

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

PHASE COMPARATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Propagation Delay |

tPLH, tPHL |

|

|

|

|

|

|

|

|

|

|

||||

|

SIGIN, COMPIN to PCIOUT |

|

|

|

|

|

2 |

- |

- |

200 |

- |

250 |

- |

300 |

ns |

|

|

|

|

|

|

|

4.5 |

- |

- |

40 |

- |

50 |

- |

60 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

34 |

- |

43 |

- |

51 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN to PCPOUT |

|

|

|

|

|

2 |

- |

- |

300 |

- |

375 |

- |

450 |

ns |

|

|

|

|

|

|

|

4.5 |

- |

- |

60 |

- |

75 |

- |

90 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

51 |

- |

64 |

- |

77 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGIN, COMPIN to PC3OUT |

|

|

|

|

|

2 |

- |

- |

245 |

- |

305 |

- |

307 |

ns |

|

|

|

|

|

|

|

4.5 |

- |

- |

49 |

- |

61 |

- |

74 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

42 |

- |

52 |

- |

63 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

||||

Output Transition Time |

tTHL, tTLH |

|

2 |

- |

- |

75 |

- |

95 |

- |

110 |

ns |

||||

|

|

|

|

|

|

|

4.5 |

- |

- |

15 |

- |

19 |

- |

22 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

13 |

- |

16 |

- |

19 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

||||

Output Enable Time, SIGIN, |

tPZH, tPZL |

|

2 |

- |

- |

265 |

- |

330 |

- |

400 |

ns |

||||

COMPIN to PC2OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

53 |

- |

66 |

- |

80 |

ns |

||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

45 |

- |

56 |

- |

68 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

||||

Output Disable Time, SIGIN, |

tPHZ, tPLZ |

|

2 |

- |

- |

315 |

- |

395 |

- |

475 |

ns |

||||

COMPIN to PC2OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

63 |

- |

79 |

- |

95 |

ns |

||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

54 |

- |

67 |

- |

81 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC Coupled Input Sensitivity |

|

|

|

|

VI(P-P) |

3 |

- |

11 |

- |

- |

- |

- |

- |

mV |

|

(P-P) at SIGIN or COMPIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

15 |

- |

- |

- |

- |

- |

mV |

||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

33 |

- |

- |

- |

- |

- |

mV |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCO SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Frequency Stability with |

|

∆ f |

R = 100kΩ , |

3 |

- |

0.11 |

- |

- |

- |

- |

- |

%/oC |

|||

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

Temperature Change |

|

|

|

|

R2 = ∞ |

|

|

|

|

|

|

|

|

|

|

|

∆ |

T |

|

|

|

|

|

|

|

|

|

||||

|

|

4.5 |

- |

0.11 |

- |

- |

- |

- |

- |

%/oC |

|||||

|

|

|

|

|

|

|

6 |

- |

0.11 |

- |

- |

- |

- |

- |

%/oC |

Maximum Frequency |

fMAX |

C1 = 50pF |

3 |

- |

24 |

- |

- |

- |

- |

- |

MHz |

||||

|

|

|

|

|

|

R1 = 3.5kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

24 |

- |

- |

- |

- |

- |

MHz |

|

|

|

|

|

|

|

R2 = ∞ |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

24 |

- |

- |

- |

- |

- |

MHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 = 0pF |

3 |

- |

38 |

- |

- |

- |

- |

- |

MHz |

|

|

|

|

|

|

R1 = 9.1kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

38 |

- |

- |

- |

- |

- |

MHz |

|

|

|

|

|

|

|

R2 = ∞ |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

38 |

- |

- |

- |

- |

- |

MHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10

Loading...

Loading...