TEXAS INSTRUMENTS CD54HC4051F3A, CD54HC4052F3A, CD54HC4053F3A, CD54HCT4051F3A, CD74HC4051E Technical data

...

[ /Title (CD54 HC405 1, CD74 HC405 1, CD74 HCT40 51, CD74 HC405 2,

Data sheet acquired from Harris Semiconductor SCHS122G

November 1997 - Revised July 2003

CD54/74HC4051, CD54/74HCT4051, CD54/74HC4052, CD74HCT4052, CD54/74HC4053, CD74HCT4053

High-Speed CMOS Logic Analog Multiplexers/Demultiplexers

Features |

Ordering Information |

• Wide Analog Input Voltage Range . . . . . . . . . . ± 5V Max

•Low “On” Resistance

-70Ω Typical (VCC - VEE = 4.5V)

-40Ω Typical (VCC - VEE = 9V)

•Low Crosstalk between Switches

•Fast Switching and Propagation Speeds

•“Break-Before-Make” Switching

• Wide Operating Temperature Range . . -55oC to 125oC

• CD54HC/CD74HC Types |

|

|

|

- |

Operation Control Voltage . . . . |

. . . . . . . . . . 2V to 6V |

|

- |

Switch Voltage . . . . . . . |

. . . . . . . . |

. . . . . . . . 0V to 10V |

- |

High Noise Immunity . . . |

NIL = 30%, NIH = 30% of VCC, |

|

|

VCC = 5V |

|

|

• CD54HCT/CD74HCT Types |

|

||

- |

Operation Control Voltage . . . . . |

. . . . . . 4.5V to 5.5V |

|

- |

Switch Voltage . . . . . . . |

. . . . . . . . |

. . . . . . . . 0V to 10V |

- |

Direct LSTTL Input |

|

|

|

Logic Compatibility . . . |

VIL = 0.8V Max, VIH = 2V Min |

|

- |

CMOS Input Compatibility . . . . . |

II ≤ 1µ A at VOL, VOH |

|

Description

These devices are digitally controlled analog switches which utilize silicon gate CMOS technology to achieve operating speeds similar to LSTTL with the low power consumption of standard CMOS integrated circuits.

These analog multiplexers/demultiplexers control analog voltages that may vary across the voltage supply range (i.e. VCC to VEE). They are bidirectional switches thus allowing any analog input to be used as an output and vice-versa.

The switches have low “on” resistance and low “off” leakages. In addition, all three devices have an enable control which, when high, disables all switches to their “off” state.

|

TEMP. RANGE |

|

PART NUMBER |

(oC) |

PACKAGE |

CD54HC4051F3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD54HC4052F3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD54HC4053F3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD54HCT4051F3A |

-55 to 125 |

16 Ld CERDIP |

|

|

|

CD74HC4051E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HC4051M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4051M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4051NSR |

-55 to 125 |

16 Ld SOP |

|

|

|

CD74HC4051PWR |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HC4052E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HC4052M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4052M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4052NSR |

-55 to 125 |

16 Ld SOP |

|

|

|

CD74HC4052PW |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HC4052PWR |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HC4053E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HC4053M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4053M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HC4053NSR |

-55 to 125 |

16 Ld SOP |

|

|

|

CD74HC4053PW |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HC4053PWR |

-55 to 125 |

16 Ld TSSOP |

|

|

|

CD74HCT4051E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HCT4051M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4051M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4052E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HCT4052M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4052M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4053E |

-55 to 125 |

16 Ld PDIP |

|

|

|

CD74HCT4053M |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4053M96 |

-55 to 125 |

16 Ld SOIC |

|

|

|

CD74HCT4053PWR |

-55 to 125 |

16 Ld TSSOP |

|

|

|

NOTE: When ordering, use the entire part number. The suffixes 96 and R denote tape and reel.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © 2003, Texas Instruments Incorporated

1

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

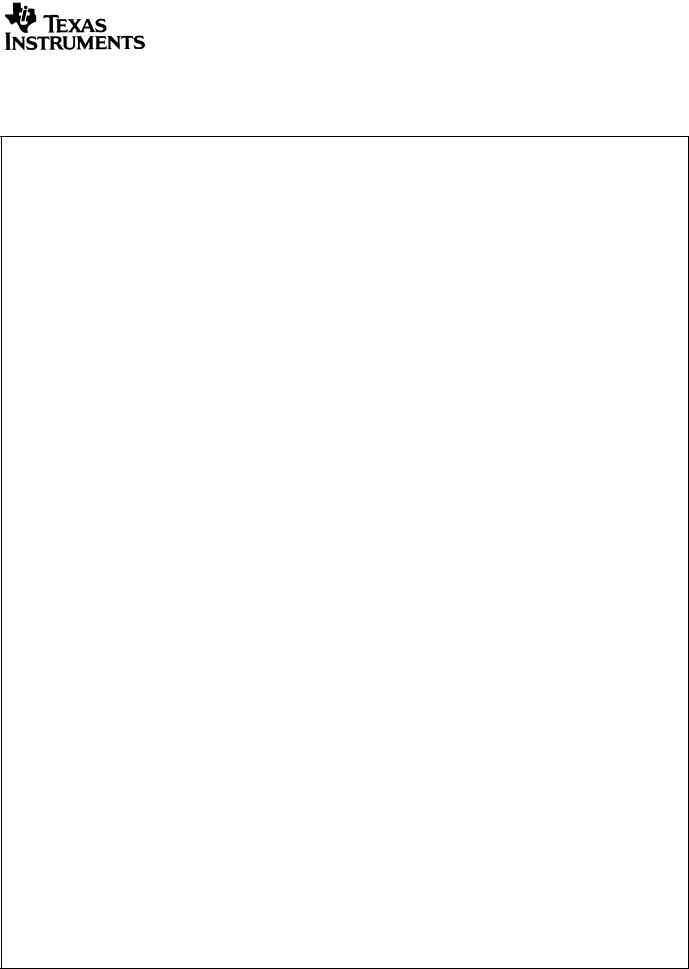

Pinouts

CD54HC4051, CD54HCT4051 (CERDIP)

CD74HC4051

(PDIP, SOIC, SOP, TSSOP)

CD74HCT4051

(PDIP, SOIC)

TOP VIEW

CHANNEL |

A4 |

1 |

IN/OUT |

A6 |

2 |

|

COM OUT/IN |

A |

3 |

CHANNEL |

A7 |

4 |

IN/OUT |

A5 |

5 |

|

E |

6 |

VEE |

7 |

GND |

8 |

16 VCC |

15 |

A2 |

14 |

A1 |

CHANNEL |

|

|

|

13 |

A0 |

IN/OUT |

|

12 |

A3 |

11 |

S0 |

10 S1 |

ADDRESS |

|

SELECT |

9 |

S2 |

CD54HC4052

(CERDIP)

CD74HC4052

(PDIP, SOIC, SOP, TSSOP)

CD74HCT4052

(PDIP, SOIC)

TOP VIEW

CHANNEL |

B0 |

1 |

|

|

|

IN/OUT |

B2 |

2 |

|

COM OUT/IN BN |

3 |

CHANNEL |

B3 |

4 |

|

|

|

IN/OUT |

B1 |

5 |

|

E |

6 |

VEE |

7 |

GND |

8 |

16 VCC |

15 |

A2 |

CHANNEL |

|

|

|

14 |

A1 |

IN/OUT |

|

||

13 |

AN |

COM OUT/IN |

12 |

A0 |

CHANNEL |

|

|

|

11 |

A3 |

IN/OUT |

10 |

S0 |

9 |

S1 |

CD54HC4053

(CERDIP)

CD74HC4053

(PDIP, SOIC, SOP, TSSOP)

CD74HCT4053

(PDIP, SOIC, TSSOP)

TOP VIEW

B1 |

1 |

CHANNEL |

B0 |

2 |

|

IN/OUT |

|||

|

|

C1 |

3 |

COM OUT/IN CN |

4 |

IN/OUT C0 |

5 |

E |

6 |

VEE |

7 |

GND |

8 |

16 VCC |

15 |

BN |

COM OUT/IN |

14 |

AN |

COM OUT/IN |

13 |

A1 |

CHANNEL |

|

|

|

12 |

A0 |

IN/OUT |

11 |

S0 |

|

10 |

S1 |

9 |

S2 |

2

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

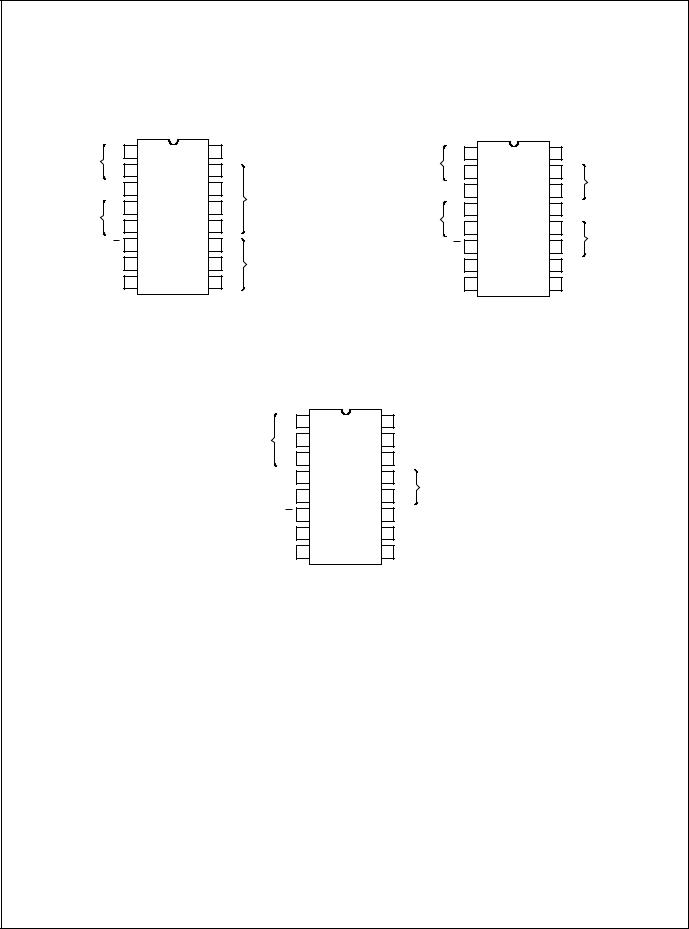

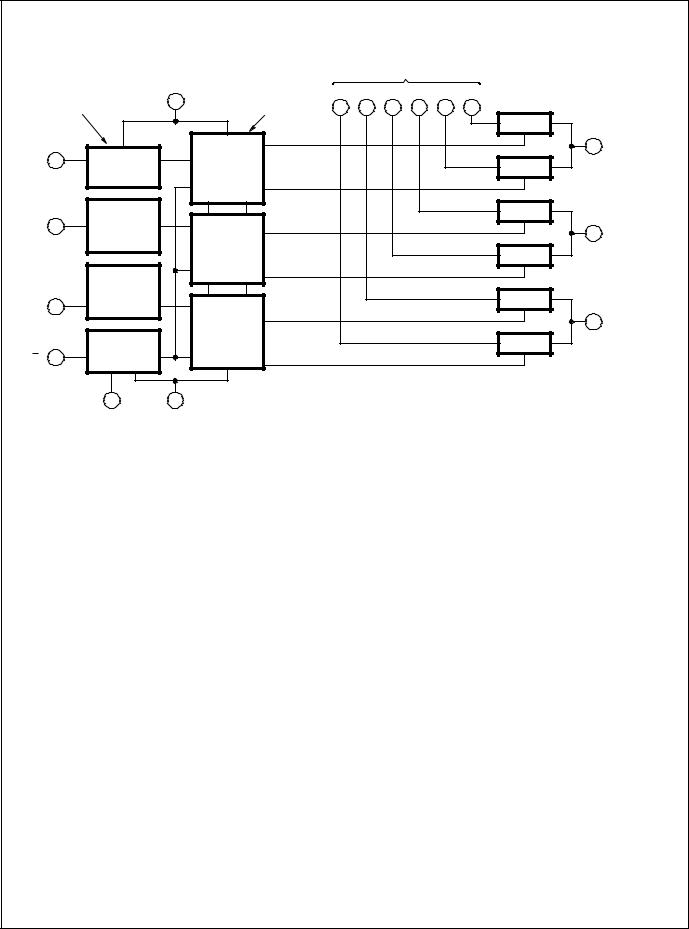

Functional Diagram of HC/HCT4051

|

|

|

CHANNEL IN/OUT |

|

|

|||

VCC |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

16 |

4 |

2 |

5 |

1 |

12 |

15 |

14 |

13 |

TG |

TG

S0 11

|

|

|

TG |

S1 |

10 |

|

TG |

BINARY |

A |

||

|

|

3 COMMON |

|

|

LOGIC |

TO |

OUT/IN |

|

1 OF 8 |

||

|

LEVEL |

TG |

|

|

DECODER |

||

|

CONVERSION |

|

|

|

WITH |

|

|

|

|

|

|

S2 |

9 |

ENABLE |

|

|

TG |

||

|

|

|

|

|

|

|

TG |

E |

6 |

|

|

|

|

|

TG |

8 |

7 |

GND VEE

TRUTH TABLE

HC/HCT4051

|

INPUT STATES |

|

“ON” |

|

|

|

|

|

|

ENABLE |

S2 |

S1 |

S0 |

CHANNELS |

L |

L |

L |

L |

A0 |

|

|

|

|

|

L |

L |

L |

H |

A1 |

|

|

|

|

|

L |

L |

H |

L |

A2 |

|

|

|

|

|

L |

L |

H |

H |

A3 |

|

|

|

|

|

L |

H |

L |

L |

A4 |

|

|

|

|

|

L |

H |

L |

H |

A5 |

|

|

|

|

|

L |

H |

H |

L |

A6 |

|

|

|

|

|

L |

H |

H |

H |

A7 |

|

|

|

|

|

H |

X |

X |

X |

None |

|

|

|

|

|

X = Don’t care

3

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

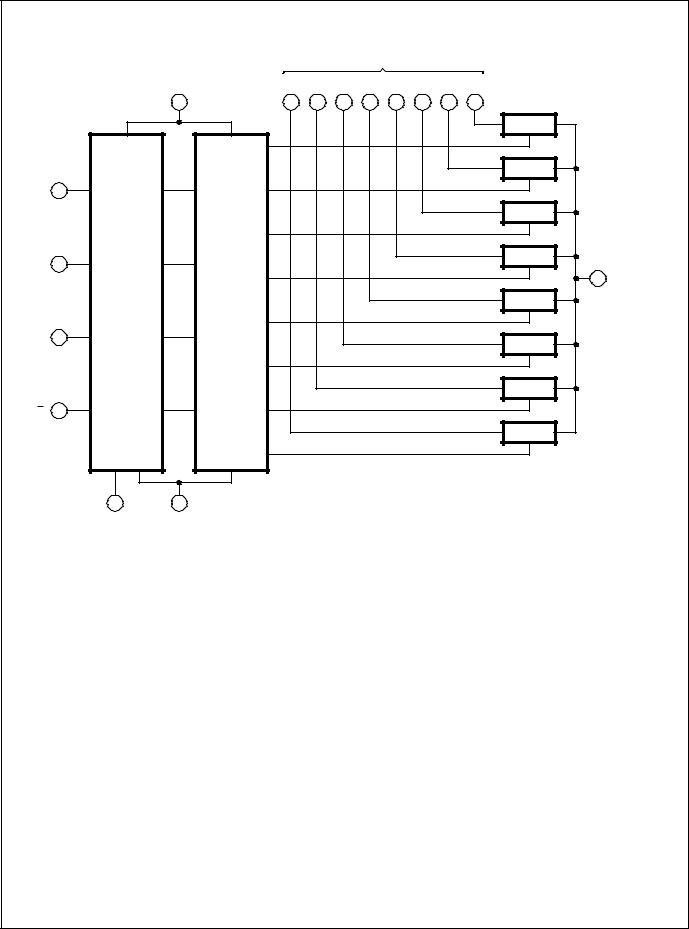

Functional Diagram of ’HC4052, CD74HCT4052

|

A CHANNELS IN/OUT |

||||

VCC |

A3 |

A2 |

A1 |

A0 |

|

11 |

15 |

14 |

12 |

||

|

|||||

16 |

|

|

|

|

|

|

|

|

BINARY |

|

S1 |

9 |

LOGIC |

TO |

|

1 OF 4 |

||||

LEVEL |

||||

|

|

CONVERSION |

DECODER |

|

|

|

WITH |

||

|

|

|

||

|

|

|

ENABLE |

|

S0 |

10 |

|

|

|

E |

6 |

|

|

8 |

7 |

GND VEE

TRUTH TABLE

’HC4052, CD74HCT4052

|

INPUT STATES |

|

“ON” |

||

|

|

|

|

|

|

ENABLE |

|

S1 |

|

S0 |

CHANNELS |

L |

|

L |

|

L |

A0, B0 |

|

|

|

|

|

|

L |

|

L |

|

H |

A1, B1 |

|

|

|

|

|

|

L |

|

H |

|

L |

A2. B2 |

|

|

|

|

|

|

L |

|

H |

|

H |

A3, B3 |

|

|

|

|

|

|

H |

|

X |

|

X |

None |

|

|

|

|

|

|

X = Don’t care

1 |

5 |

2 |

4 |

B0 |

B1 |

B2 |

B3 |

B CHANNELS IN/OUT

TG

TG

TG |

|

|

|

TG |

13 |

COMMON A |

|

OUT/IN |

|||

|

|

||

TG |

3 |

COMMON B |

|

OUT/IN |

|||

|

|

||

TG |

|

|

TG

TG

4

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

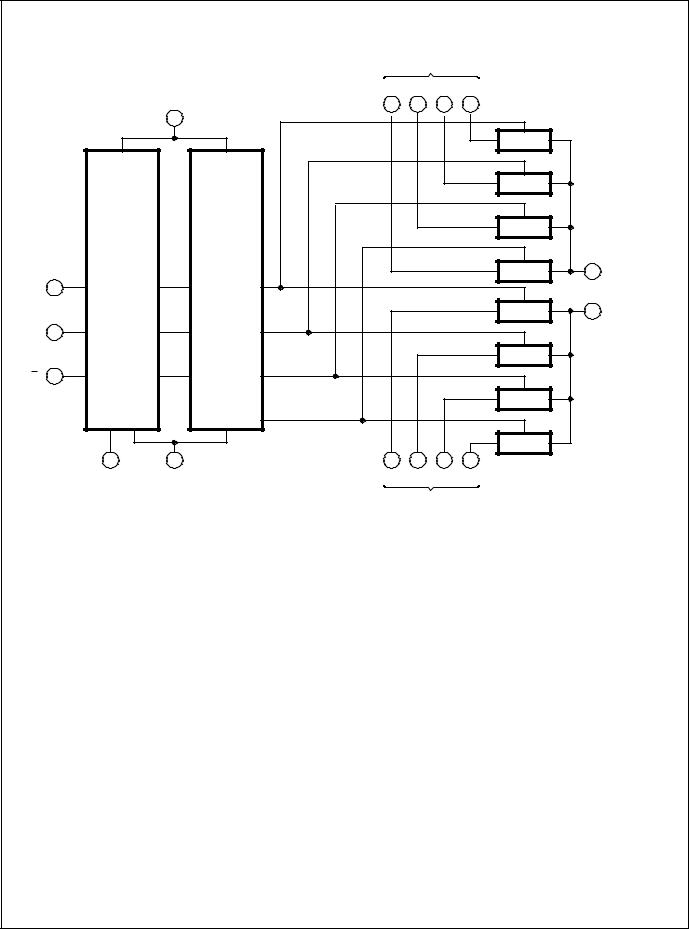

Functional Diagram of ’HC4053, CD74HCT4053

|

|

VCC |

BINARY TO |

|

|

IN/OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

1 OF 2 |

C1 |

C0 |

B1 |

B0 |

A1 |

A0 |

|

|

|

LOGIC LEVEL |

16 |

DECODERS |

|

||||||

|

|

|

|

|

|

|

|

|||

|

CONVERSION |

WITH ENABLE |

3 |

5 |

1 |

2 |

13 |

12 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

TG |

|

|

|

|

|

|

|

|

|

|

14 |

A COMMON |

|

|

|

|

|

|

|

|

|

OUT/IN |

|

S0 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TG |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TG |

|

S1 |

10 |

|

|

|

|

|

|

|

15 |

B COMMON |

|

|

|

|

|

|

|

|

|

OUT/IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TG |

|

S2 |

9 |

|

|

|

|

|

|

|

TG |

|

|

|

|

|

|

|

|

|

C COMMON |

||

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

OUT/IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TG |

|

E |

6 |

|

|

|

|

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

|

|

|

GND |

VEE |

|

|

|

|

|

|

|

|

TRUTH TABLE

’HC4053, CD74HCT4053

|

INPUT STATES |

|

“ON” |

|

|

|

|

|

|

ENABLE |

S0 |

S1 |

S2 |

CHANNELS |

L |

L |

L |

L |

C0, B0, A0 |

|

|

|

|

|

L |

H |

L |

L |

C0, B0, A1 |

|

|

|

|

|

L |

L |

H |

L |

C0, B1, A0 |

|

|

|

|

|

L |

H |

H |

L |

C0, B1, A1 |

|

|

|

|

|

L |

L |

L |

H |

C1, B0, A0 |

|

|

|

|

|

L |

H |

L |

H |

C1, B0, A1 |

|

|

|

|

|

L |

L |

H |

H |

C1, B1, A0 |

|

|

|

|

|

L |

H |

H |

H |

C1, B1, A1 |

|

|

|

|

|

H |

X |

X |

X |

None |

|

|

|

|

|

X = Don’t care

5

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

Absolute Maximum Ratings (Note 2) |

|

|

Thermal Information |

|

||||||

DC Supply Voltage, VCC - VEE . . . . . . . . . . . . . . . . . |

-0.5V to 10.5V |

Package Thermal Impedance, θ JA (see Note 1): |

67oC/W |

|||||||

DC Supply Voltage, VCC . |

. . . |

. . . . . . . . . . . . . . . . . . . . . |

. . . -0.5V to +7V |

E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . |

||||||

DC Supply Voltage, VEE . |

. . . |

. . . . . . . . . . . . . . . . . . . . . . |

. . +0.5V to -7V |

M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 73oC/W |

|||||

DC Input Diode Current, IIK |

|

|

|

NS (SOP) Package . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 64oC/W |

|||||

For V |

I |

< -0.5V or V |

I |

> V |

CC |

+ 0.5V . . . . . . . . . . . . . . . . |

. . . . . .± |

20mA |

PW (TSSOP) Package . . . . . . . . . . . . . . . . . . . . . |

. . . . . 108oC/W |

|

|

|

|

|

|

|

150oC |

|||

DC Switch Diode Current, IOK |

|

|

Maximum Junction Temperature . . . . . . . . . . . . . . . . |

|||||||

For VI < VEE -0.5V or VI > VCC + 0.5V . . . . . . . . . . . |

. . . . . .± |

20mA |

Maximum Storage Temperature Range . . . . . . . . . . |

-65oC to 150oC |

||||||

DC Switch Current, (Note 2) |

|

|

|

Maximum Lead Temperature (Soldering 10s) . . . . . . |

. . . . . . . 300oC |

|||||

For VI > VEE -0.5V or VI < VCC + 0.5V . . . . . . . . . . . |

. . . . . .± |

25mA |

|

|

||||||

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . |

. . . . . .± |

50mA |

|

|

||||||

DC VEE Current, IEE |

|

. . . |

. . . |

. . . . . . . . . . . . . . . . . . . . |

. . . . . -20mA |

|

|

|||

NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

Recommended Operating Conditions For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges

|

PARAMETER |

MIN |

MAX |

UNITS |

|

|

|

|

|

Supply Voltage Range (For TA = Full Package Temperature Range), VCC (Note 2) |

|

|

|

|

|

CD54/74HC Types |

2 |

6 |

V |

|

|

|

|

|

|

CD54/74HCT Types |

4.5 |

5.5 |

V |

|

|

|

|

|

Supply Voltage Range (For TA = Full Package Temperature Range), VCC - VEE |

|

|

|

|

|

CD54/74HC Types, CD54/74HCT Types (See Figure 1) |

2 |

10 |

V |

|

|

|

|

|

Supply Voltage Range (For TA = Full Package Temperature Range), VEE (Note 3) |

|

|

|

|

|

CD54/74HC Types, CD54/74HCT Types (See Figure 2) |

0 |

-6 |

V |

|

|

|

|

|

DC Input Control Voltage, VI |

GND |

VCC |

V |

|

Analog Switch I/O Voltage, VIS |

VEE |

VCC |

V |

|

Operating Temperature, T |

-55 |

125 |

oC |

|

|

A |

|

|

|

Input Rise and Fall Times, tr, tf |

|

|

|

|

|

2V |

0 |

1000 |

ns |

|

|

|

|

|

|

4.5V |

0 |

500 |

ns |

|

|

|

|

|

|

6V |

0 |

400 |

ns |

|

|

|

|

|

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

2.All voltages referenced to GND unless otherwise specified..

3.In certain applications, the external load resistor current may include both VCC and signal line components. To avoid drawing VCC current when switch current flows into the transmission gate inputs, the voltage drop across the bidirectional switch must not exceed 0.6V (cal-

culated from rON values shown in Electrical Specifications table). No VCC current will flow through RL if the switch current flows into terminal 3 on the HC/HCT4051; terminals 3 and 13 on the HC/HCT4052; terminals 4, 14 and 15 on the HC/HCT4053.

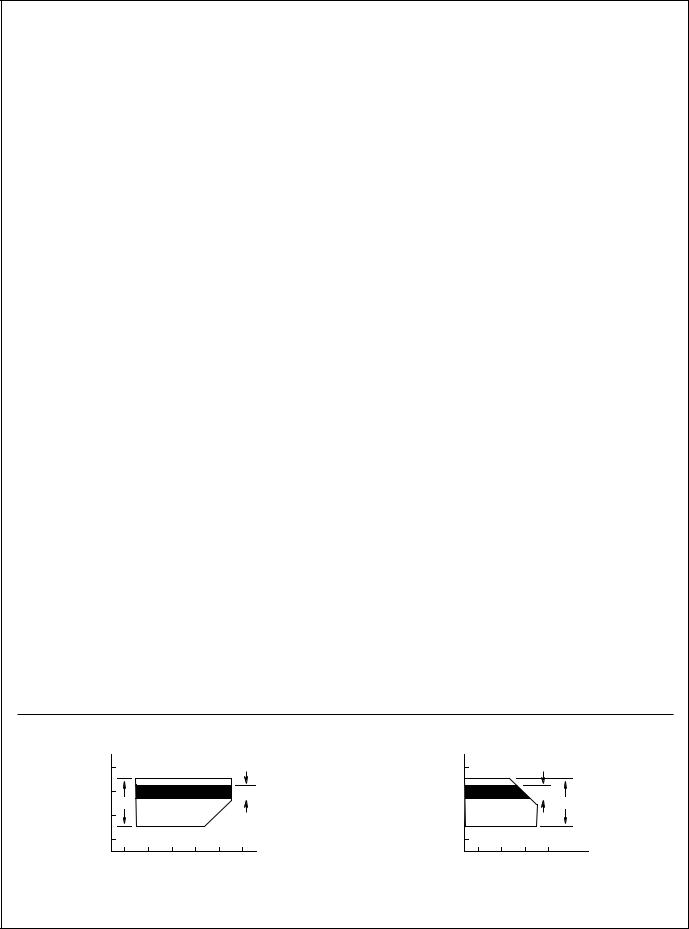

Recommended Operating Area as a Function of Supply Voltages

|

8 |

|

|

|

|

|

|

(V) |

6 |

|

|

|

|

|

|

GND |

|

HC |

|

|

|

|

HCT |

4 |

|

|

|

|

|

||

- |

|

|

|

|

|

|

|

CC |

2 |

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

2 |

4 |

6 |

8 |

10 |

12 |

|

0 |

||||||

|

|

|

VCC - VEE (V) |

|

|

||

|

8 |

|

|

|

|

(V) |

6 |

|

|

|

|

GND |

|

|

|

HCT |

HC |

4 |

|

|

|

||

- |

|

|

|

|

|

CC |

2 |

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

-2 |

-4 |

-6 |

-8 |

|

0 |

||||

|

|

|

VEE - GND (V) |

||

FIGURE 1. |

FIGURE 2. |

6

’HC4051, ’HCT4051, ’HC4052, CD74HCT4052, ’HC4053, CD74HCT4053

DC Electrical Specifications

|

|

TEST CONDITIONS |

|

|

AMBIENT TEMPERATURE, TA |

|

|

|

|||||||

|

|

VIS |

VI |

VEE |

VCC |

|

25oC |

|

-40oC - 85oC |

-55oC - 125oC |

|

|

|||

|

PARAMETER |

(V) |

(V) |

(V) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

High Level Input Voltage, |

|

|

|

2 |

1.5 |

- |

- |

1.5 |

- |

1.5 |

- |

V |

|||

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

0 |

V |

||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Low Level Input Voltage, |

|

|

|

2 |

- |

- |

0.5 |

- |

0.5 |

- |

0.5 |

V |

|||

VIL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On Resistance, rON |

VCC or VEE |

VIL or |

0 |

4.5 |

- |

70 |

160 |

- |

200 |

- |

240 |

Ω |

|

||

IO = 1mA, (Figure 11) |

|

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

6 |

- |

60 |

140 |

- |

175 |

- |

210 |

Ω |

|

||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-4.5 |

4.5 |

- |

40 |

120 |

- |

150 |

- |

180 |

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC to VEE |

|

0 |

4.5 |

- |

90 |

180 |

- |

225 |

- |

270 |

Ω |

|

|

|

|

|

|

0 |

6 |

- |

80 |

160 |

- |

200 |

- |

240 |

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-4.5 |

4.5 |

- |

45 |

130 |

- |

162 |

- |

195 |

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Maximum On Resistance |

|

|

0 |

4.5 |

- |

10 |

- |

- |

- |

- |

- |

Ω |

|

||

Between any Two |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

6 |

- |

8.5 |

- |

- |

- |

- |

- |

Ω |

|

|||

Channels, ∆ rON |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

-4.5 |

4.5 |

- |

5 |

- |

- |

- |

- |

- |

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Switch On/Off Leakage |

For Switch Off: |

VIL or |

|

|

|

|

|

|

|

|

|

|

|

|

|

Current, IIZ |

When VIS = VCC, |

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOS = VEE; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 and 2 Channels |

|

0 |

6 |

- |

- |

± 0.1 |

- |

± |

1 |

- |

± 1 |

µ |

A |

|

|

When VIS = VEE, |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4053 |

VOS = VCC |

|

-5 |

5 |

- |

- |

± 0.1 |

- |

± |

1 |

- |

± 1 |

µ |

A |

|

|

|

For Switch On: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 Channels |

|

0 |

6 |

- |

- |

± 0.1 |

- |

± |

1 |

- |

± 1 |

µ |

A |

|

|

All Applicable |

|

|||||||||||||

|

|

Combinations of |

|

|

|

|

|

|

|

|

|

|

|

|

|

4052 |

|

-5 |

5 |

- |

- |

± 0.2 |

- |

± |

2 |

- |

± 2 |

µ |

A |

||

VIS and VOS |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

± 0.2 |

|

± |

|

|

± 2 |

µ |

|

|

|

8 Channels |

Voltage Levels |

|

0 |

6 |

- |

- |

- |

2 |

- |

A |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4051 |

|

|

-5 |

5 |

- |

- |

± 0.4 |

- |

± |

4 |

- |

± 4 |

µ |

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Control Input Leakage |

|

VCC or |

0 |

6 |

- |

- |

± 0.1 |

- |

± |

1 |

- |

± 1 |

µ |

A |

|

Current, IIL |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

Quiescent Device |

When VIS = VEE, |

VCC or |

0 |

6 |

- |

- |

8 |

- |

80 |

- |

160 |

µ |

A |

||

Current, ICC |

VOS = VCC |

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

IO = 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

When VIS = VCC, |

|

-5 |

5 |

- |

- |

16 |

- |

160 |

- |

320 |

µ |

A |

|||

|

|

VOS = VEE |

|

|

|

|

|

|

|

|

|

|

|

|

|

7

Loading...

Loading...