SANYO LC35W1000BTS-70U, LC35W1000BTS-10U Datasheet

Ordering number : ENN*6624

CMOS IC

LC35W1000BM, BTS-70U/10U

Asynchronous Silicon Gate 1M (131,072 words × 8 bits) SRAM

Preliminary

Overview

The LC35W1000BM and LC35W1000BTS-70U/10U are asynchronous silicon gate CMOS static RAM devices with a 131,072-word by 8-bit structure. They provide two chip enable pins (CE1 and CE2) for device select/deselect control and one output enable pin (OE) for output control. They feature high speed, low power, and a wide operating temperature range.This makes them optimal for use in systems that require high speed, low power, and battery backup. They also support easy memory expansion.

Features

•Low-voltage operation: 2.7 to 3.6 V

•Wide operating temperature range: –40 to +85°C

•Access time:

70 ns (maximum):

LC35W1000BM and LC35W1000BTS-70U. 100 ns (maximum):

LC35W1000BM and LC35W1000BTS-10U.

•Low current drain

Standby mode: 0.1 µA (typical*) at Ta = +25°C 10.0 µA (maximum) at Ta = –40 to +70°C

20.0 µA (maximum) at Ta = –40 to +85°C

•Data retention voltage: 2.0 to 3.6 V

•No clock required (fully static circuits)

•Input/output shared function pins, 3-state output pins

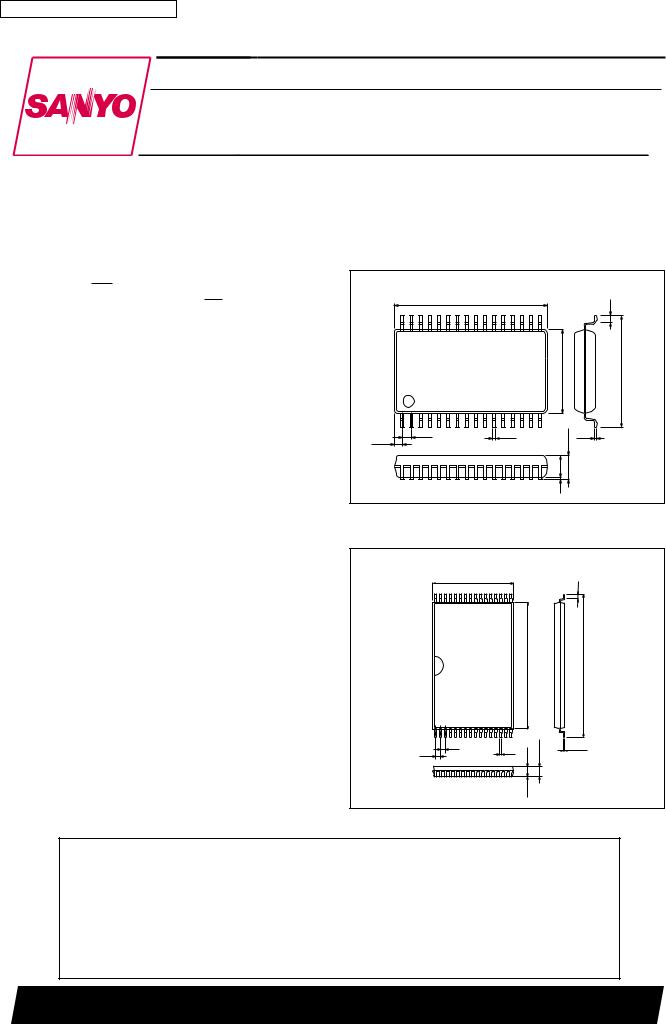

•Package

32-pin SOP (525 mil) plastic package:

LC35W1000BM

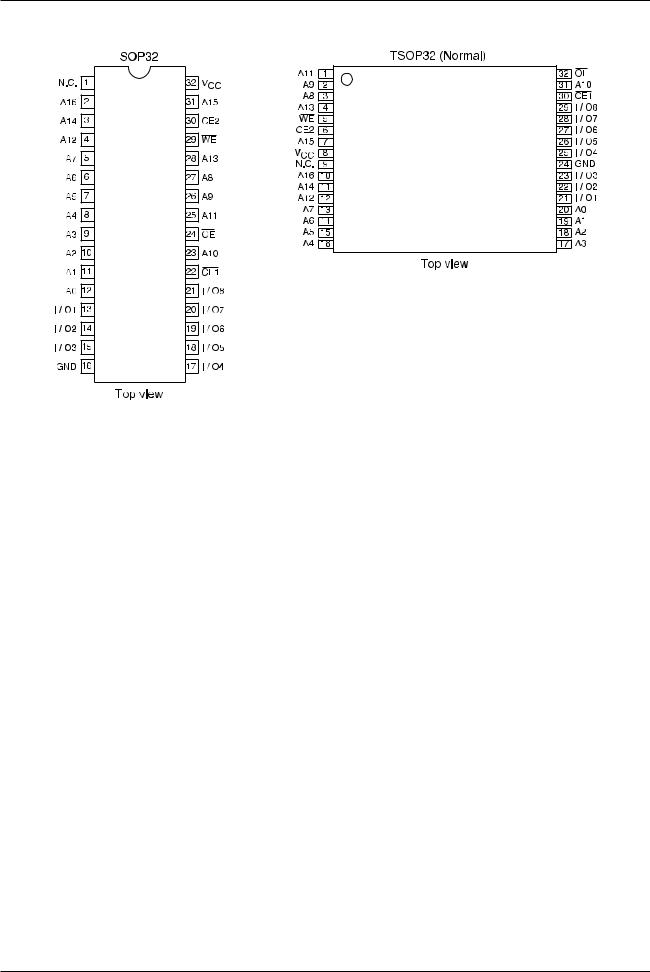

32-pin TSOP (8 × 14 mm) plastic package (Normal): LC35W1000BTS

Package Dimensions

unit: mm

3205A-SOP32 |

|

|

|

|

|

[LC35W1000BM-70U/10U] |

|

||

|

20.5 |

|

|

0.8 |

32 |

|

17 |

|

|

|

|

|

||

|

|

|

11.2 |

14.0 |

1 |

0.4 |

16 |

3.1max |

0.15 |

1.27 |

||||

(0.73) |

|

|

|

|

|

|

|

|

|

|

|

|

(2.7) |

|

|

|

|

0.2 |

SANYO: SOP32 |

|

|

|

|

|

unit: mm

3228A-TSOP32DA

[LC35W1000BTS-70U/10U]

|

8.0 |

0.5 |

|

32 |

17 |

||

|

12.4 |

14.0 |

1 |

0.5 |

16 |

|

1.2max |

0.125 |

|

(0.25) |

(1.0) |

|||||

0.2 |

||||||

|

|

|||||

|

|

|

|

0.08 |

SANYO: TSOP32DA |

|

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft’s control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft’s control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

41902RM (OT) No. 6624-1/9

LC35W1000BM, BTS-70U/10U

Pin Assignment

A13488

A13487

No. 6624-2/9

LC35W1000BM, BTS-70U/10U

Block Diagram

|

Address buffer |

|

Raw Decoder |

|

|

|

|

||

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Output

buffer

Input data buffer

Memory cell array

Data control circuit

Control

circuit

Pin Functions

A0 to A16 |

Address input |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ready/write control input |

|

|

|

WE |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Output enable input |

||

|

|

|

OE |

|

|||

|

|

|

|

|

|

|

|

|

Chip enable input |

||||||

|

CE, |

CE2 |

|||||

|

|

|

|

|

|

|

|

I/O1 to I/O8 |

Data I/O |

||||||

|

|

|

|

|

|

|

|

VCC, GND |

Power supply, ground |

||||||

Function Table

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode |

|

CE1 |

CE2 |

|

OE |

|

WE |

I/O |

Supply current |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Ready cycle |

|

L |

H |

|

L |

|

H |

Data output |

ICCA |

|||

Write cycle |

|

L |

H |

|

X |

|

L |

Data input |

ICCA |

|||

Output disable |

|

L |

H |

|

H |

|

H |

High impedance |

ICCA |

|||

Unselected |

|

H |

X |

|

X |

|

X |

High impedance |

ICCS |

|||

|

X |

L |

|

X |

|

X |

High impedance |

ICCS |

||||

|

|

|

|

|||||||||

Note: X indicates H or L. |

|

|

|

|

|

|

|

|

|

|||

Specifications

Maximum Ratings at Ta = 25°C

Parameter |

Symbol |

Conditions |

Ratings |

Unit |

|

|

|

|

|

Maximum supply voltage |

VCC max |

|

4.6 |

V |

Input pin voltage |

VIN |

|

–0.3* to VCC + 0.3 |

V |

I/O pin voltage |

VI/O |

|

–0.3 to VCC + 0.3 |

V |

Operating temperature |

Topr |

|

–40 to +85 |

°C |

|

|

|

|

|

Storage temperature |

Tstg |

|

–55 to +125 |

°C |

*: For pulse widths under 30 ns: –2.0 V

Note: This chip may be destroyed if any stress in excess of the absolute maximum ratings is applied.

No. 6624-3/9

Loading...

Loading...