SANYO LC72366, LC72362N, LC72358N Datasheet

Ordering number : EN5065A

CMOS LSI

LC72358N, 72362N, 72366

Single-Chip PLL Microcontrollers

Overview

The LC72358N, LC72362N, and LC72366 are 1.33 µs instruction execution time single-chip microcontrollers for electronic tuning applications. These products incorporate a high-speed locking circuit and a high-performance direct PLL circuit that can control the local oscillator C/N characteristics. These products have 256 or 512 bytes of RAM and 16K, 24K or 32K bytes of program ROM on chip, and incorporate a three-channel serial I/O interface, a six-channel A/D converter and other interfaces.

Features

•ROM

—LC72358N: 8K steps (8191 × 16 bits)

—LC72362N: 12K steps (12287 × 16 bits)

—LC72366: 16K steps (16383 × 16 bits)

The subroutine area in both products is 4K steps (4095 × 16 bits).

•RAM

—LC72358N, 72362N: 512 × 4 bits (banks 0 to 7)

—LC72366: 1K × 4 bits (banks 0 to F)

•Stack: Eight levels

•Serial I/O: Three channels (8-bit 3-wire format)

There are three internal serial clocks: 12.5 kHz,

37.5kHz and 187.5 kHz.

•External interrupts:

Two channels (the INT0 and INT1 pins)

Switching between rising and falling edge detection is supported.

•Internal interrupts: Three channels

—Two internal timer interrupt channels

The timers provide eight interrupt periods: 100 µs,

1ms, 2 ms, 5 ms, 10 ms, 50 ms, 125 ms and 250 ms.

—One serial I/O interrupt channel

•Multiple interrupt levels: Four levels

Hardware priority order

INT0 pin > INT1 pin > SI/O pin > internal timer 0 > internal timer 1

•A/D converter: Six channels (6-bit successive approx-

imation type)

•General-purpose ports

— Input ports: 10

—Output ports: 28

—I/O ports: 25 (These pins can be switched between

input and output in bit units.)

•PLL block

—Built-in sub-charge pump for high-speed locking

—Support for dead zone control

—Built-in unlock detection circuit

—Twelve reference frequencies: 1, 3, 3.125, 5, 6.25, 9, 10, 12.5, 25, 30, 50 and 100 kHz

•Universal counter: 20 bits

Supports frequency and period measurement with counting periods of 1, 4, 8 and 32 ms.

• Timers: Timer interrupt periods

100 µs, 1 ms, 2 ms, 5 ms, 10 ms, 50 ms, 125 ms and 250 ms

•Beep: Six frequencies: 2.08 kHz, 2.25 kHz, 2.5 kHz,

3.0kHz, 3.75 kHz, 4.17 kHz.

•Reset: Built-in voltage detection type reset circuit

•Cycle time: 1.33 µs (all instructions execute in one

cycle)

• Halt mode: The microcontroller operating clock is stopped in halt mode.

There are four types of event that clear halt mode: interrupt requests, timer FF overflows, key inputs, and hold pin inputs.

• Operating supply voltage: 4.5 to 5.5 V (3.5 to 5.5 V when only the controller block operates)

•Package: QFP80E (QIP80E)

•OTP version: LC72P366

•Development tools: Emulator .................RE32N

Evaluation chip.......LC72EV350 Evaluation chip board

................................EB-72EV350

This LSI can easily use CCB that is SANYO’s original bus format.

•CCB is a trademark of SANYO ELECTRIC CO., LTD.

•CCB is SANYO’s original bus format and all the bus addresses are controlled by SANYO.

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

63096HA (OT)/62295TH (OT) No. 5065-1/13

LC72358N, 72362N, 72366

Package Dimensions

unit: mm

3174-QFP80E

[LC72358N, 72362N, 72366]

SANYO: QIP80E

Pin

No. 5065-2/13

LC72358N, 72362N, 72366

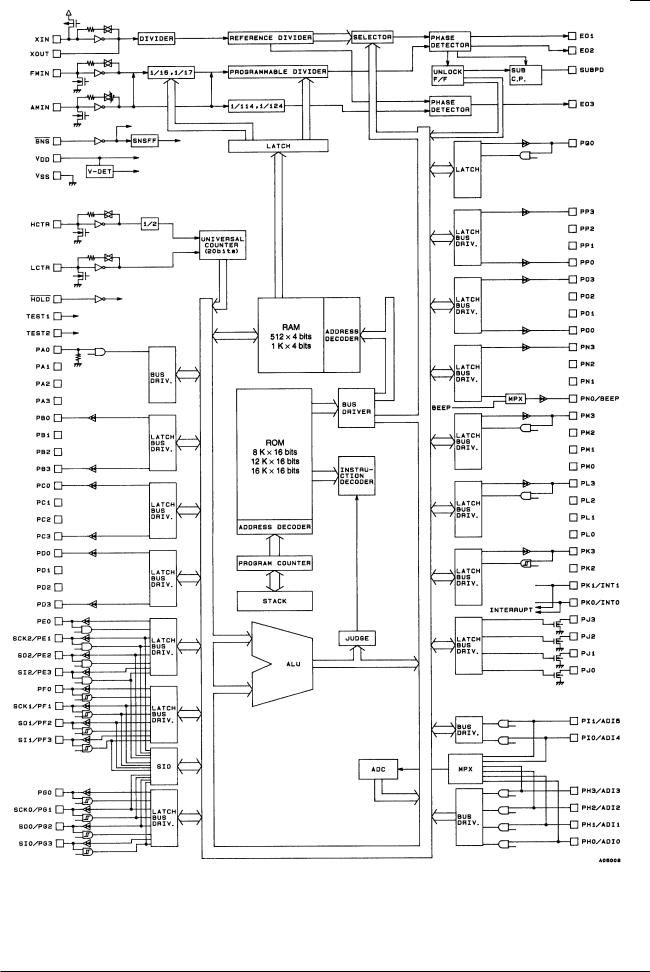

Block Diagram

No. 5065-3/13

LC72358N, 72362N, 72366

Specifications

Absolute Maximum Ratings at Ta = 25°C, VSS = 0 V

Parameter |

Symbol |

Conditions |

Ratings |

Unit |

|

|

|

|

|

|

|

Maximum supply voltage |

VDD max |

|

–0.3 to +6.5 |

V |

|

Input voltage |

VIN |

All input pins |

–0.3 to VDD + 0.3 |

V |

|

Output voltage |

VOUT (1) |

J port |

–0.3 to +15 |

V |

|

VOUT (2) |

All output ports other than VOUT (1) |

–0.3 to VDD + 0.3 |

V |

||

|

|||||

|

IOUT (1) |

J port |

0 to 5 |

mA |

|

Output current |

IOUT (2) |

D, E, F, G, K, L, M, N, O, P and Q ports, |

0 to 3 |

mA |

|

EO1, EO2, EO3, SUBPD |

|||||

|

|

|

|

||

|

|

|

|

|

|

|

IOUT (3) |

B and C ports |

0 to 1 |

mA |

|

Allowable power dissipation |

Pd max |

Ta = –40 to +85°C |

400 |

mW |

|

|

|

|

|

|

|

Operating temperature |

Topr |

|

–40 to +85 |

°C |

|

|

|

|

|

|

|

Storage temperature |

Tstg |

|

–45 to +125 |

°C |

|

|

|

|

|

|

Allowable Operating Ranges at Ta = –40 to +85°C, VDD = 3.5 to 5.5 V

Parameter |

Symbol |

|

|

|

|

|

Conditions |

min |

typ |

max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD (1) |

CPU and PLL operating |

4.5 |

5.0 |

5.5 |

V |

|||||

Supply voltage |

VDD (2) |

CPU operating |

3.5 |

|

5.5 |

V |

|||||

|

VDD (3) |

Memory retention |

1.3 |

|

5.5 |

V |

|||||

|

VIH (1) |

E, H, I, L, M and Q ports, HCTR and LCTR |

0.7 VDD |

|

VDD |

V |

|||||

|

(when selected for input) |

|

|||||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Input high level voltage |

VIH (2) |

F, G and K ports, LCTR (period measurement mode), |

0.8 VDD |

|

VDD |

V |

|||||

HOLD |

|

||||||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH (3) |

|

|

|

|

|

|

2.5 |

|

VDD |

V |

|

SNS |

|

|||||||||

|

VIH (4) |

A port |

0.6 VDD |

|

VDD |

V |

|||||

|

VIL (1) |

E, H, I, L, M and Q ports, HCTR and LCTR |

0 |

|

0.3 VDD |

V |

|||||

|

(when selected for input) |

|

|||||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Input low level voltage |

VIL (2) |

A, F, G and K ports, LCTR (period measurement mode) |

0 |

|

0.2 VDD |

V |

|||||

|

VIL (3) |

|

0 |

|

1.3 |

V |

|||||

|

|

SNS |

|

|

|||||||

|

VIL (4) |

|

|

0 |

|

0.4 VDD |

V |

||||

|

|

HOLD |

|

|

|||||||

|

fIN (1) |

XIN |

4.0 |

4.5 |

5.0 |

MHz |

|||||

|

fIN (2) |

FMIN: VIN (2), VDD (1) |

10 |

|

150 |

MHz |

|||||

|

fIN (3) |

FMIN: VIN (3), VDD (1) |

10 |

|

130 |

MHz |

|||||

Input frequency |

fIN (4) |

AMIN (H): VIN (3), VDD (1) |

2.0 |

|

40 |

MHz |

|||||

fIN (5) |

AMIN (L): VIN (3), VDD (1) |

0.5 |

|

10 |

MHz |

||||||

|

|

||||||||||

|

fIN (6) |

HCTR: VIN (3), VDD (1) |

0.4 |

|

12 |

MHz |

|||||

|

fIN (7) |

LCTR: VIN (3), VDD (1) |

100 |

|

500 |

kHz |

|||||

|

fIN (8) |

LCTR (period measurement): VIH (2), VIL (2), VDD (1) |

1 |

|

20 × 103 |

Hz |

|||||

|

VIN (1) |

XIN |

0.5 |

|

1.5 |

Vrms |

|||||

Input amplitude |

VIN (2) |

FMIN |

0.10 |

|

1.5 |

Vrms |

|||||

|

VIN (3) |

FMIN, AMIN, HCTR, LCTR |

0.07 |

|

1.5 |

Vrms |

|||||

Input voltage range |

VIN (4) |

ADI0 to ADI5 |

0 |

|

VDD |

V |

|||||

No. 5065-4/13

Loading...

Loading...