SANYO LC371100SM-10LV, LC371100ST-20LV, LC371100ST-10LV, LC371100SP-20LV, LC371100SP-10LV Datasheet

...

Ordering number : EN*5087C

CMOS LSI

LC371100SP, SM, ST-10/20LV

1 MEG (131072 words× 8 bits) Mask ROM

Internal Clocked Silicon Gate

Preliminary

Overview

The LC371100SP, LC371100SM and LC371100ST are 131,072-word × 8-bit organization (1,048,576-bit) mask programmable read only memories.

The LC371100SP-10, LC371100SM-10 and LC371100ST-10 feature an access time of 100 ns, an OE access time of 40 ns, and a standby current of 30 µA, and are optimal for use in 5-V systems that require high-speed access.

The LC371100SP-20LV, LC371100SM-20LV and LC371100ST-20LV feature an access time of 200 ns, an OE access time of 80 ns, and a standby current of 4 µA. Additionally, they provide high-speed access in 3.3-V systems (3.0 to 3.6 V) with a 150-ns access time and a 60ns OE access time.

These ROMs adopt the JEDEC standard pin assignment which allows them to replace EPROM easily. To prevent bus line collisions in multi-bus microcontroller systems, pin 24 can be mask programmed to be either active high or active low.

Features

•131072 words × 8 bits organization

•Power supply

LC371100SP, SM, ST-10: |

5.0 V ± 10% |

LC371100SP, SM, ST-20LV: |

2.7 to 3.6 V |

• Fast access time (tAA, tCA) |

|

LC371100SP, SM, ST-10: |

100 ns (max.) |

LC371100SP, SM, ST-20LV: |

200 ns (max.) |

|

150 ns (VCC = 3.0 to 3.6 V) |

• Operating current |

|

LC371100SP, SM, ST-10: |

70 mA (max.) |

LC371100SP, SM, ST-20LV: |

20 mA (max.) |

• Standby current |

|

LC371100SP, SM, ST-10: |

30 µA (max.) |

LC371100SP, SM, ST-20LV: |

5 µA (max.) |

•Full static operation (internal clocked type)

•Fully TTL compatible (5 V supply)

•3 state outputs

•JEDEC standard pin configuration

•Package type

LC371100SP-10/20LV: DIP32 (600 mil) LC371100SM-10/20LV:SOP32 (525 mil) LC371100ST-10/20LV: TSOP32 (8 mm × 20 mm)

Package Dimensions

unit: mm

3192-DIP32

[LC371100SP]

SANYO: DIP32

unit: mm

3205-SOP32

[LC371100SM]

SANYO: SOP32

unit: mm

3224-TSOP32

[LC371100ST]

SANYO: TSOP32 (type-I)

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

43098HA (OT)/51195TH (OT)/41095TH (OT) No. 5087-1/5

LC371100SP, SM, ST-10/20LV

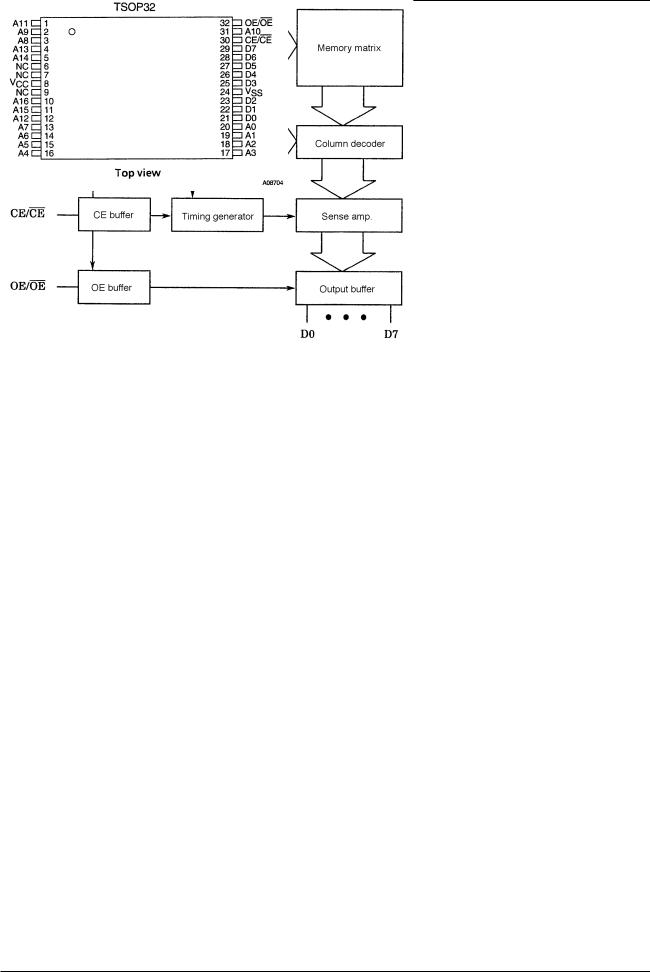

Pin Assignments |

Pin Functions |

|

||

|

|

|

|

|

|

A0 to A16 |

Address input |

||

|

|

|

|

|

|

D0 to D7 |

Data output |

||

|

|

|

|

|

|

|

|

|

|

|

CE/CE |

Chip enable input |

||

|

|

|

|

|

|

|

|

|

|

|

OE/OE |

Output enable input |

||

|

|

|

|

|

|

VCC |

Power supply |

||

|

VSS |

Ground |

||

Block Diagram

Truth Table

|

|

|

|

|

|

|

|

CE/CE |

OE/OE |

Output |

Current drain |

||||

L/H |

X |

High-impedance |

Standby mode |

||||

|

|

|

|

|

|

|

|

H/L |

L/H |

High-impedance |

Operating mode |

||||

|

|

|

|

|

|

|

|

H/L |

H/L |

DOUT |

Operating mode |

||||

X: H or L level should be offered.

No. 5087-2/5

Loading...

Loading...